【導(dǎo)讀】10nm預(yù)計(jì)將會是一個(gè)高產(chǎn)能與長使用壽命的技術(shù)節(jié)點(diǎn)。臺積電和三星都計(jì)劃在2015年第4季投產(chǎn)10nm設(shè)計(jì),所瞄準(zhǔn)的客戶顯然就是Apple。如果能夠在2016年或甚至在2017年中旨以前量產(chǎn)10nm,那么16/14nm將會是一個(gè)“短命”的技術(shù)節(jié)點(diǎn)。

半導(dǎo)體供應(yīng)鏈正面臨越來越多的挑戰(zhàn),但10nm節(jié)點(diǎn)將有更大的機(jī)會能夠從新技術(shù)工藝的微縮中獲得更大的好處。

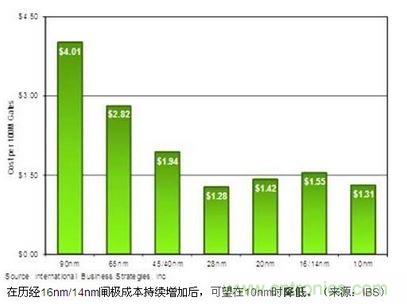

根據(jù)國際商業(yè)策略(IBS)的分析預(yù)計(jì),20nm和16/14nm工藝的閘極成本將會比上一代技術(shù)更高。而針對10nm閘極成本的分析則顯現(xiàn)出不同的模式,如下圖所示。

在歷經(jīng)16nm/14nm閘極成本持續(xù)增加后,可望在10nm時(shí)降低。(來源:IBS)

雖然IBS并未預(yù)期工藝技術(shù)停止微縮,但預(yù)計(jì)試錯成本(cost penalty)將出現(xiàn)在采用20nm bulk CMOS HKMG和16/14nm FinFET之際。對于閘極成本的這些項(xiàng)測已經(jīng)證實(shí)是正確的,而當(dāng)蘋果(Apple)的20nm產(chǎn)品量產(chǎn)時(shí),20nm芯片產(chǎn)能比起28nm時(shí)更低得多了。

臺積電(TSMC)提供了另一個(gè)例子。該公司的28nm芯片月產(chǎn)能(WPM)達(dá)15萬片,但其20nm芯片月產(chǎn)能大約將近三分之一——60,000WPM。Globalfoundries在其紐約州馬爾它(Malta)晶圓廠也擁有20nm產(chǎn)能,但該廠的主要著重于FinFET。至于三星電子(Samsung Electronics)和聯(lián)電(UMC),他們決定直接跳過20nm。

隨著16/14nm晶圓量產(chǎn),同樣地,16/14nm的晶圓產(chǎn)能又比28nm時(shí)更低。16/14nm的晶圓產(chǎn)量同樣是由Apple驅(qū)動的,但利用16/14nm技術(shù)的時(shí)間長短則將由10nm工藝多快出現(xiàn)所決定。

相較于晶圓成本增加,10nm時(shí)的閘極成本將會降低,這是因?yàn)樵摴に噷哂懈叩拈l極密度。為了可在10nm時(shí)取得更低的閘極成本,勢必需要具備較高的系統(tǒng)與參數(shù)良率,但這并不難實(shí)現(xiàn)。

10nm預(yù)計(jì)將會是一個(gè)高產(chǎn)能與長使用壽命的技術(shù)節(jié)點(diǎn)。臺積電和三星都計(jì)劃在2015年第4季投產(chǎn)10nm設(shè)計(jì),所瞄準(zhǔn)的客戶顯然就是Apple。如果能夠在2016年或甚至在2017年中旨以前量產(chǎn)10nm,那么16/14nm將會是一個(gè)“短命”的技術(shù)節(jié)點(diǎn)。

然而,10nm所需的資本支出大約為20億美元,可實(shí)現(xiàn)10,000 WPM的產(chǎn)能;如果要達(dá)到40,000 WPM產(chǎn)能,那么晶圓廠將耗資80億美元。此外,實(shí)現(xiàn)10nm的設(shè)計(jì)至少需要1.5億美元的最低成本,因此,如果芯片營收必須比設(shè)計(jì)成本更高10倍才能取得不錯的投資報(bào)酬率,那么,10nm芯片就必須達(dá)到15億美元的銷售數(shù)字。

在10nm節(jié)點(diǎn)以后,可能必須使用超紫外光微影(EUV)技術(shù),而且必須在提升EUV吞吐量方面穩(wěn)定進(jìn)步。盡管450mm晶圓技術(shù)持續(xù)進(jìn)展,但預(yù)計(jì)要到2020年以前才可能開始導(dǎo)入。