【導(dǎo)讀】本文分享的是一款完整的線性可變差分變壓器(LVDT)信號調(diào)理電路,可精確測量距離機(jī)械參考點的線性位置或線性位移。模擬域中的同步解調(diào)用于提取位置信息并抑制外部噪聲。24位、Σ-Δ模數(shù)轉(zhuǎn)換器(ADC)可數(shù)字化位置輸出信息,以實現(xiàn)高精度。

電路功能與優(yōu)勢

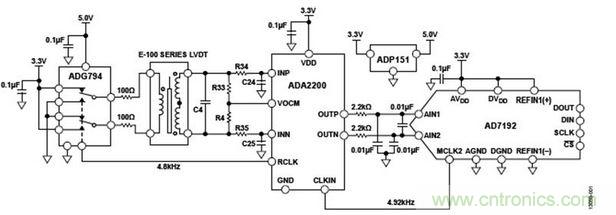

圖1所示電路是一款完整的線性可變差分變壓器(LVDT)信號調(diào)理電路,可精確測量距離機(jī)械參考點的線性位置或線性位移。模擬域中的同步解調(diào)用于提取位置信息并抑制外部噪聲。24位、Σ-Δ模數(shù)轉(zhuǎn)換器(ADC)可數(shù)字化位置輸出信息,以實現(xiàn)高精度。

LVDT在活動核心和線圈組件之間采用電磁耦合。這種非接觸式(因而是無摩擦的)工作方式是它們廣泛用于航空航天、過程控制、機(jī)器人、核、化學(xué)工廠、液壓、動力渦輪以及其他惡劣工作環(huán)境和要求具備長工作壽命與高可靠性應(yīng)用的主要原因。

包括LVDT激勵信號在內(nèi)的整個電路功耗僅為10 mW。電路激勵頻率和輸出數(shù)據(jù)速率均為SPI可編程。 該系統(tǒng)允許在可編程帶寬和動態(tài)范圍之間進(jìn)行權(quán)衡取舍,支持1 kHz以上的帶寬,且在20 Hz帶寬時具有100 dB動態(tài)范圍,是精密工業(yè)位置和計量應(yīng)用的理想之選。

圖1. LVDT信號調(diào)理電路(原理示意圖: 未顯示所有連接和去耦)

電路描述

ADA2200同步解調(diào)器可在信號解調(diào)至與LVDT核心位移成比例的低頻輸出電壓之前對LVDT次級信號進(jìn)行濾波,從而提取位置信息。ADA2200驅(qū)動AD7192 24位Σ-Δ型ADC,后者對輸出進(jìn)行數(shù)字化和濾波處理。ADA2200產(chǎn)生同步LVDT激勵信號,而ADG794開關(guān)將CMOS電平激勵信號轉(zhuǎn)換為精密3.3 V方波信號,驅(qū)動LVDT初級繞組。

LVDT是絕對位移傳感器,可將線性位移轉(zhuǎn)換為比例電信號。LVDT是特殊的繞線變壓器,具有活動核心,其位置與待測位置貼合。激勵信號施加于初級繞組。隨著核心的移動,次級繞組上的電壓成比例發(fā)生變化;根據(jù)該電壓即可計算位置。

LVDT的類型有很多,此外提取位置信息的方法也各不相同。圖1中的電路采用4線模式LVDT。將兩個LVDT的次級輸出相連使其電壓相反,從而執(zhí)行減法。當(dāng)LVDT核心位于零點位置時,這兩個次級端上的電壓相等,兩個繞組上的電壓差為零。隨著核心從零點位置開始移動,次級繞組上的電壓差也隨之增加。LVDT輸出電壓相位根據(jù)方向而改變。

該電路的主時鐘由AD7192 ADC產(chǎn)生。ADA2200接受主時鐘并產(chǎn)生其內(nèi)部所有時鐘,包括用作LVDT激勵信號的參考時鐘。ADA2200上的時鐘分頻器配置為產(chǎn)生4.8 kHz激勵信號。ADG794將激勵信號轉(zhuǎn)換為精密±3.3 V方波信號,該+3.3V來自于ADC電源電壓。3.3 V電源也用作ADC基準(zhǔn)電壓;因此,激勵信號與ADC基準(zhǔn)電壓之間的比例關(guān)系可以改善電路的噪聲性能和穩(wěn)定性。系統(tǒng)的3.3 V電源由ADP151低壓差調(diào)節(jié)器提供;后者由5 V電源驅(qū)動。

LVDT次級繞組和ADA2200輸入之間的耦合電路用來限制信號帶寬,并調(diào)節(jié)RCLK和ADA2200輸入之間的相對相位。該電路配置為具有最大正交(相位 = 90°)響應(yīng)以及最小同相(相位 = 0°)響應(yīng)。這使得可以僅通過測量正交輸出就能確定位置,進(jìn)而使ADA2200輸出電壓對電路中相位的變化不甚敏感。 LVDT的溫度變化導(dǎo)致有效串聯(lián)電阻和電感發(fā)生改變,是相位變化的主要來源。

ADA2200輸出端的抗混疊濾波器保持ADC所支持的信號帶寬。AD7192內(nèi)部數(shù)字濾波器的輸出帶寬約等于0.27乘以輸出數(shù)據(jù)速率。為了將輸出帶寬保持在4.8 kHz最大輸出數(shù)據(jù)速率,輸出抗混疊濾波器的-3 dB轉(zhuǎn)折頻率可以設(shè)為2 kHz左右。對于要求較低輸出數(shù)據(jù)速率的系統(tǒng),可相應(yīng)降低抗混疊濾波器的轉(zhuǎn)折頻率。

集成式同步解調(diào)器

ADA2200集成式同步解調(diào)器組成電路核心。它采用獨特的電荷共享技術(shù)來執(zhí)行模擬域內(nèi)的離散式時間信號處理。ADA2200具有全差分信號路徑。它由高阻抗輸入緩沖器后接一個固定低通濾波器(FIR抽取濾波器)、一個可編程IIR濾波器、一個解調(diào)器和一個差分輸出緩沖器組成。它的輸入和輸出共模電壓等于1.65 V(3.3 V電源電壓的1/2)。

ADA2200接受來自AD7192 ADC的4.92 MHz時鐘信號,然后產(chǎn)生其內(nèi)部所有時鐘,以及用作LVDT激勵信號的4.8 kHz參考時鐘。ADA2200集成可配置時鐘分頻器,可編程支持很多不同的激勵頻率。

CMOS開關(guān)

選擇ADG794 CMOS開關(guān)是因為它具有低導(dǎo)通電阻、快速開關(guān)時間、先開后合式開關(guān)動作以及低成本等特點。

ADG794將ADA2200的低壓CMOS電平RCLK輸出轉(zhuǎn)換為低阻抗差分輸出方波源,然后驅(qū)動LVDT。為使開關(guān)留有裕量以便驅(qū)動正3.3 V信號,ADG794 VDD輸入采用5 V電源供電。

LVDT

圖1中的電路只需略作改動即可支持各種LVDT。Measurement Specialties, Inc. E-100 LVDT采用四線式模式,以便演示電路的主要特點。E-100沖程范圍為±2.54 mm,沖程端輸出靈敏度為240 mV/V,滿量程范圍最大線性度誤差為±0.5%,工作頻率范圍為100 Hz至10 kHz。完整詳情請參見E-Series LVDT數(shù)據(jù)手冊。

[page]

ADA2200輸入耦合網(wǎng)絡(luò)

可調(diào)諧ADA2200輸入耦合網(wǎng)絡(luò)以支持不同的LVDT。LVDT次級繞組電感和分流電容(C4)組成振蕩電路。 R4和R33電阻降低了振蕩電路的Q值,使該電路不易受LVDT繞組電感和電阻的變化影響,但功耗有所上升。R34/C24和R35/C25組成的RC濾波器對可降低信號帶寬,同時提供調(diào)節(jié)電路相對相位所需的額外自由度。ADA2200內(nèi)部相位敏感檢測器(PSD)的最大輸出發(fā)生在0°或180°相對相移處。

對于采用4.8 kHz方波激勵信號的E-100 LVDT而言,采用下列元件值可獲得最大輸出條件下的最優(yōu)相位:

● R4 = R33 = 2.2 kΩ

● R34 = R35 = 1 kΩ

● C24 = C25 = 3300 pF

● C4 = 0.01 μF

如需調(diào)諧該電路,則可通過放置LVDT核心以產(chǎn)生接近滿量程輸出信號的方式測量相位;然后,測量同相(I)和正交(Q)輸出信號。采用這些測量結(jié)果便可計算相對相位:

調(diào)節(jié)網(wǎng)絡(luò)元件,直到θREL絕對值低于約±3°;這樣可以改善電路對于LVDT電氣參數(shù)變化的靈敏度。

ADC選擇和同步

選擇AD7192 Σ-Δ型ADC,因為該器件支持可配置輸出數(shù)據(jù)速率,并具有各種不同的數(shù)字濾波器輸出選項,從而允許在帶寬和噪聲之間進(jìn)行權(quán)衡取舍。主時鐘輸出功能可輕松實現(xiàn)ADC采樣時鐘頻率與ADA2200輸出信號的鎖定。這對于優(yōu)化數(shù)字濾波器性能而言是必須的。由LVDT信號確定位置所需的數(shù)值是一次激勵時鐘周期的平均值。因此,當(dāng)AD7192輸出數(shù)據(jù)速率設(shè)為4.8 kHz時,即設(shè)為一個激勵時鐘周期時,可獲得所需的平均值。如果激勵時鐘周期和ADC采樣頻率未鎖定,則恢復(fù)的位置測量信息中包含錯誤。除以輸出數(shù)據(jù)速率便可有效求取多個激勵時鐘周期的平均值。

ADA2200輸出信號哪怕在LVDT核心位置固定的情況下亦含有電能,數(shù)值為激勵信號頻率的倍數(shù)。還可在頻率域中分析數(shù)字濾波器性能。AD7192具有sinc3或sinc4傳遞函數(shù),該傳遞函數(shù)在輸出數(shù)據(jù)速率的倍數(shù)處歸零。這些頻率分量是雜散誤差的來源。通過將ADC的輸出數(shù)據(jù)速率設(shè)為激勵信號頻率(或激勵頻率的約數(shù))便可抑制輸出雜散。如果激勵時鐘周期和ADC采樣頻率未鎖定,則雜散將不會落在傳遞函數(shù)的零點。

用于性能分析的用戶軟件

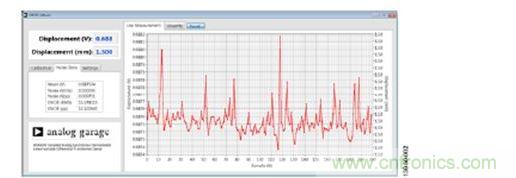

該電路支持圖形用戶界面,可方便地進(jìn)行板上的器件配置,并評估電路性能。該軟件的選項卡可執(zhí)行電路校準(zhǔn)和器件配置,以及顯示噪聲性能、線性度性能和實時位置測量。

圖2. 用戶軟件屏幕截圖

噪聲分析

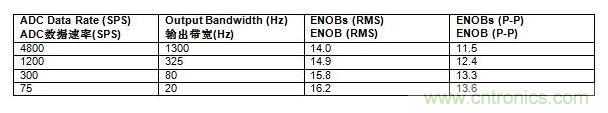

該電路的輸出噪聲是ADC輸出數(shù)據(jù)速率的函數(shù)。表1顯示數(shù)字化數(shù)據(jù)相對于ADC采樣速率的有效位數(shù)(ENOB),假設(shè)滿量程輸出電壓為2.5 V。該電路的噪聲性能與LVDT核心位置無關(guān)。

表1. 噪聲性能與帶寬的關(guān)系

如果ADA2200輸出噪聲與頻率無關(guān),則預(yù)計有效位數(shù)將在輸出數(shù)據(jù)速率每4次折疊下降時增加一位。 ENOB在較低輸出數(shù)據(jù)速率下的增加放緩是由于輸出驅(qū)動器的1/f噪聲所導(dǎo)致的;該噪聲在較低的輸出數(shù)據(jù)速率下成為噪底的主要成分。

[page]

線性度測試結(jié)果

首先在±2.0 mm核心位移處執(zhí)行一次兩點校準(zhǔn)即可測量線性度結(jié)果。由這兩次測量結(jié)果可確定斜率和失調(diào),從而實現(xiàn)預(yù)期直線擬合。 然后,在±2.5 mm滿量程范圍內(nèi)測量核心位移。從預(yù)期直線擬合數(shù)據(jù)中減去測量數(shù)據(jù)即可確定線性度誤差。

圖3. 位置線性度誤差與LVDT內(nèi)核位移的關(guān)系

測得的數(shù)據(jù)顯示電路性能優(yōu)于E-Series LVDT數(shù)據(jù)手冊中指定的線性度性能。

多LVDT同步工作

很多應(yīng)用都會近距離使用多個LVDT。若這些LVDT以相似的載波頻率運(yùn)行,雜散磁耦合可能導(dǎo)致拍頻。 產(chǎn)生的拍頻可能會影響這些條件下的測量精度。為避免這種情況,所有LVDT必須同步工作。

通過讓器件同時退出復(fù)位狀態(tài),可同步多個ADA2200器件。ADA2200在RST引腳解除置位之后的第一個CLKIN上升沿時退出復(fù)位模式。因此,從單一源驅(qū)動所有ADA2200 CLKIN引腳以及所有RESETB線路便足以確保器件同步工作。避免在CLKIN上升沿附近對RESETB解除置位,以防器件在不同時鐘沿上復(fù)位。 可監(jiān)控ADA2200器件的RCLK輸出,確保ADA2200器件正確同步。

常見變化

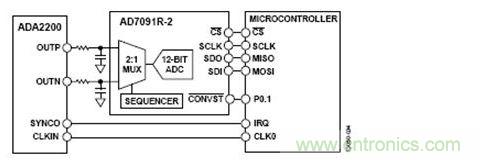

在某些系統(tǒng)中,可能需要使用SAR ADC,而非Σ-Δ型轉(zhuǎn)換器。 這些情況下,ADC轉(zhuǎn)換時鐘必須與ADA2200更新速率同步。 如前所述,ADA2200輸出會在激勵頻率的倍數(shù)處含有雜散。 這些雜散可通過移動平均濾波器或級聯(lián)多個移動平均濾波器加以抑制。 移動平均濾波器易于實現(xiàn),且具有出色的時域特性。 若要完全抑制雜散,則移動平均樣本大小必須等于8個樣本的整數(shù)倍。

圖4顯示了ADA2200連接至AD7091R-2,后者是一個超低功耗、雙通道、12位SAR ADC。 使用一個雙通道ADC,因而ADA2200的OUTP和OUTN輸出可順序采樣。 由于ADA2200輸出為分立式時間樣本,通過對兩個順序輸出樣本執(zhí)行減法操作(即VOUTP - VOUTN)便可實現(xiàn)差分測量。

圖4. 采用雙通道SAR ADC進(jìn)行差分采樣

SYNCO信號在每個ADA2200輸出采樣周期內(nèi)變?yōu)橛行АYNCO可用來中斷微控制器,以便獲取一對ADC樣本(對OUTP和OUTN采樣)。在上述示例中,采樣周期等于激勵時鐘頻率乘以8(或38.4 kHz);因此,ADC采樣速率為76.8 kSPS。

電路評估與測試

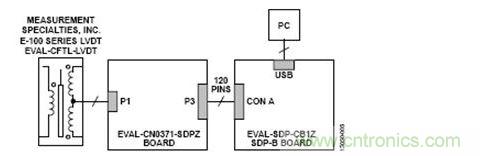

CN-0371電路使用EVAL-CN0371-SDPZ電路板和EVAL-SDP-CB1Z SDP-B控制器板。 這兩片板具有120引腳的對接連接器,可以快速完成設(shè)置并評估電路性能。 電路板包含待評估電路,SDP-B板配合CN-0371評估軟件使用,捕捉電路板數(shù)據(jù)。

設(shè)備要求

需要以下設(shè)備:

● 帶USB端口的Windows XP(32位)、Windows Vista 或Windows 7的PC

● EVAL-CN0371-SDPZ電路板

● EVAL-SDP-CB1Z SDP-B控制器板

● CN-0371評估軟件

● Measurement Specialties, Inc. E-100經(jīng)濟(jì)型LVDT (EVAL-CFTL-LVDT)

[page]

開始使用

下載CN0371.zip文件,然后運(yùn)行setup.exe文件。 默認(rèn)情況下,程序安裝在Analog Devices目錄下。 程序名稱為CN0371。

功能框圖

電路框圖參見圖5。 有關(guān)完整的電路原理圖請參見EVAL-CN0371-SDPZ-Schematic.pdf文件,該文件位于CN-0371設(shè)計支持包中。 用于電路板的5 V電源由USB總線通過SDP-B板的120引腳連接器提供。

圖5. 測試設(shè)置框圖

設(shè)置

將EVAL-CN0371-SDPZ電路板上的120引腳連接器連接到EVAL-SDP-CB1Z SDP-B板上的CON A連接器。 使用尼龍五金配件,通過120引腳連接器兩端的孔牢牢固定這兩片板。

測試

啟動評估軟件,并通過USB電纜將PC連接到SDP-B板上的微型USB連接器。

一旦USB通信建立,就可以使用SDP-B板來發(fā)送、接收和采集來自電路板的數(shù)據(jù)。

圖6顯示電路板連接SDP-B板的照片。 有關(guān)SDP-B板的信息請參閱UG-277用戶指南。

有關(guān)測試設(shè)置、校準(zhǔn)以及如何使用評估軟件來捕捉數(shù)據(jù)的詳細(xì)信息,請參閱CN-0371軟件用戶指南。

針對原型開發(fā)的連接

EVAL-CN0371-SDPZ電路板設(shè)計為搭配EVAL-SDP-CB1Z SDP-B板使用,但任何微處理器都可與AD7192的SPI接口實現(xiàn)對接。對于另一個搭配EVAL-CN0371-SDPZ電路板使用的控制器而言,第三方必須開發(fā)相應(yīng)軟件。

目前已有一些轉(zhuǎn)接板能實現(xiàn)與Altera或Xilinx現(xiàn)場可編程門陣列(FPGAs)的接口。 利用Nios驅(qū)動器,Altera的BeMicro SDK板能配合BeMicro SDK/SDP轉(zhuǎn)接板一同使用。任何集成FMC連接器的Xilinx評估板均可與FMC-SDP轉(zhuǎn)接板一同使用。

EVAL-CN0371-SDPZ還兼容Digilent、Imod接口規(guī)格。

圖6顯示系統(tǒng)測試設(shè)置的照片。

圖6. EVAL-CN0371-SDPZ電路板連接EVAL-SDP-CB1Z SDP-B板和LVDT(核心連接精密應(yīng)變計接頭)