【導讀】隨著CMOS技術(shù)的出現(xiàn)和進步,1982年推出了基于CMOS的浮點DSP芯片。AT&T;公司于1984年推出的DSP32是第一個高性能浮點 DSP。1990年推出了浮點DSP芯片MC96002。可見從80年代以來,DSP芯片的發(fā)展突飛猛進,逐漸決定電子產(chǎn)品的更新?lián)Q代。從運算速度看,DSP芯片關(guān)鍵的乘法器部件從40%降到5%以內(nèi),片內(nèi)RAM數(shù)量增加一級以上。引腳數(shù)量增加到200個以上,大大提高了芯片靈活性。

本文介紹了基于 TMS320C5416DSP芯片的音頻信號濾波系統(tǒng),結(jié)合音頻編解碼TLV320AIC23芯片,F(xiàn)LASH存儲器等實現(xiàn)語音錄放器硬件的設(shè)計;接著以 CCS環(huán)境下的C語言為軟件設(shè)計。將語音信號輸入后,經(jīng)AIC23進行采樣后保存在外擴存儲器中,再經(jīng)過DSP帶緩沖串口MCBSP 2讀入DSP,經(jīng)過FIR濾波器濾除信號中的噪聲,最后進行離散傅里葉快速變換。

1 硬件設(shè)計方案

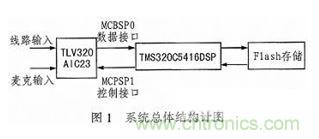

本系統(tǒng)采用DSP芯片TMS320C5416和TLV320AIC23音頻編解碼芯片實現(xiàn)系統(tǒng)的軟硬件設(shè)計,并在此基礎(chǔ)上完成語音信號的采集、播放、存儲、分析功能。文中包括3部分:音頻信號采集、DSP芯片處理信號、Flash存儲器。系統(tǒng)總體設(shè)計結(jié)構(gòu)如圖1所示。

TMS320C5416是文中采用的主芯片,是一款低功耗、高性能的DSP芯片,主要功能包括采集語音信號、存儲以及控制模塊間通信等,將音頻信號經(jīng)過采集和壓縮后存放到Flash存儲器中。AIC23的高性能立體聲信號的輸入支持MIC和LINE?IN兩種方式,可配置寄存器選擇,并且具有可編程增益調(diào)節(jié)。其內(nèi)部集成模數(shù)和數(shù)模轉(zhuǎn)換部件,采用先進的采樣技術(shù),采樣范圍在8K~96K之間。

本設(shè)計的從芯片TLV320AIC23音頻編解碼芯片,是立體聲音頻Codec芯片,主要負責對語音信號的A/D轉(zhuǎn)換,采樣編碼及濾波,該芯片是理想的音頻模擬器件,應用廣泛;DSP芯片三個中有兩個緩沖串口MCBSP0和MCBSP1負責控制音頻芯片AIC23,其中MCBSP0串口是SPI接口,實現(xiàn)語音數(shù)據(jù)的發(fā)送和接收,MCBSP1串口是I2S接口,任務(wù)是寫控制字;Flash存儲模塊可快速訪問可電擦寫,即使停電信息也不會丟失數(shù)據(jù)的存儲器,而且成本很低,可靠性高、穩(wěn)定性強,容量大有幾GB,外形小巧等特性,進行讀取和存儲操作為載體。

1.1 系統(tǒng)硬件電路設(shè)計

本系統(tǒng)采用的DSP芯片TMS320C5416,最高頻率可達160MIPS,系統(tǒng)實時性良好;音頻編解碼芯片TLV320AIC23采樣精度在16~32位。上述兩種芯片的結(jié)合是解決移動音頻錄放系統(tǒng)、現(xiàn)場采集語音的理想設(shè)計。TMS320C5416的3個MCBSP可以方便地實現(xiàn) AIC23之間的控制和通信。AIC23是可編程芯片,其內(nèi)部含有11個16位寄存器,由MODE引腳選擇控制接口采用SPI或者I2C哪種工作方式,MODE=0采用I2C模式;MODE=1表示采用SPI模式。

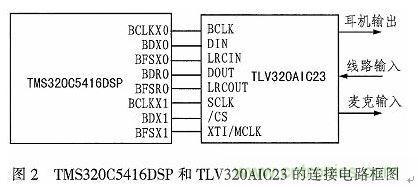

AIC23獨立的控制口接收控制器的命令字,而獨立的數(shù)據(jù)接口交換DSP語音數(shù)據(jù)。為DSP提供工作時鐘的是12M外部晶振。本系統(tǒng)C5416DSP的MCBSP0連接AIC23的控制接口,MCBS P1連接AIC23的數(shù)據(jù)接口。TMS320C5416DSP連接TLV320AIC23的接口框圖如圖2。

1.2 TMS320C5416DSP模塊設(shè)計

本次設(shè)計采用TMS320C5416芯片,其內(nèi)部128K*16的RAM,能有效提高系統(tǒng)的集成度和總體性能。另外它還有3個多通道緩沖串口,提供128個通道。C5416芯片的特點有:工作頻率可達160 MIPS;可以訪問的數(shù)據(jù)存儲空間64K、I/O空間64K。

TMS320C5416和TLV320AIC23連接的引腳如下:BCLKX0/1:傳輸時鐘信號,是多通道緩沖串行接口發(fā)送器的串行移位時鐘信號,復位時,默認為輸入。當OFF為低電平,BCLKX進入高組態(tài);TMS320C5416連接FLASH器件時,DSP芯片每次采集32位的語音數(shù)據(jù),依次從左聲道開始往右聲道寫入Flash器件進行存儲。

1.3 TLV320AIC23語音采集及回放接口電路模塊

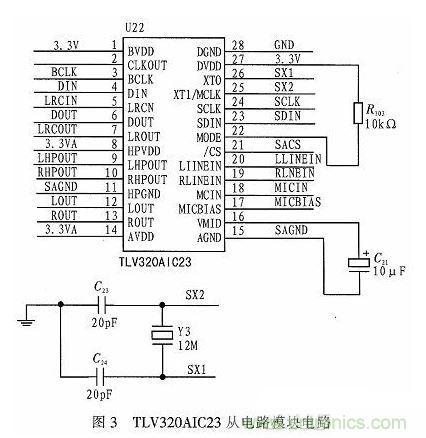

AIC23芯片內(nèi)部集成了ADC和DAC,兼容C5416的輸入/輸出電壓,它的數(shù)字接口和DSP的MCBSP端口無縫連接。AIC23采用先進的Sigma—delta過采樣技術(shù),將大部分的噪聲轉(zhuǎn)移到阻態(tài),采樣頻率范圍8K~96K提供4種16 bit、20 bit、24 bit和32 bit的采樣數(shù)據(jù),ADC和DAC的輸出信噪比分別達到90 dB和100 dB。

TLV320AIC23與TMS320C5416連接的引腳圖如下。BCLK:I2S數(shù)字音頻接口時鐘信號,串行數(shù)據(jù)傳輸時鐘,當主模式是AIC23時,由AIC23產(chǎn)生BCLK且由它傳輸給DSP,此時的頻率僅為主時鐘的1/4,當從模式時,DSP產(chǎn)生BCLK;DIN:I2S格式輸入給D/A轉(zhuǎn)換器;DOUT,立體聲ADC產(chǎn)生,I2S格式A/D轉(zhuǎn)換器串行數(shù)據(jù)輸出:LRCIN/LRCOUT:I2SD/A和A/D轉(zhuǎn)換器字時鐘信號,主機模式下,AIC23產(chǎn)生該信號發(fā)送給DSP,從機模式下,由DSP產(chǎn)生;SCLK:控制端口串行時鐘輸入;SDIN:控制端口串行數(shù)據(jù)輸入,控制協(xié)議,傳輸配置數(shù)據(jù);/CS:在SPI模式下,是數(shù)據(jù)鎖存控制端,在I2C模式下,作為外設(shè)7位地址的末位;XTI/MCLK:外部時鐘輸入。本文中AIC23由外接的晶振提供工作時鐘,TLV320AIC23從電路模塊電路如圖3。

1.4 語音數(shù)據(jù)存儲接口電路模塊

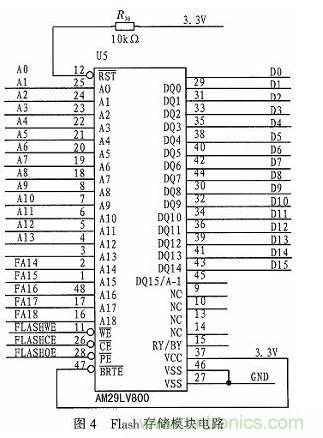

本文的語音數(shù)據(jù)存儲模塊采用32M*8位的Flash存儲空間,能夠滿足文中對存儲器芯片的容量以及讀取語音信號速度。Flash存儲器內(nèi)存放錄音和放音系統(tǒng)數(shù)據(jù)。Flash的構(gòu)成是由一組可獨立擦除的1KB區(qū)塊,擦除一個區(qū)塊將使該區(qū)塊全部復位為1。Flash存儲器每個區(qū)塊的基地址都固定不變。 Flash存儲器在存儲器中處于起始位置,一般從0開始。下圖4為Flash存儲模塊電路圖。

Flash存儲器是一種不揮發(fā)性內(nèi)存,存儲特性相當于硬盤,因此成為便攜式數(shù)字設(shè)備的存儲介質(zhì),同時Flash存儲器采用串行結(jié)構(gòu),讀寫單元以頁和塊為單位,容量可以很大,成本低廉,而且又能確保數(shù)據(jù)讀寫的正確性。閃存的I/O端口有8位,數(shù)據(jù)傳送的方式是輪流傳送命令字。DSP采集到的32位語音數(shù)據(jù),通過外部總線分4次,從左往右聲道寫入閃存中。

1.5 電源接口模塊

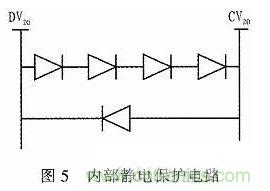

TMS320C5416DSP的供電結(jié)構(gòu)采用雙電源器件芯片,內(nèi)核電源CVDD和I/O電源DVDD,需要考慮相對電壓和上電次序。兩種供電控制策略不同:DVDD是3.3 V單電源上電,而CVDD只加載1.6 V,降低供電是想要降低芯片的功耗。雙供電模式可以消除電源間的延時。在理想狀態(tài)下,I/O電源和內(nèi)核電源應該同時加電,但實際情況下想要做到并不容易。如果不能同時加電,需要根據(jù)引腳電平對工作模式進行配置,內(nèi)核要優(yōu)先于I/O供電,要求一種電壓要低于操作電壓,另一個電壓供電時間不能超出要求。上電過程中,要保證I/O緩沖接收到正確的內(nèi)核輸出,并防止系統(tǒng)的總線沖突。加電次序主要取決于內(nèi)部靜電保護電路如圖5所示。

圖5中可見,需要DVDD不超出CVDD 2 V,于是采用4個二極管降壓,而內(nèi)核電源不能超過I/O電源電壓0.5 V,因此只用一個二極管,否則容易損壞芯片。

2 系統(tǒng)軟件設(shè)計模塊

本語音錄放系統(tǒng)的軟件環(huán)境是DSP集成開發(fā)環(huán)境IDE提供成熟的核心功能和便捷的圖形可視化工具,使得設(shè)計更快。CCS2.0提采用圖形接口界面,有編輯工具和工程管理工具,提供軟件開發(fā)、程序調(diào)試和仿真環(huán)境,集成了匯編器、編譯器、建庫工具等。CCS集成的代碼調(diào)試工具具備各種調(diào)試功能,同時支持匯編和C/C++語言,本系統(tǒng)的程序軟件均采用C語言混合編寫。既容易調(diào)試,又能提高軟件的執(zhí)行效率,能對DSP進行指令級仿真和實時數(shù)據(jù)分析。同時它還具有豐富的庫函數(shù)。

本系統(tǒng)的軟件部分主要是從現(xiàn)場線路輸入和麥克語音所采集到的信號,收集并存儲到Flash存儲器中,由濾波后播出信號,并將信號變換到頻域,即FFT離散傅立葉快速變換。

2.1 語音分析子模塊

現(xiàn)場輸入的語音信號,送入立體聲音頻編解碼器AIC23中,AIC23控制芯片內(nèi)寄存器,將信號A/D轉(zhuǎn)換,用數(shù)字計算機處理數(shù)字信號,然后由數(shù)字濾波器濾波,再送到Flash存儲器暫存。數(shù)字濾波器是一個離散時間系統(tǒng)。程序語音模塊處理過程:首先初始化系統(tǒng),包括設(shè)置時鐘發(fā)生器、AIC23的初始化、多通道緩沖、工作變量的初始等。

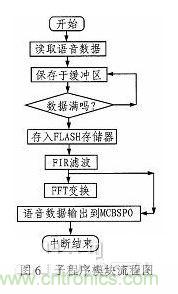

語音分析程序模塊處理過程:TLN320AIC23初始化,語音錄音數(shù)據(jù)讀取后存入數(shù)據(jù)緩沖區(qū),調(diào)用FIR數(shù)字濾波器濾波,效果突出,然后將數(shù)字語音信號暫存在閃存內(nèi),最后由耳機發(fā)出,同時進行FFT離散快速變換算法。語音數(shù)據(jù)輸出到MCBSP。語音分析子程序模塊流程圖如圖6所示。

2.2 數(shù)字濾波器設(shè)計

使用窗函數(shù)的有限長,實現(xiàn)加窗線性相位FIR數(shù)字濾波器,能夠滿足轉(zhuǎn)移序列或脈沖響應的常見問題。

b=fir1(n,Wn,‘ftype’);

b=fr1(n,Wn,‘ftype’,‘window’);

n為濾波器的階數(shù),Wn為截止頻率,ftype決定濾波器類型,high時為高通濾波器,stop時為帶阻濾波器。window采用窗函數(shù)類型,是一種通過截短和計權(quán)的方法使無限長非因果序列成為有限長脈沖應響應序列的設(shè)計方法,其默認值為漢明窗,w=hamming(n),產(chǎn)生一個n點的漢明窗函數(shù)。編寫matlab程序,生成FIR系數(shù)存放在FH[n]中,程序運行后在顯示區(qū)顯示結(jié)果。

FFT是快速計算DFT的高效方法,能夠顯著降低運算量,大大提高DFT運算速度。大部分DSP芯片能在單指令周期內(nèi)完成乘法累加運算。FFT算法是利用DFT系數(shù)的特性,合并運算,將長序列轉(zhuǎn)換為短序列DFT,以減少運算量。FFT算法的實現(xiàn)過程:

1)把N點的時域信號分解成N個時域信號,單點組成信號,并計算出頻譜。

2)輸入數(shù)據(jù)的比特反轉(zhuǎn),即將輸入序列整理成位序顛倒的次序。位碼倒置可以提高程序執(zhí)行速度和存儲效率。

3)實現(xiàn)N點復數(shù)FFT,執(zhí)行3個循環(huán)套計算FFT變換,最內(nèi)層都進行蝶形運算,第一級、第二級、第三級至第log2N級都是蝶形運算。序列點數(shù)N=2m,N為2的整數(shù)冪的FFT算法。

4)估計功率普

,X(k)一般分成虛部和實部,計算時將FFT算法變換好的數(shù)據(jù)求平方和。

2.3 控制寄存器程序設(shè)計

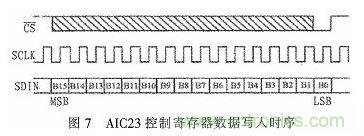

本文的TLV320AIC23利用串行傳輸數(shù)據(jù)。前半部分數(shù)據(jù)控制所需存放寄存器地址,后半部分將所要寫入的值保存在寄存器中。采用兩個8 bit處理串行傳輸?shù)目刂茢?shù)據(jù)。結(jié)合實際本文對于I2C寫入模塊采用匯編語言。

DSP通過I2C總線將配置命令發(fā)送到AIC23,完成初始化配置,然后AIC23開始工作。AIC23的初始化記錄在一個數(shù)組中,利用串口發(fā)送命令,采用循環(huán)方式發(fā)送。AIC23數(shù)據(jù)寫入時序圖如圖7。

如圖中所示B[15~9]是記錄控制寄存器的地址,B[8~0]是要寫入的值被保存在寄存器中。

3 結(jié)論

文中設(shè)計了TMS320C5416DSP芯片的音頻信號濾波系統(tǒng),結(jié)合音頻編解碼TLV320AIC23芯片、FLASH存儲器等完成語音錄放器硬件的設(shè)計過程;軟件設(shè)計分為語音設(shè)計子程序和控制寄存器程序設(shè)計。在CCS環(huán)境下的C語言編程,將外部輸入的語音信號,經(jīng)AIC23進行采樣后保存在外擴存儲器中,再經(jīng)過DSP帶緩沖串口MCBSP 2讀入DSP,經(jīng)過FIR濾波器濾除信號中的噪聲,最后進行離散傅立葉快速變換再進行播放。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: