【導讀】當你需要從一個不帶數(shù)模轉換器(DAC)的微控制器輸出模擬信號時,你可以外加一個DAC芯片。但是你也可以用另一種更經(jīng)濟的方法,即采用脈寬調(diào)制(PWM)輸出加低通濾波器(LPF)取其平均值的方法,該平均值等于PWM信號的占空比。

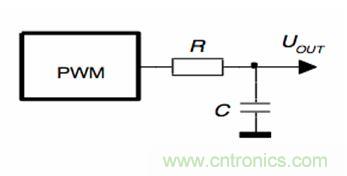

圖1:用RC低通濾波器得到PWM信號的平均值

RC低通濾波器濾除掉非直流信號,得到的便是平均信號UOUT。如果PWM信號的周期T為63個時鐘周期,UOUT將會是64個離散DC值之一。(0 到 63,6位分辨率。)

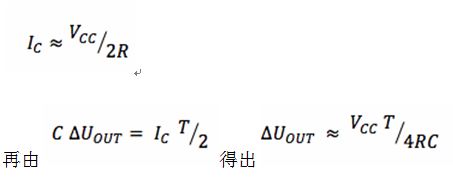

RC低通濾波器的時間常數(shù)τ必須足夠大以平滑輸出信號UOUT,紋波?UOUT應小于一個最低有效位(LSB)。最壞的情況出現(xiàn)在50% 占空比時(如圖2所示)。當τ遠大于周期T時,電容的充電電流IC 和變化?UOUT可近似為:

對于一個6位的DAC,UOUT應小于 VCC/64,要求濾波器的τ=RC ≥ 16·T。

圖2:濾波輸出(藍色)的紋波應小于一個LSB

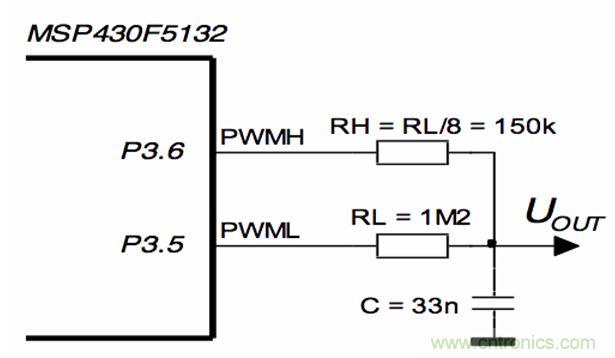

一些實用數(shù)據(jù):低功耗微處理器常使用一個32768Hz晶體振蕩器作為PWM模塊的時鐘信號。如果是6位PWM,則周期T為64/32768≈2ms,因此需要32ms的時間常數(shù),也就是要等待5τ(160ms)來使6位轉換器穩(wěn)定。非常慢。本設計實例將展現(xiàn)你如何才能加速完成信號的轉換。

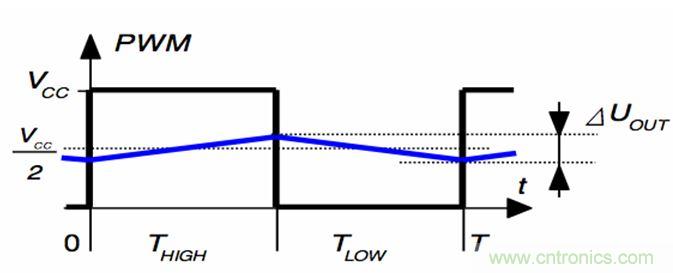

微控制器中的PWM模塊通??梢援a(chǎn)生多個PWM信號。我們來考慮一下將兩個基于PWM的3位DAC(DACH和DACL)的輸出求和,求和前DACL輸出的幅度被減小到了八分之一。得到的信號相當于一個6位DAC,但將會比簡單版本有重大的優(yōu)勢:周期T對于相同的分辨率僅為8個時鐘周期,而所需的時間常數(shù)τ是原來的八分之一,DAC的穩(wěn)定時間快了8倍。這樣改進后就很容易用電阻為兩個PWM信號(PWMH、PWML)實現(xiàn)RC濾波器:

圖3:將兩個基于PWM的DAC輸出合到一起

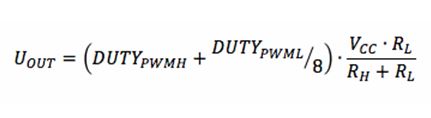

輸出信號UOUT等于:

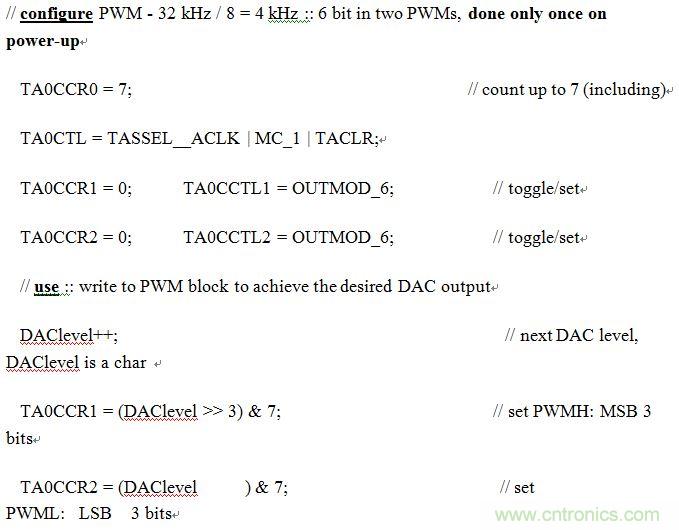

這一技術已經(jīng)在TI MSP430F5132微控制器中實現(xiàn):

圖4:基于6位(3+3)PWM的DAC的初始化和寫入代碼

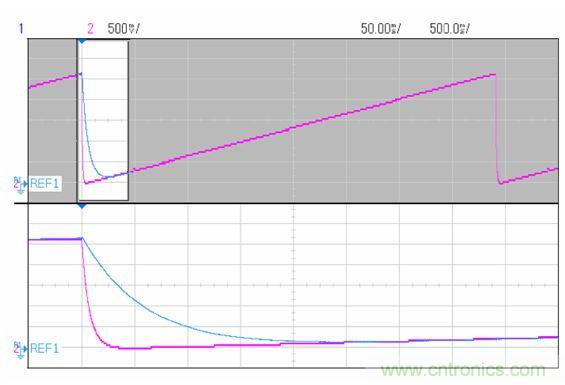

圖5:基于6位PWM的DAC測量輸出;藍線:圖1方案(穩(wěn)定時間160ms);紫線:圖3方案(穩(wěn)定時間20ms)。

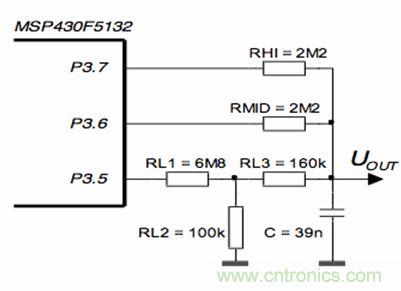

7位DAC可以用1%精度的電阻實現(xiàn)。這次,兩個PWM信號用來產(chǎn)生兩個3位DAC,最終實現(xiàn)6位的效果,MSb只用P3.7引腳來設置為0或1。

圖6:基于7位PWM的DAC的實現(xiàn)

圖7:圖6電路的測量輸出結果;注意其優(yōu)秀的線性度

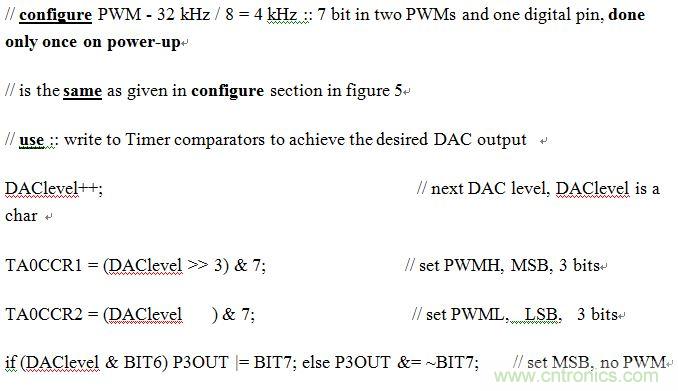

圖8:基于7位(3+3+1)PWM的DAC的初始化和寫入代碼

這里的速度提升更加明顯。一個簡單的PWM DAC需要128個時鐘周期(128/32768 s-1=3.9ms),因此τ=32·T=125ms,穩(wěn)定時間為5·125ms=625ms。圖7的穩(wěn)定時間為40ms,快了16倍。使用高階的LPF濾波器也有助于縮短穩(wěn)定時間。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: