【導讀】本文談到這么多年來最受關注的電源噪聲測量問題,有最實用的經(jīng)驗總結(jié),有實測案例佐證,有仿真分析相結(jié)合。一起來看看吧!

電源噪聲是電磁干擾的一種,其傳導噪聲的頻譜大致為10kHz~30MHz,最高可達150MHz。電源噪聲,特別是瞬態(tài)噪聲干擾,其上升速度快、持續(xù)時間短、電壓振幅度高、隨機性強,對微機和數(shù)字電路易產(chǎn)生嚴重干擾。

在電源噪聲的分析過程中,比較經(jīng)典的方法是使用示波器觀察電源噪聲波形并測量其幅值,據(jù)此判斷電源噪聲的來源。但是隨著數(shù)字器件的電壓逐步降低、電流逐 步升高,電源設計難度增大,需要使用更加有效的測試手段來評估電源噪聲。本文是使用頻域方法分析電源噪聲的一個案例,在觀察時域波形無法定位故障時,通過 FFT(快速傅立葉變換)方法進行時頻轉(zhuǎn)換,將時域電源噪聲波形轉(zhuǎn)換到頻域進行分析。電路調(diào)試時,從時域和頻域兩個角度分別來查看信號特征,可以有效地加 速調(diào)試進程。

在單板調(diào)試過程中發(fā)現(xiàn)一個網(wǎng)絡的電源噪聲達到80mv,已經(jīng)超過器件要求,為了保證器件能夠穩(wěn)定工作必須降低該電源噪聲。

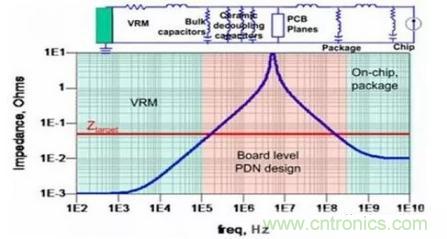

在調(diào)試該故障前先回顧下電源噪聲抑制的原理。如下圖所示,電源分配網(wǎng)絡中不同的頻段由不同的元件來抑制噪聲,去耦元件包含電源調(diào)整模塊(VRM)、去耦 電容、PCB電源地平面對、器件封裝和芯片。VRM包含電源芯片及外圍的輸出電容,大約作用于DC到低頻段(100K左右),其等效模型是一個電阻和一個 電感組成的二元件模型。去耦電容最好使用多個數(shù)量級容值的電容配合使用,充分覆蓋中頻段(數(shù)10K到100M左右)。由于布線電感和封裝電感的存在,即時 大量堆砌去耦電容也難以在更高頻起到作用。PCB電源地平面對形成了一個平板電容,也具有去耦作用,大約作用在數(shù)十兆。芯片封裝和芯片負責高頻段 (100M以上),目前的高端器件一般會在封裝上增加去耦電容,此時PCB上的去耦范圍可以降低到數(shù)十兆甚至幾兆。因此,在電流負載不變的情況下,我們只 要判斷出電壓噪聲出現(xiàn)在哪個頻段,那么針對這個頻段所對應的去耦元件進行優(yōu)化即可。在兩個去耦元件的相鄰頻段時兩個去耦元件會配合作用,所以在分析去耦元 件臨界點時相鄰頻段的去耦元件也要同時納入考慮。

根據(jù)傳統(tǒng)電源調(diào)試經(jīng)驗,首先在該網(wǎng)絡上增加了一些去耦電容,增加電源網(wǎng)絡的阻抗余量, 保證在中頻段的電源網(wǎng)絡阻抗都能滿足該應用場景的需求。結(jié)果紋波僅降低幾mV,改善微乎其微。產(chǎn)生這個結(jié)果有幾個可能:1、噪聲處在低頻,并不在這些去耦 電容起作用的范圍內(nèi);2、增加電容影響了電源調(diào)節(jié)器VRM的環(huán)路特征,電容帶來的阻抗降低與VRM的惡化抵消了。帶著這個疑問,我們考慮使用示波器的頻域 分析功能來查看電源噪聲的頻譜特性,定位問題根源。

示波器的頻域分析功能是通過傅立葉變換實現(xiàn)的,傅立葉變換的實質(zhì)是任何時域的序列都可以表示為不同頻率的正弦波信號的無限疊加。我們分析這些正弦波的頻率、幅值和相位信息,就是將時域信號切換到頻域的分析方法。數(shù)字示波器采樣到的序列是離散序列,所以我們在分析中最常用的是快速傅立葉變換(FFT)。 FFT算法是對離散傅立葉變換(DFT)算法優(yōu)化而來,運算量減少了幾個數(shù)量級,并且需要運算的點數(shù)越多,運算量節(jié)約越大。

示波器捕獲的噪聲波形進行FFT變換,有幾個關鍵點需要注意。

1、根據(jù)耐奎斯特抽樣定律,變換之后的頻譜展寬(Span)對應與原始信號的采樣率的1/2,如果原始信號的采樣率為1GS/s,則FFT之后的頻譜展寬最多是500MHz;

2、變換之后的頻率分辨率(RBW Resolution Bandwidth)對應于采樣時間的倒數(shù),如果采樣時間為10mS,則對應的頻率分辨率為100Hz;

3、頻譜泄漏,即信號頻譜中各譜線之間相互干擾,能量較低的譜線容易被臨近的高能量譜線的泄漏所淹沒。避免頻譜泄漏可以盡量采集速率與信號頻率同步,延長采集信號時間及使用適當?shù)拇昂瘮?shù)。

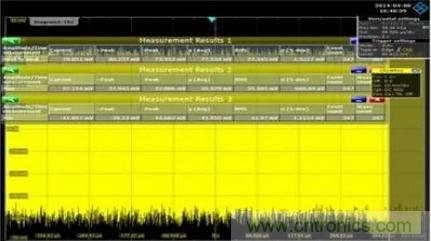

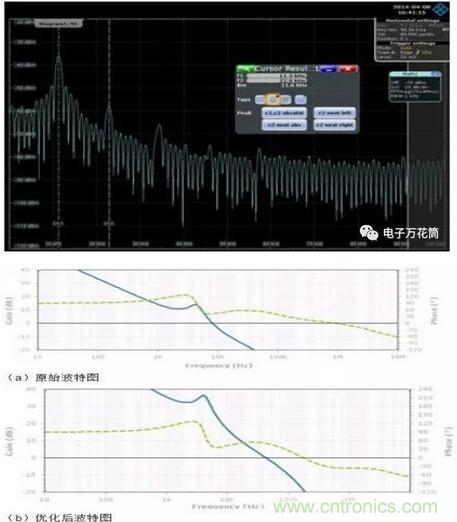

電源噪聲測量時不要求較高的采樣率,所以可以設置很長的時基,這也意味著采集的信號時間可以足夠長,可以認為覆蓋到了整個有效信號的時間跨度,此時不需 要添加窗函數(shù)。調(diào)整以上設置可以得到比較準確的FFT變換曲線了,再通過zoom功能查看感興趣的頻點。如下圖中電源噪聲的主要能量集中在11.3KHz 左右,并以該頻率為基波頻率諧振。據(jù)此可以推斷本PDN網(wǎng)絡在11.3KHz處的阻抗不能滿足要求,電容在該頻點的阻抗也比較高,起不到降低阻抗的作用, 所以前面增加電容并不能減小電源噪聲。

一般來說,11.3KHz應該是VRM的管轄范圍,此處出現(xiàn)較大噪聲說明VRM電路設計不能滿足 要求。這里對VRM的性能進行分析,VRM分析的方法眾多,此處主要采用仿真其反饋環(huán)路波特圖的手段。波特圖主要觀察幾個關鍵信息:1、穿越頻率,增益曲 線穿越0dB線的頻率點;2、相位裕度,相位曲線在穿越頻率處所對應的相位值;3、增益裕度,相位在-360°時所對應的增益值。這里我們主要關注穿越頻 率和相位裕度這兩個指標。從VRM的環(huán)路波特圖(如下圖a)可以看到,VRM的穿越頻率在8KHz左右,相位裕度37度。這里存在兩個問題:首先VRM的 相位裕度一般需要大于45度才能保證環(huán)路的穩(wěn)定工作,這里相位裕度稍小一些,需要增加相位裕度;其次穿越頻率太低,穿越頻率附近VRM的調(diào)整作用逐漸降低,而此頻點bulk電容還起不到作用,所以在8KHz附近會存在較高的阻抗,這個頻點的噪聲抑制作用較差。下圖(b)是優(yōu)化VRM環(huán)路之后的波特圖,調(diào)整相位裕度到50度,穿越頻率推到46KHz左右。

對優(yōu)化后的VRM驗證紋波,可以看到紋波明顯降低到33mv,能夠滿足器件要求。

上述案例是使用示波器FFT功能快速定位電源問題的過程,從這個例子可以看到示波器的頻域分析功能在電路調(diào)試時可以發(fā)揮很大作用。示波器的FFT功能配合長存儲深度可以很方便地分析低頻率長周期信號,這個優(yōu)勢在數(shù)字電路調(diào)試中比較突出。