【導讀】諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器件可以具有模擬和數(shù)字電源電壓以及I/O電壓。

諸如放大器和轉(zhuǎn)換器等模擬集成電路具有至少兩個或兩個以上電源引腳。對于單電源器件,其中一個引腳通常連接到地。如ADC和DAC等混合信號器件可以具有模擬和數(shù)字電源電壓以及I/O電壓。像FPGA這樣的數(shù)字IC還可以具有多個電源電壓,例如內(nèi)核電壓、存儲器電壓和I/O電壓。

不管電源引腳的數(shù)量如何,IC數(shù)據(jù)手冊都詳細說明了每路電源的允許范圍,包括推薦工作范圍和最大絕對值,而且為了保持正常工作和防止損壞,必須遵守這些限制。

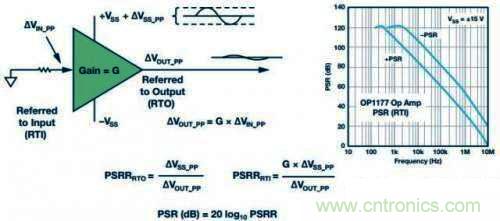

然而,由于噪聲或電源紋波導致的電源電壓的微小變化—即便仍在推薦的工作范圍內(nèi)—也會導致器件性能下降。例如在放大器中,微小的電源變化會產(chǎn)生輸入和輸出電壓的微小變化,如圖1所示。

圖1. 放大器的電源抑制顯示輸出電壓對電源軌變化的靈敏度。

放大器對電源電壓變化的靈敏度通常用電源抑制比(PSRR)來量化,其定義為電源電壓變化與輸出電壓變化的比值。

圖1顯示了典型高性能放大器(OP1177)的PSR隨頻率以大約6dB/8倍頻程(20dB/10倍頻程)下降的情況。圖中顯示了采用正負電源兩種情況下的曲線圖。盡管PSRR在直流下是120dB,但較高頻率下會迅速降低,此時電源線路上有越來越多的無用能量會直接耦合至輸出。

如果放大器正在驅(qū)動負載,并且在電源軌上存在無用阻抗,則負載電流會調(diào)制電源軌,從而增加交流信號中的噪聲和失真。

盡管數(shù)據(jù)手冊中可能沒有給出實際的PSRR,數(shù)據(jù)轉(zhuǎn)換器和其他混合信號IC的性能也會隨著電源上的噪聲而降低。電源噪聲也會以多種方式影響數(shù)字電路,包括降低邏輯電平噪聲容限,由于時鐘抖動而產(chǎn)生時序錯誤。

分析運算放大器和反饋電阻的動態(tài)特性

瑞芯微電子與OPPO簽訂VOOC閃充專利許可協(xié)議

高頻PCB電路設計常見的66個問題

淺析電阻分壓采樣電路

詳解功率MOS管的五種損壞模式