【導讀】介紹了一種基于fpga的多軸控制器,控制器主要由arm7(LPC2214)和fpga(EP2C5T144C8)及其外圍電路組成,用于同時控制多路電機的運動。

利用Verilog HDL硬件描述語言在fpga中實現(xiàn)了電機控制邏輯,主要包括脈沖控制信號產生、加減速控制、編碼器反饋信號的辨向和細分、絕對位移記錄、限位信號保護邏輯等。論文中給出了fpga內部一些核心邏輯單元的實現(xiàn),并利用QuartusⅡ、Modelsim SE軟件對關鍵邏輯及時序進行了仿真。實際使用表明該控制器可以很好控制多軸電機的運動,并且能夠實現(xiàn)高精度地位置控制。

隨著電機廣泛地應用于數(shù)字控制系統(tǒng)中,對電機控制的實時性和精度上的要求越來越高。如何靈活、有效地控制電機的運行成為研究的主要方向。文中采用現(xiàn)場可編程邏輯門陣列(Field Programmable Gate Array,fpga),通過Verilog語言編程來實現(xiàn)電機的控制。利用fpga設計具有硬件設計軟件化、高度集成化、高工作頻率等優(yōu)點。fpga最大的特點就是靈活,實現(xiàn)你想實現(xiàn)的任何數(shù)字電路,可以定制各種電路,減少受制于專用芯片的束縛,真正為自己的產品量身定做。在設計的過程中可以靈活的更改設計,而且它強大的邏輯資源和寄存器資源可以讓你輕松的去發(fā)揮設計理念。其并行執(zhí)行,硬件實現(xiàn)的方式可以應對設計中大量的高速電子線路設計需求。

1.多軸控制器主要功能

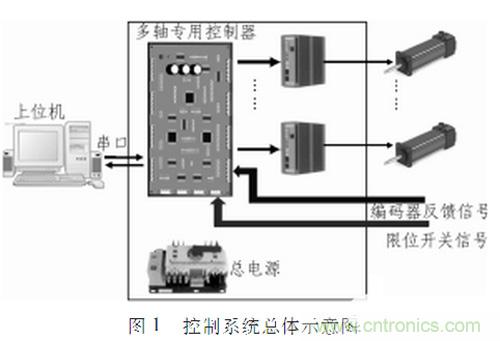

多軸控制器與上位機、電機驅動器等配合使用,圖1為采用多軸控制器組成的控制系統(tǒng)總體示意圖。控制器接收上位機發(fā)送的控制指令,分析處理并產生相應的方向信號、脈沖信號給驅動器,從而達到控制電機運行的目的。為了提高系統(tǒng)的控制精度,將電機的編碼器信號作為反饋信號輸入給控制器(內部實現(xiàn)自動辨向及四細分)。在各軸運動過程中,專用控制器對電機運行的絕對位移進行記錄,并且可以實時地將各軸的絕對位置信息上傳給上位機。另外在電機運行的過程中,為了保證電機運行的安全性,控制器還采用了限位信號反饋實現(xiàn)全硬件保護措施。

2.多軸控制器組成

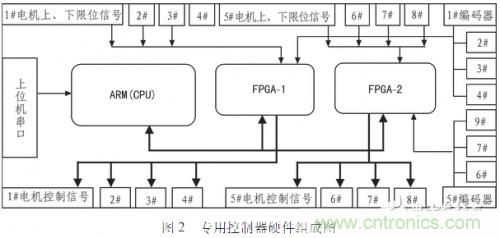

專用控制器由arm(LPC2214)、fpga(EP2C5T144C8)、驅動器接口電路、編碼器接口電路、限位檢測電路和電源電路等組成,如圖2為一個八軸電機控制器的硬件組成圖。arm通過串口實現(xiàn)與上位機之間的通信,解析從上位機獲得的控制指令,并通過fpga產生相應輸出信號給驅動器接口,驅動器接口外接驅動器。編碼器信號作為位置反饋信號同編碼器接口相連,形成位置環(huán)反饋。限位信號作為安全檢測信號同限位檢測接口相連,為整個系統(tǒng)添加一道安全保障。

3.fpga控制邏輯

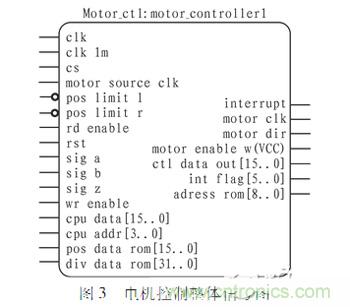

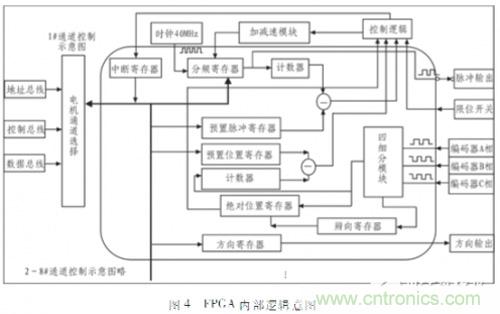

專用控制器在完成整個控制的過程中,arm只負責指令解析、控制指令發(fā)送、實時數(shù)據(jù)上傳等任務,fpga才是多軸專用控制器的核心。通過Verilog HDL語言在fpga內部實現(xiàn)了加減速曲線、編碼器信號辯向及四細分、絕對位移記錄等功能。圖3為電機控制的整體輸入、輸出信號圖,通過片選信號CS、讀有效信號rd_enable、寫有效圖信號wr_enable進行電機通道選擇。圖4給出了1#通道控制的fpga內部邏輯示意圖,下面將逐一對各主要模塊進行詳細介紹。

1)加減速曲線模塊

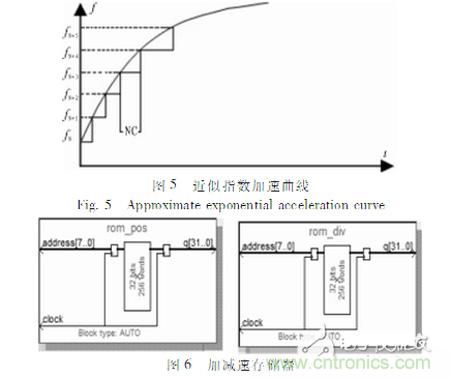

為了更有效、更理想地控制電機的運行,在fpga內部設計了加減速曲線模塊。文中采用了一種近似指數(shù)加減速曲線的方法,如圖5為近似指數(shù)加速曲線,減速曲線與之對稱。速度等距分布,那么在該速度級上保持的時間不一樣場。為了簡化,用速度級數(shù)N與一個常數(shù)C的乘積去模擬并且保持的時間用不熟來代替。因此,速度每升一級,電機都要在該速度級上走NC步(其中N為該速度級數(shù))。

建立兩個名為rom_pos、rom_div的ROM模塊,如圖6所示,rom_pos為脈沖個數(shù)存儲器,rom_div為分頻值存儲器。通過相同的地址線將兩個存儲器連接起來,使一個地址對應一組脈沖個數(shù)和分頻值。

fpga獲得方向信號、脈沖(距離)信號、目標分頻值之后.如果電機運行過程中不需要加減速,直接以目標分頻值控制脈沖信號的發(fā)送即可。如果需要執(zhí)行加減速,則fpga內部要調用加減速模塊。根據(jù)地址線獲取一組數(shù)據(jù),即脈沖個數(shù)pul_cnt和分頻值div_num,以div_num大小的分頻值發(fā)送pul_cnt個脈沖,然后再按照下一組數(shù)據(jù)值發(fā)送脈沖,直到分頻值達到目標分頻值為止,減速過程與加速過程對稱。當電機按照脈沖(距離)信號運行到一半行程的時候,如果分頻值還未達到目標分頻值,此時就要進行強制減速。

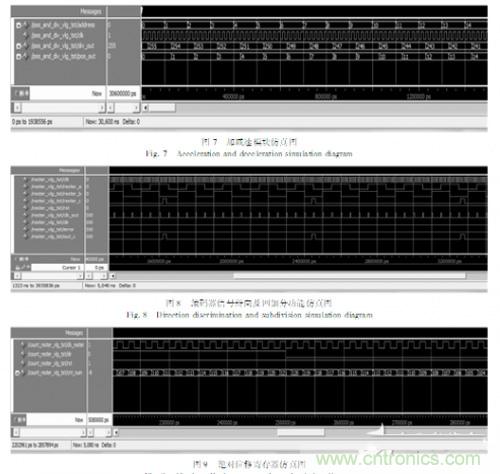

編寫仿真程序,使兩個存儲器地址線相同,對存儲器地址address做加1運算,從而可一次性讀取兩個存儲器所對應存儲單元的數(shù)據(jù)。利用Modulesim仿真工具對加減速模塊進行功能仿真,仿真結果如圖7所示,訪問一個存儲器地址就對應著一組脈沖個數(shù)和分頻值的輸出。

2)編碼器反饋辨向及四細分

編碼器反饋信號由A、B、Z三相信號組成。A、B兩相信號相位相差90度,一個周期內A、B相信號會出現(xiàn)4種不同的組合狀態(tài),根據(jù)這一特征可以對編碼器信號進行辯相和四細分處理。Z相信號為編碼器零位信號,當編碼器旋轉一圈,Z相就會有信號輸出。

在QuartusⅡ編譯環(huán)境下成功編譯之后,調用Modulesim仿真軟件,編寫仿真程序,使之產生全局時鐘、復位信號、相位差為90度的A、B相信號和Z相信號。如圖8所示,給出了該多軸控制器中所采用的編碼器信號辯相及四細分的功能仿真圖。

3)絕對位移記錄

多軸專用控制器可以將電機運行的絕對位移實時地上傳給上位機,這一功能的實現(xiàn)就有賴于fpga中的絕對位移記錄部分的邏輯功能。在fpga內部設置一個絕對位移寄存器,用來對編碼器反饋信號(辨向四細分之后)進行計數(shù)運算。當編碼器信號的一個脈沖到來時,根據(jù)辯向后的方向信號做不同的運算處理。方向為正則絕對位移寄存器的值就進行加1運算,否則進行減1運算,從而達到對絕對位移進行記錄的目的。并且arm可以隨時讀取該絕對位移寄存器的值,然后將其值上傳給上位機,從而完成實時上傳電機運行位置信息的功能。編寫仿真程序對絕對位移寄存器進行功能仿真,結果如圖9所示。

4.結束語

該方案成功已應用于某6軸Stewart平臺運動控制中,在實現(xiàn)了0.1μm的運動定位精度的同時,運動機構得到了很好的保護,多次實驗及實際使用中,該專用控制器運行安全可靠。