【導讀】在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數(shù)用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發(fā),闡述幾種有效降低輸出紋波噪聲的方法。

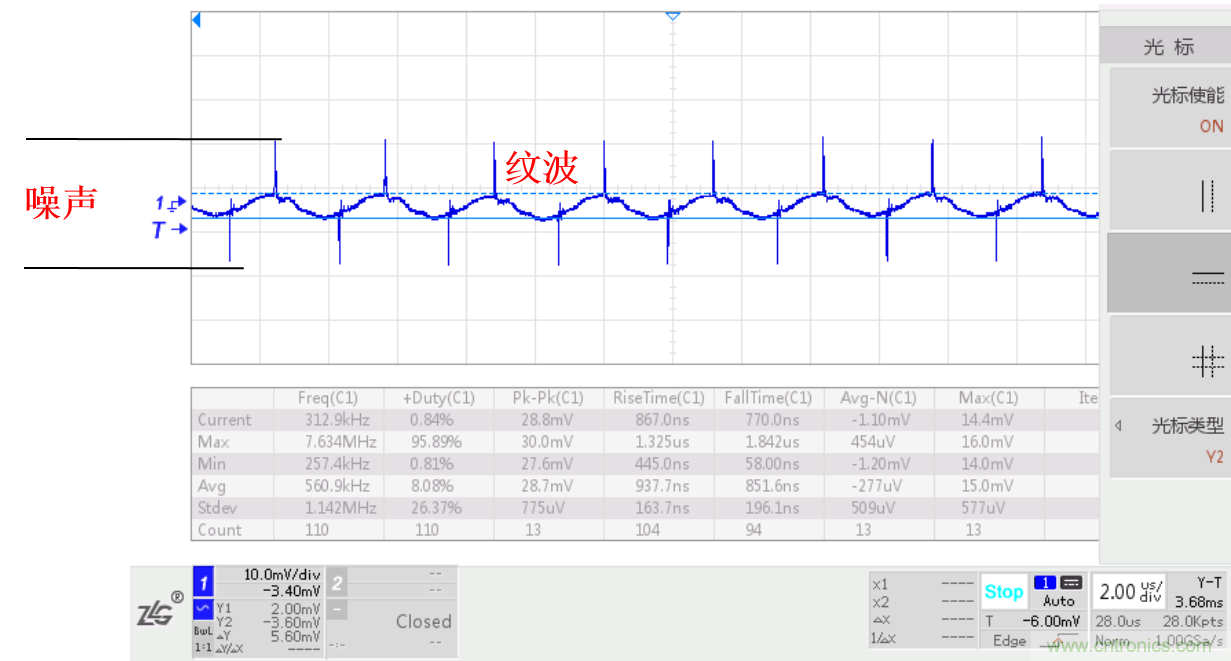

1、電源的紋波與噪聲圖示

紋波和噪聲即:直流電源輸出上疊加的與電源開關頻率同頻的波動為紋波,高頻雜音為噪聲。具體如圖1所示,頻率較低且有規(guī)律的波動為紋波,尖峰部分為噪聲。

2、紋波噪聲的測試方法

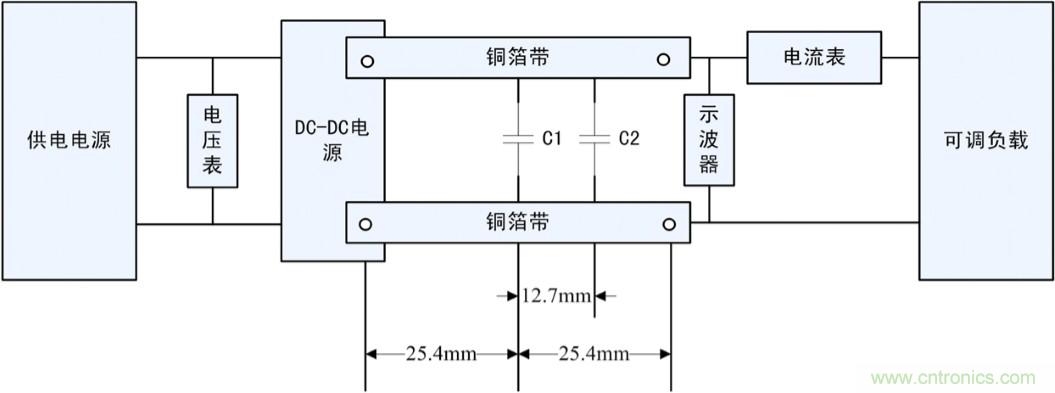

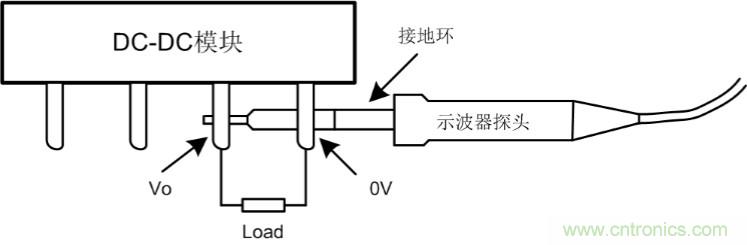

對于中小微功率模塊電源的紋波噪聲測試,業(yè)內主要采用平行線測試法和靠接法兩種。其中,平行線測試法用于引腳間距相對較大的產品,靠測法用于模塊引腳間距小的產品。

但不管用平行線測試法還是靠測法,都需要限制示波器的帶寬為20MHz,同時需要去掉地線夾。

具體如圖2和圖3所示。

圖2 平行線測試法

注1:C1為高頻電容,容量為1μF;C2為鉭電容,容量為10μF。

注2:兩平行銅箔帶之間的距離為2.5mm,兩平行銅箔帶的電壓降之和應小于輸出電壓的2%。

圖3靠測法

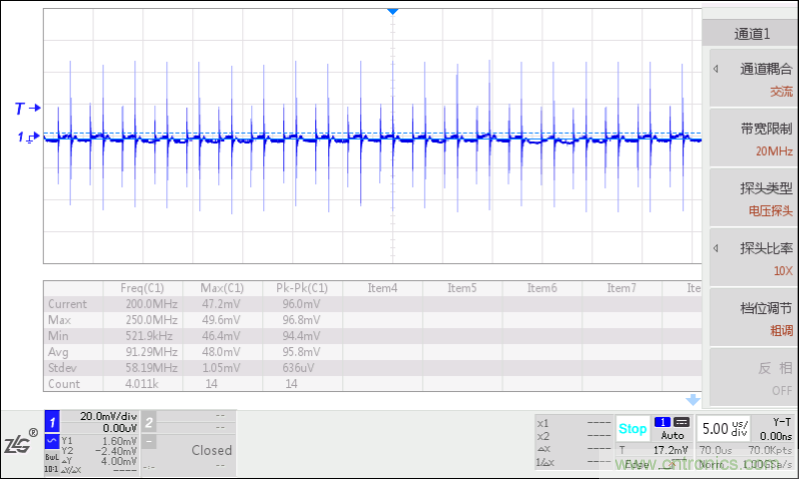

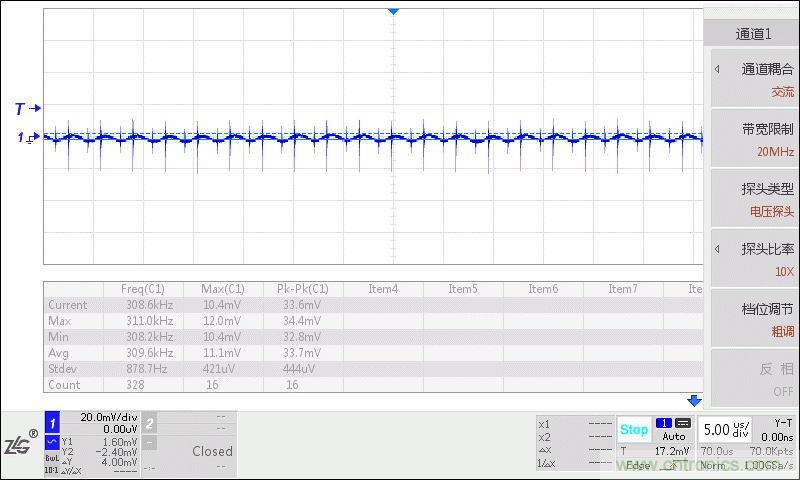

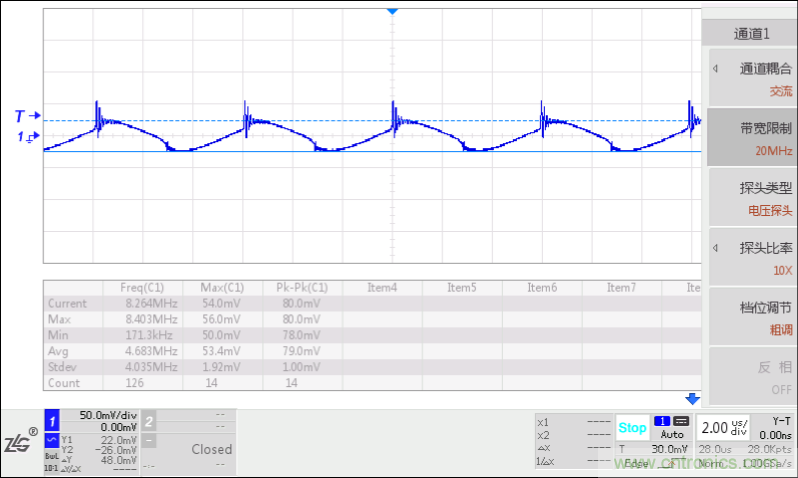

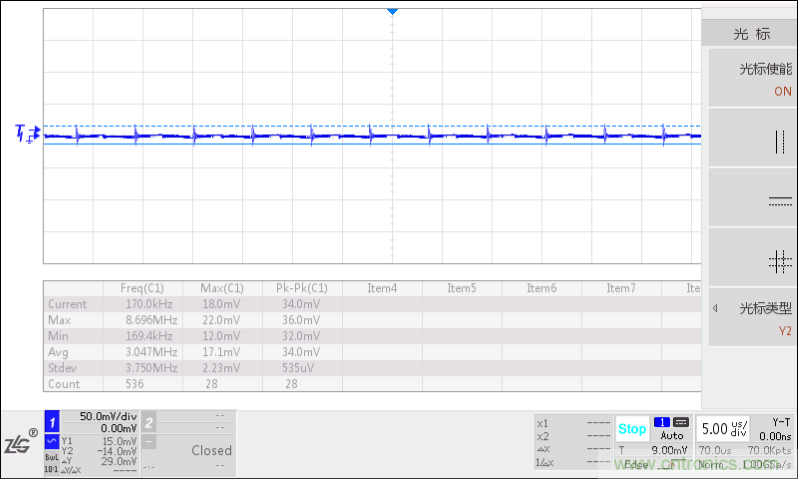

3、去除地線夾測試的區(qū)別

測試紋波噪聲需要把地線夾去掉,主要是由于示波器的地線夾會吸收各種高頻噪聲,不能真實反映電源的輸出紋波噪聲,影響測量結果。下面的圖4和圖5分別展示了對同一個產品,使用地線夾及取下地線夾測試的巨大差異。

圖4 使用地線夾測試-示波器垂直分辨率200mv/div

圖5 去除地線夾測試-示波器垂直分辨率50mv/div

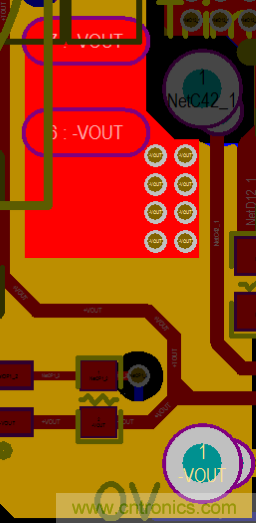

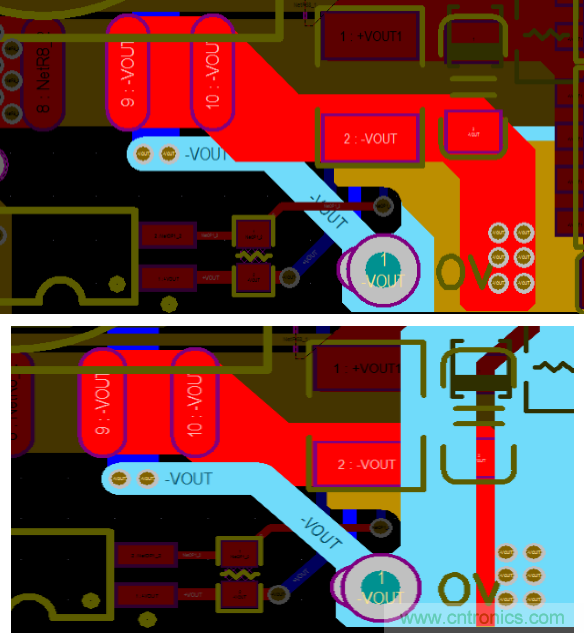

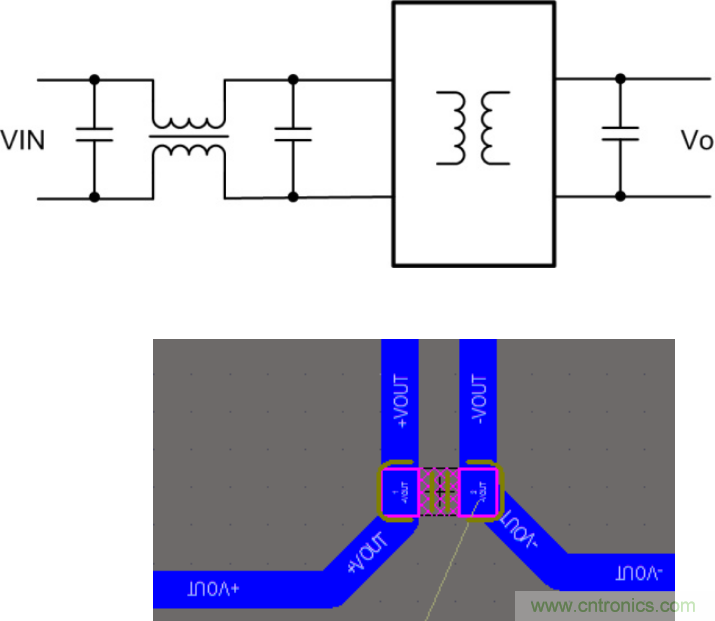

4、設計上PCB布局的影響

好與壞的PCB布局,是設計上影響紋波噪聲的關鍵因素。差的PCB布局如圖6所示,變壓器輸出的地,直接通過過孔連到背部的地平面,地平面連接電源的輸出引腳。此布局在輸出5V/2A的負載下,實測電源尖峰達1.5V VP-P。

圖6 差的PCB布局

如圖7 所示是比較好的PCB布局,調整了變壓器的位置,將變壓器輸出地通過兩個電容后,再回到地平面和輸出引腳相連。實測在相同5V/2A輸出的負載下,噪聲已降到60mV VP-P,差別顯著。

圖7 好的PCB布局

5、輸出濾波電容的影響

輸出濾波電容的容值、ESR對模塊輸出的紋波噪聲也有直接影響。按圖8所示的 產品測試紋波噪聲。

外部不加外接電容,測試輸出的紋波噪聲,如圖圖9所示,約為100mV。同樣的輸入、負載條件下,電源的輸出端加226的MLCC,實測電源輸出的紋波噪聲降到不到40mV。

圖8 測試用圖

圖9 無外接電容

圖10 外加226電容

實際應用時,電容除容量、ESR外,建議負載端的電容在回到電源之前,先匯集到輸出電容,經過電容濾波后,再回到電源,從而有效降低紋波噪聲對電路的影響。如圖11所示。

圖11 外部電容的位置

6、電感對紋波噪聲的影響

電感的感量及寄生電容對紋波噪聲的影響同樣顯著。一般地,感量大時對紋波抑制作用明顯,寄生電容小的電感對噪聲抑制效果好。以對紋波抑制為例,測試對電源輸出紋波的影響,測試圖如圖12所示。

圖12 測試電感濾波效果用例

根據(jù)圖12,我們先人為的把產品內部的濾波電感短路,只用電容濾波,測得紋波噪聲如圖13所示,紋波峰峰值約50mV。

圖13 人為短路內部濾波電感的紋波噪聲圖

下一步,在電源外部增加一個LC電路,在相同輸入、負載條件下,重測紋波噪聲圖,如圖14所示,紋波已接近直線,非常小。

圖14 外加LC的紋波噪聲圖

以上簡單從紋波噪聲的圖例、測試方法開始,描述從電源設計、外部電路應用出發(fā),結合實際測試比較幾種降低紋波噪聲的方法。實際的工程應用中還需考慮電容、電感的負載效應、自激影響等,還需再做深究。

推薦閱讀: