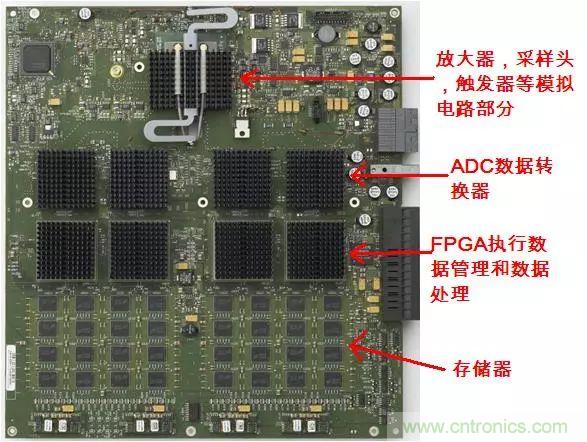

【導(dǎo)讀】圖1是90000-X示波器的捕獲板。90000-X示波器使用磷化銦技術(shù),其硬件帶寬可達(dá)33GHz,實(shí)時采樣率可達(dá)80GSa/s,存儲深度可達(dá)2GB。這些指標(biāo)都達(dá)到了業(yè)界頂尖的水平。

但是隨著采樣速率和存儲深度的提升,數(shù)字信號處理能力成為一大挑戰(zhàn),傳統(tǒng)的使用內(nèi)置計(jì)算機(jī)的Matlab軟件處理方式已經(jīng)不能滿足測試速度的要求?,F(xiàn)在,90000和90000-X示波器采用FPGA硬件進(jìn)行數(shù)字信號的處理,代表了示波器數(shù)字信號處理技術(shù)發(fā)展的方向。

90000和90000-X示波器的FPGA執(zhí)行了如下處理,大幅度提升了示波器響應(yīng)的速度;其FPGA也集成了嵌入去嵌入和精密探頭校準(zhǔn)算法,也大幅度提升了測試精度。

1、MegaZoom處理核

MegaZoom處理核集成在FGPA內(nèi)部,它對存儲器進(jìn)行管理。首先是使用乒乓處理技術(shù),把存儲器分為兩部分,一部分捕獲數(shù)據(jù)時,另一部分在傳遞數(shù)據(jù)。這樣波形更新速度可提升一倍。

MegaZoom也進(jìn)行壓縮處理,進(jìn)行屏幕顯示波形數(shù)據(jù)運(yùn)算,只傳遞需要顯示的數(shù)據(jù)到示波器屏幕上,這樣刷新速率會提升許多倍。一旦需要測量數(shù)據(jù),再把數(shù)據(jù)傳遞給內(nèi)部計(jì)算機(jī)進(jìn)行參數(shù)計(jì)算?,F(xiàn)在已經(jīng)能夠用FPGA處理一部分測量參數(shù)了,只傳遞測量參數(shù),速度又將大幅提升。

2、FPGA進(jìn)行波形參數(shù)測量

現(xiàn)在已經(jīng)把一部分測試參數(shù)用FPGA實(shí)現(xiàn)了,未來會把主要的測量參數(shù)都用FPGA實(shí)現(xiàn),整個示波器的速度又會大幅度提升。

3、FPGA進(jìn)行正弦內(nèi)插

傳統(tǒng)的示波器的Sinx/x正弦內(nèi)插是用內(nèi)置計(jì)算機(jī)的Matlab來實(shí)現(xiàn),一旦設(shè)置的存儲深度比較深,則示波器的速度會變得很慢,現(xiàn)在用FPGA來實(shí)現(xiàn),則沒有這樣的瓶頸。

4、FPGA進(jìn)行幅度和相位修正

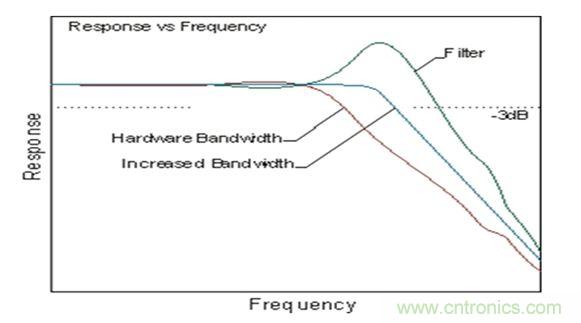

硬件放大器、采樣保持電路的幅頻和相頻響應(yīng)沒法做到很完美,那用FPGA進(jìn)行幅度和相位修正是理想化頻響的正當(dāng)方法。有的示波器也可以用這種修正來提升或降低示波器的帶寬。圖2是提升示波器帶寬的方法,應(yīng)用一個高通濾波器(圖2綠色曲線),提升示波器帶寬(原來硬件帶寬曲線是紅色曲線)到更高數(shù)量級(藍(lán)色曲線)。

圖2. DSP提升示波器帶寬的方法

5、FPGA進(jìn)行觸發(fā)抖動修正

硬件觸發(fā)器的觸發(fā)抖動一般是1PS以上,可以用FPGA進(jìn)行觸發(fā)抖動修正到100fs量級,這樣提升了單個波形的觸發(fā)精度。但是沒法修正雙通道的時間偏差不確定度。

6、FPGA進(jìn)行FFT運(yùn)算和頻譜觸發(fā)

用FPGA進(jìn)行FFT運(yùn)算可大幅度提升FFT處理的速度,并且可以進(jìn)行頻譜觸發(fā)。用內(nèi)置計(jì)算機(jī)的Matlab進(jìn)行FFT處理,當(dāng)內(nèi)存深度設(shè)置比較深時一般較慢,也沒法進(jìn)行頻譜觸發(fā)。

7、FPGA執(zhí)行嵌入和去嵌入處理,執(zhí)行精密探頭校準(zhǔn)參數(shù)的處理

用FPGA執(zhí)行嵌入和去嵌入處理,大幅度提升了響應(yīng)速度。

由于精密探頭校準(zhǔn)參數(shù)類似于S參數(shù),校準(zhǔn)參數(shù)表的數(shù)據(jù)量比較大,只有用FPGA進(jìn)行處理,才能滿足速度的要求。

8、FPGA執(zhí)行協(xié)議觸發(fā)和協(xié)議譯碼

示波器做總線的協(xié)議分析是示波器應(yīng)用方向之一,但是用軟件做協(xié)議譯碼速度比較慢,用軟件只能進(jìn)行協(xié)議搜索,而不能進(jìn)行協(xié)議觸發(fā)?,F(xiàn)在一些示波器如3000-X示波器已經(jīng)用處理器實(shí)現(xiàn)了這個功能,使得譯碼速度很快,而且可以進(jìn)行協(xié)議的硬件觸發(fā)。高端示波器用FPGA實(shí)現(xiàn)這個功能也在研發(fā)之中。

小結(jié):

高端示波器用FPGA實(shí)現(xiàn)數(shù)字信號處理技術(shù)正在不斷提升中,這必將大幅度提升示波器的響應(yīng)速度和精度。這是示波器R&D關(guān)鍵工作之一。

推薦閱讀: