【導(dǎo)讀】近期臺積電技術(shù)長孫元成在其自家技術(shù)論壇中,首次揭露臺積電研發(fā)多年的eMRAM(嵌入式磁阻式隨機(jī)存取存儲)和eRRAM(嵌入式電阻式存儲器)將分別訂于明后年進(jìn)行風(fēng)險(xiǎn)性試產(chǎn)。預(yù)計(jì)試產(chǎn)主要采用22nm工藝。這種次世代存儲將能夠?yàn)槲锫?lián)網(wǎng)、行動裝置、高速運(yùn)算電腦和智能汽車等四領(lǐng)域所提供效能更快和耗電更低的存儲效能。臺積電此舉讓嵌入式存儲器再度回到人們的視線中。本文將為你闡述嵌入式存儲器的前世今生。

何為嵌入式存儲器

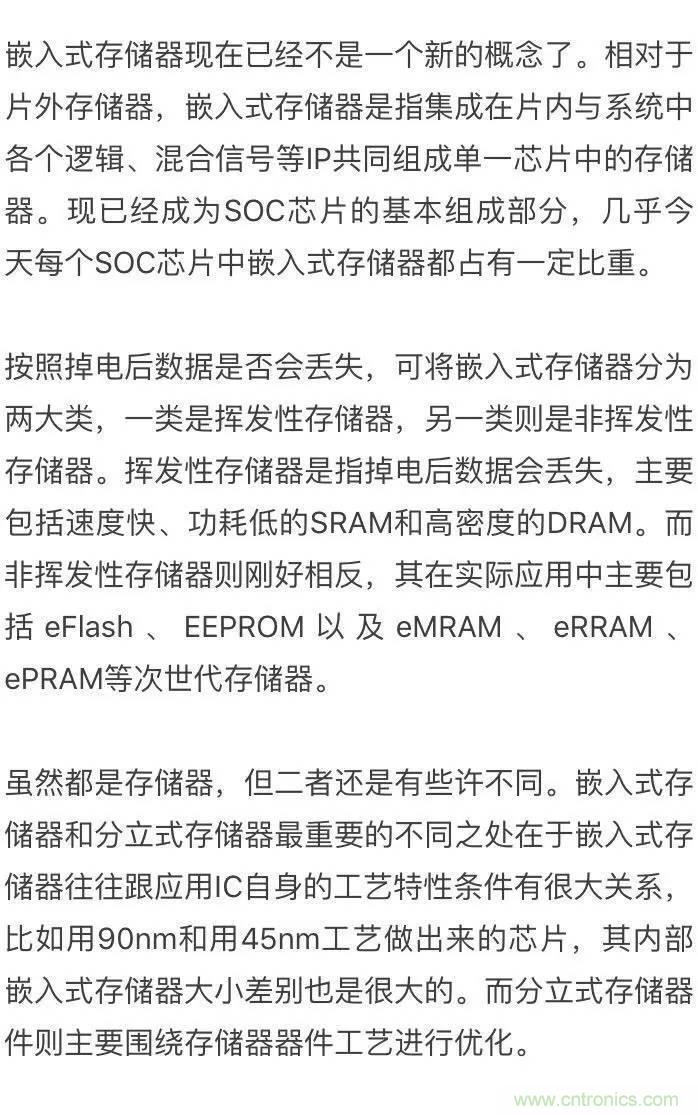

隨著信息技術(shù)的發(fā)展,嵌入式存儲器在SOC中的面積所占比重也在逐年增加,從圖一可以看出,從1999年平均的20%上升到2007年的60-70%乃至2014年的90%的面積??梢钥闯觯度胧酱鎯ζ鲗τ谛酒到y(tǒng)性能的影響越來越大。

圖一 嵌入式存儲器在SOC中所占芯片面積的比重。

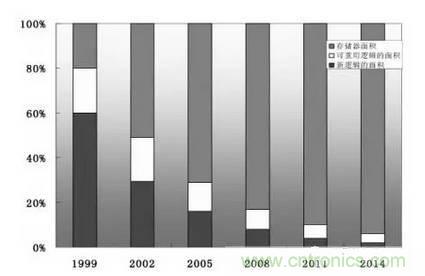

圖二 MPU于DRAM隨時(shí)代變遷而發(fā)展的關(guān)系圖

同時(shí)片內(nèi)存儲器具有靈活簡單的接口、更低延遲和更寬總線,更為重要的是還能節(jié)省系統(tǒng)的空間大小,使得它日益受到集成電路設(shè)計(jì)師的青睞。在這一時(shí)期嵌入式存儲器主要以SRAM和DRAM兩種形式呈現(xiàn)。

到了九十年代中期,Intel做了一項(xiàng)重大創(chuàng)新,將片外高速緩沖器(Cache)集成到了片內(nèi)。這直接導(dǎo)致當(dāng)時(shí)一大批分立的片外高速緩沖存儲器廠商倒閉,成為嵌入式存儲器代替分立式存儲器的標(biāo)志性事件。

到了今天一顆手機(jī)處理器超過90%的面積由各種嵌入式SRAM如寄存器堆,一二級緩存甚至三級緩存組成,嵌入式SRAM也成為晶圓代工廠的工藝技術(shù)衡量指標(biāo)。由于SRAM由六個晶體管組成,而DRAM只有一個晶體管加一個電容組成,具有面積優(yōu)勢,當(dāng)時(shí)很多廠商其實(shí)都在思考將DRAM嵌入到系統(tǒng)的可能性。

九十年代,當(dāng)時(shí)IBM,Toshiba等大公司都在嘗試開發(fā)嵌入式DRAM。但開發(fā)并不順利,開發(fā)的難點(diǎn)在于DRAM工藝與常規(guī)邏輯工藝差異很大,工藝的整合難度相當(dāng)大。雖然到今天,隨著工藝的進(jìn)步,使得一些公司像TSMC也在重新審視eDRAM的可行性,并有部分成果,但是主流的設(shè)計(jì)還是沒有將eDRAM納入必備選項(xiàng)。

后來隨著消費(fèi)類電子大幅成長,不斷擴(kuò)大的存儲需求刺激著嵌入式閃存(eFlash)不斷發(fā)展。從早期,設(shè)計(jì)人員將程序簡單固化在ROM中,到后來的OTP,EEPROM乃至現(xiàn)在很火的高密度eFlash內(nèi)存。嵌入式內(nèi)存能夠有效存儲代碼和數(shù)據(jù),而且掉電后還不丟失,對很多應(yīng)用都有重要意義。

然而走到今天,現(xiàn)有存儲技術(shù)暴露的一些缺陷,比如SRAM、DRAM的問題在于其易失性,斷電后信息會丟失且易受電磁輻射干擾,這一缺陷極大限制了其在國防航空航天等一系列關(guān)鍵高科技領(lǐng)域的應(yīng)用。而FLASH、EEPROM的寫入速度慢,且寫入算法比較復(fù)雜,無法滿足實(shí)時(shí)處理系統(tǒng)中高速、高可靠性寫入的要求,且功耗較高,無法滿足嵌入式應(yīng)用的低功耗要求。

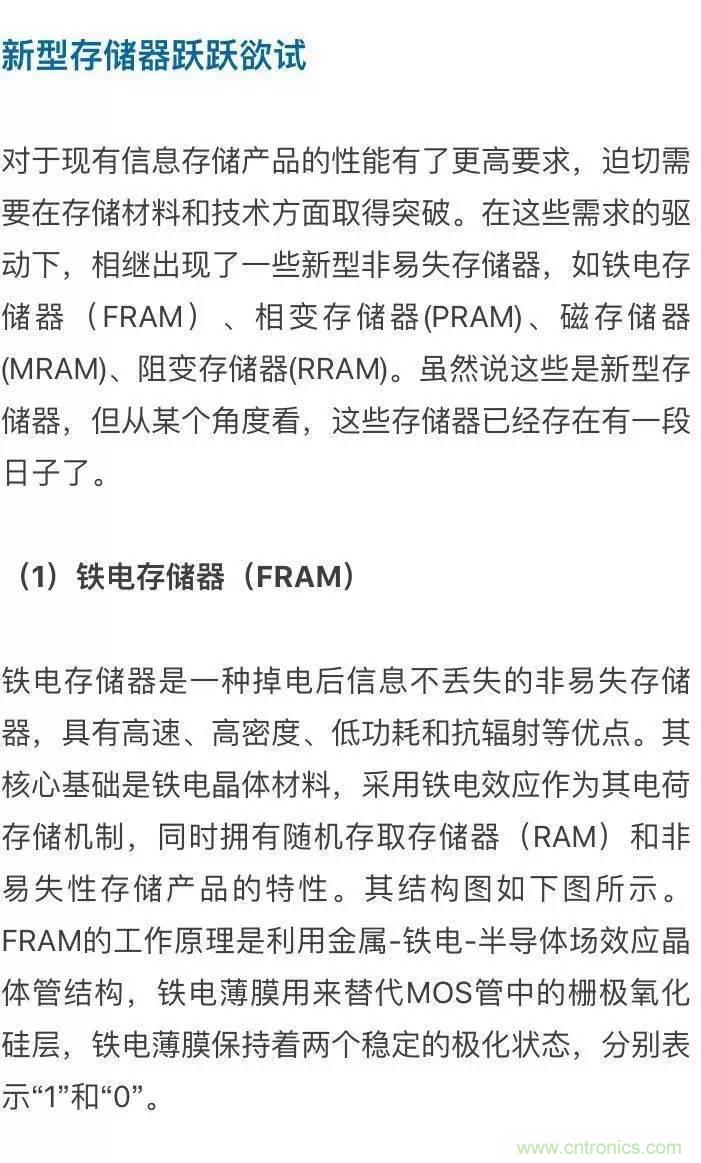

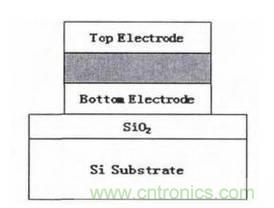

圖三 FRAM結(jié)構(gòu)剖面圖

(2)磁性存儲器(MRAM)

MRAM是利用材料的磁場隨磁場的作用而改變的原理所制成。利用磁存儲單元磁性隧道結(jié)(MTJ)的隧穿磁電阻效應(yīng)來進(jìn)行存儲。

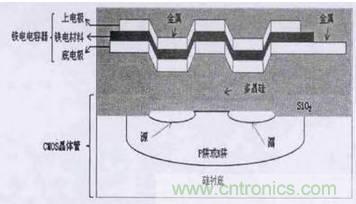

如下圖四所示,MTJ有三層,最上層為自由層,中間是隧道結(jié),下面是固定層。自由層的磁場極化方向是可以改變的,而固定層的磁場方向固定不變。當(dāng)自由層與固定層的磁場平行時(shí),存儲單元呈現(xiàn)低阻態(tài);當(dāng)磁場方向相反時(shí),存儲單元呈現(xiàn)高阻態(tài)。MRAM通過檢測存儲單元電阻的高低,來判斷所存數(shù)據(jù)是0還是1。

圖四 MJT結(jié)構(gòu)示意圖

(3)相變存儲器(PRAM)

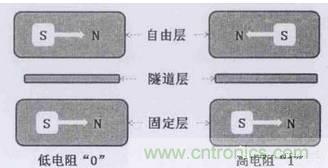

PRAM的存儲原理是利用某些薄膜合金的結(jié)構(gòu)結(jié)構(gòu)相變存儲0和1的信息。通常這些合金具有兩種穩(wěn)定狀態(tài):具有低電阻的多晶狀態(tài)和具有高電阻的無定形狀態(tài)。PRAM應(yīng)用硫系玻璃材料,利用硫族材料的電致相變特性,其在晶體和非晶體狀態(tài)呈現(xiàn)不同的電阻特性。當(dāng)被加熱時(shí)呈晶體狀,為1狀態(tài);當(dāng)冷卻為非晶體時(shí),為0狀態(tài)。通過改變流過該晶體的電流就可以實(shí)現(xiàn)這兩種狀態(tài)的轉(zhuǎn)換。

圖五 相變存儲材料

(4)阻變式存儲器(RRAM)

RRAM的原理是通過特定的薄膜材料的電阻值在不同電壓下呈現(xiàn)的電阻值不同來區(qū)分0和1的值。RRAM的存儲單元具有簡單的金屬/阻變存儲層/金屬(MIM)三明治結(jié)構(gòu)如圖六所示。

圖六 RRAM器件結(jié)構(gòu)圖

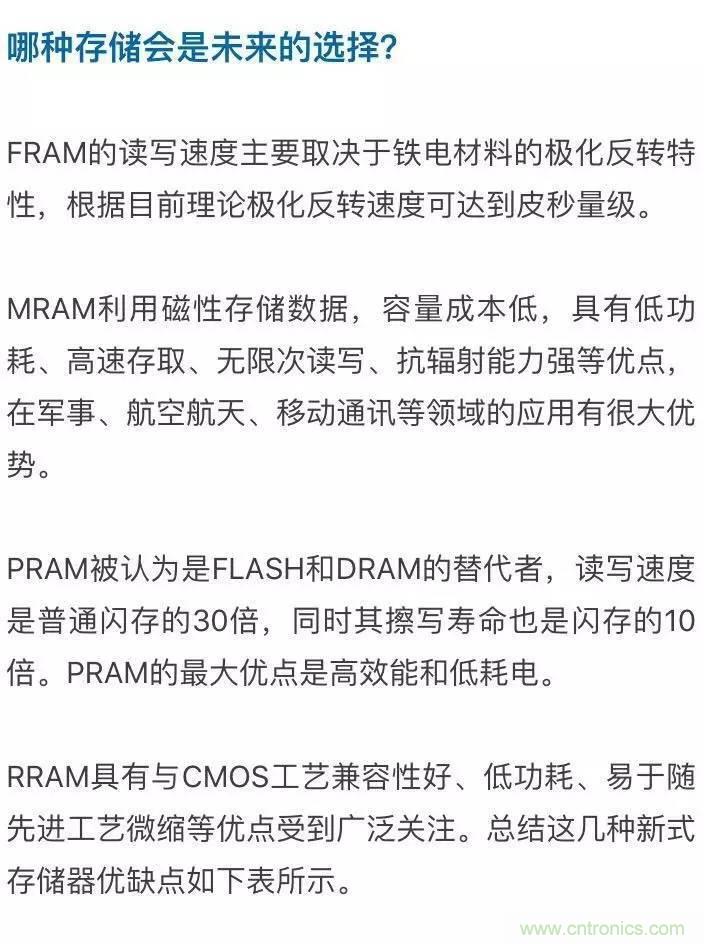

表一 幾種存儲器性能對比

新型存儲器挑戰(zhàn)

FRAM目前作為新型存儲器的主要問題是鐵電薄膜材料。未來發(fā)展需要解決的主要難題:一是采用3D結(jié)構(gòu)縮小單元面積提高集成度;二是提高鐵電薄膜特性。

RRAM還是一項(xiàng)前沿的研究課題,目前還主要停留在實(shí)驗(yàn)室階段。未來材料的尋找仍然是RRAM面臨的主要問題。

而臺積電未來選擇先生產(chǎn)的MRAM和PRAM也會遇到挑戰(zhàn)。MRAM的主要問題在于其高昂的制造成本。其次MRAM依靠磁性存儲材料,磁場會對周圍的芯片產(chǎn)生怎樣的影響需要仔細(xì)考慮。

而PRAM的最大問題是成本和容量。目前PRAM的單位容量成本還是比NAND高不少。發(fā)熱對于PRAM而言是個大問題,由于PRAM需要加熱電阻式材料發(fā)生相變,隨著工藝越來月先進(jìn),單元變得越來越精細(xì),對于加熱元件的控制要求也將越來越高,那發(fā)熱帶來的影響也將加大。發(fā)熱和耗電可能會制約PRAM的進(jìn)一步發(fā)展。

嵌入式存儲器未來

嵌入式存儲器具有大容量集成的優(yōu)勢,是SOC的重要組成部分,具有重要的創(chuàng)新性和實(shí)用性。何種嵌入式存儲器將取得最終的成功,取決于多方面的因素:能否與標(biāo)準(zhǔn)CMOS 工藝兼容,在不斷增加復(fù)雜性的工藝步驟的基礎(chǔ)上,實(shí)現(xiàn)大容量的片上集成,從而提高其性價(jià)比;能否隨著工藝的發(fā)展縮小尺寸,解決超深亞微米工藝的延續(xù)性和擴(kuò)展性問題,這是所有采用電容結(jié)構(gòu)存儲信息的存儲器面對的共同挑戰(zhàn);能否滿足片上其他高速邏輯的帶寬需要,構(gòu)成帶寬均衡、穩(wěn)定簡潔的集成系統(tǒng);準(zhǔn)確的市場定位,保持量產(chǎn)。

總而言之每項(xiàng)技術(shù)的發(fā)展都有其機(jī)會與挑戰(zhàn)。而無懼挑戰(zhàn)勇于創(chuàng)新的企業(yè)最終將贏得市場。

推薦閱讀: