【導(dǎo)讀】在各種應(yīng)用中(從通信基礎(chǔ)設(shè)施到儀器儀表)����,對(duì)系統(tǒng)帶寬和分辨率的更高要求促進(jìn)了將多個(gè)數(shù)據(jù)轉(zhuǎn)換器以陣列形式連接的需求���。設(shè)計(jì)人員必須找到低噪聲、高精度解決方案����,才能為使用普通JESD204B串行數(shù)據(jù)轉(zhuǎn)換器接口的大型數(shù)據(jù)轉(zhuǎn)換器陣列提供時(shí)鐘和同步���。

時(shí)鐘生成器件包含抖動(dòng)衰減功能、內(nèi)部VCO以及各種輸出和很多同步管理功能����,現(xiàn)已問(wèn)世,它能解決這個(gè)系統(tǒng)問(wèn)題�����。然而����,在很多實(shí)際應(yīng)用中��, 數(shù)據(jù)轉(zhuǎn)換器陣列所需的大量時(shí)鐘已經(jīng)超出了單個(gè)IC元件所能提供的極限�����。設(shè)計(jì)人員試圖連接多個(gè)時(shí)鐘生成和時(shí)鐘分配元件�,創(chuàng)建豐富的時(shí)鐘樹(shù)。

本文將提供一個(gè)關(guān)于如何構(gòu)建靈活可編程時(shí)鐘擴(kuò)展網(wǎng)絡(luò)的真實(shí)案例�, 它不僅具有出色的相位噪聲/抖動(dòng)性能���,還可將所需的同步信息從時(shí)鐘樹(shù)的第一個(gè)器件傳遞至最后一個(gè)器件, 同時(shí)提供確定性控制����。

簡(jiǎn)介

無(wú)線(xiàn)通信系統(tǒng)從3G到4G和LTE(以及5G,目前正在規(guī)范討論階段)的演進(jìn)是推動(dòng)高速數(shù)據(jù)轉(zhuǎn)換和同步的關(guān)鍵技術(shù)因素����。在蜂窩基站應(yīng)用中,多種因素共同作用����,提高了數(shù)據(jù)帶寬要求。主要的因素是����,訂閱數(shù)量的增加導(dǎo)致對(duì)更為豐富的多媒體內(nèi)容的需求,以及對(duì)于使用全球蜂窩基礎(chǔ)設(shè)施的機(jī)器間通信的新應(yīng)用需求�����。其結(jié)果是�����,設(shè)計(jì)人員尋求全新的創(chuàng)新型RF收發(fā)器架構(gòu),這種架構(gòu)具有更高的通道數(shù)�����, 使用諸如有源天線(xiàn)設(shè)計(jì)��、大規(guī)模MIMO 和高級(jí)波束成形等技術(shù)�。

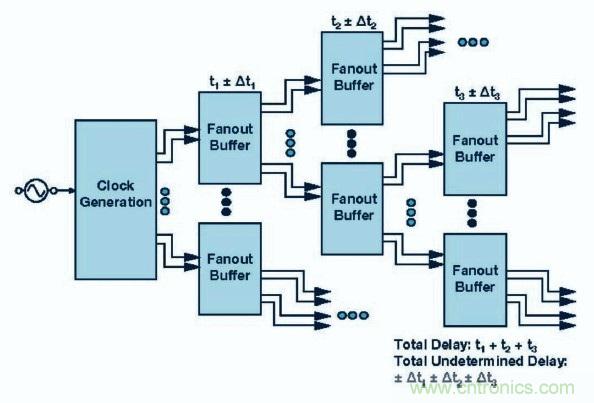

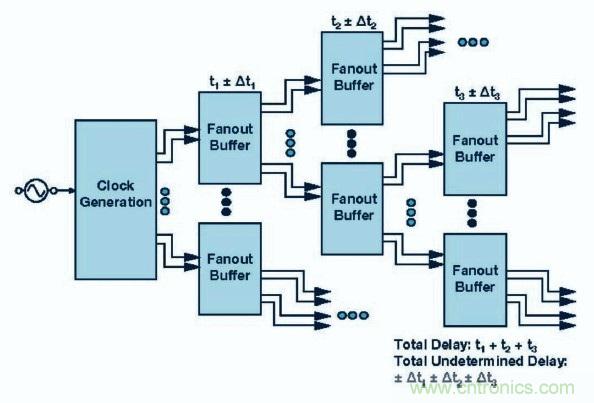

具有大量輸入和輸出的系統(tǒng)利用多條傳輸路徑,需要大量的ADC和DAC元件�。數(shù)據(jù)轉(zhuǎn)換要求擴(kuò)大后, 采樣時(shí)鐘生成和同步就成了很大的設(shè)計(jì)挑戰(zhàn)���。在復(fù)雜系統(tǒng)中����,所需的時(shí)鐘信號(hào)數(shù)量可以輕松從幾個(gè)增加到上百個(gè)�����,如圖1所示�。

JESD204B標(biāo)準(zhǔn)定義了串行數(shù)據(jù)接口����,可用來(lái)減少寬帶數(shù)據(jù)轉(zhuǎn)換器和其它系統(tǒng)IC之間的數(shù)據(jù)輸入/輸出數(shù)量��。數(shù)據(jù)I/O數(shù)量的下降解決了高速���、高位數(shù)數(shù)據(jù)轉(zhuǎn)換器的互連問(wèn)題。以更少的互連提供寬帶數(shù)據(jù)轉(zhuǎn)換器的能力簡(jiǎn)化了PCB布局布線(xiàn)���,實(shí)現(xiàn)了更小的尺寸���,卻不降低整體系統(tǒng)性能。這些改進(jìn)對(duì)于克服大部分應(yīng)用中的系統(tǒng)尺寸和成本限制非常重要�,包括無(wú)線(xiàn)基礎(chǔ)設(shè)施、便攜式儀器儀表�����、軍事應(yīng)用和醫(yī)療超聲設(shè)備���。

圖1:帶時(shí)鐘樹(shù)的數(shù)據(jù)轉(zhuǎn)換器系統(tǒng)

系統(tǒng)級(jí)考慮因素

在含有大型數(shù)據(jù)轉(zhuǎn)換器陣列的復(fù)雜系統(tǒng)中��,處理更大的數(shù)據(jù)量要求從天線(xiàn)到處理單元具有高SNR(信噪比)��。從時(shí)鐘角度來(lái)講�,SNR受限于采樣時(shí)鐘的相位噪聲����。較差的相位噪聲性能會(huì)造成抖動(dòng)并增加EVM(誤差矢量幅度)�, 從而嚴(yán)重降低SNR�,影響系統(tǒng)性能。一般而言���,時(shí)鐘信號(hào)質(zhì)量用抖動(dòng)來(lái)表示����,其定義為目標(biāo)帶寬內(nèi)的相位噪聲積分���。

通常����,相位噪聲積分限值為幾十kHz到幾十MHz�。然而,寬帶噪聲同樣很重要���,因?yàn)檩^高的時(shí)鐘信號(hào)噪底同樣會(huì)影響系統(tǒng)SNR。較差的采樣時(shí)鐘還可能含有雜散信號(hào)內(nèi)容�,會(huì)降低SFDR(無(wú)雜散動(dòng)態(tài)范圍)。最終���,考慮到占空比和上升/下降時(shí)間等參數(shù)��,采樣時(shí)鐘質(zhì)量不應(yīng)僅在頻率域中定義�, 還應(yīng)在時(shí)間域中定義。

這些是采樣時(shí)鐘的基本系統(tǒng)要求���。然而����,在大型數(shù)據(jù)轉(zhuǎn)換器陣列中����,當(dāng)不同陣列的時(shí)鐘之間需要同步時(shí), 通道間偏斜便是一個(gè)關(guān)鍵要求�����。這類(lèi)系統(tǒng)的性能取決于同步數(shù)據(jù)陣列��,因此對(duì)不同數(shù)據(jù)轉(zhuǎn)換器之間的偏斜很敏感��。

功耗也是一個(gè)考慮因素��。較高的功耗降低了系統(tǒng)效率,使溫度升高并增加冷卻成本和引線(xiàn)��,且增加了潛在故障率�����。從商業(yè)角度出發(fā)��,器件數(shù)和電路板空間同樣是很重要的�,應(yīng)加以控制。

時(shí)鐘樹(shù)結(jié)構(gòu)

如前所述�,在一個(gè)大規(guī)模系統(tǒng)中,單個(gè)時(shí)鐘IC通常沒(méi)有足夠的輸出來(lái)驅(qū)動(dòng)所有分支����。時(shí)鐘樹(shù)拓?fù)湟苍S可以克服這個(gè)問(wèn)題,且能同步多個(gè)器件����、設(shè)備,或多個(gè)系統(tǒng)�����。圖2給出了一個(gè)時(shí)鐘樹(shù)拓?fù)淇驁D��。注意���,樹(shù)形結(jié)構(gòu)的每一級(jí)都有延遲成分�����,由固定部分和不確定部分組成�。

這些延遲可能受外界因素的影響�����,比如電壓和溫度變化����,以及特定器件工藝變化。這種不精確性會(huì)疊加���,可能導(dǎo)致ADC和DAC無(wú)法忍受的時(shí)序偏差���,而高頻時(shí)需要對(duì)其時(shí)鐘信號(hào)進(jìn)行同步。現(xiàn)代系統(tǒng)所要求的高工作頻率意味著苛刻的建立和保持時(shí)間�。雖然固定延遲可以通過(guò)其它方面加以補(bǔ)償,但不確定性延遲卻無(wú)法在系統(tǒng)中補(bǔ)償���。因此����,設(shè)計(jì)人員的目標(biāo)便是通過(guò)某種方式控制不確定性延遲,最小化甚至完全消除其影響����。

圖2:時(shí)鐘樹(shù)框圖

除這些限制外,樹(shù)形結(jié)構(gòu)應(yīng)當(dāng)是靈活的����,以便根據(jù)系統(tǒng)需要增加分支數(shù)量,并輕松控制它們�����。

實(shí)現(xiàn)時(shí)鐘對(duì)齊和通道偏斜最小化目標(biāo)的常見(jiàn)做法是使用確定性— 也就是說(shuō)�����,重復(fù)用于所有器件和所有上電時(shí)序�����。在JESD204B系統(tǒng)中�����, 需要對(duì)齊本地多幀時(shí)鐘(LMFC),以實(shí)現(xiàn)確定性延遲�。接口通過(guò)子類(lèi)1(SYSREF)或子類(lèi)2(SYNC)定義調(diào)用發(fā)送和接收器件的LMFC復(fù)位與對(duì)齊�����。系統(tǒng)中的不確定性延遲使得在1 個(gè)LFMC周期內(nèi)實(shí)現(xiàn)LMFC的對(duì)齊變得更為困難��。因此�,前文提到的帶高精度對(duì)齊功能的時(shí)鐘樹(shù)結(jié)構(gòu)可以幫助系統(tǒng)設(shè)計(jì)人員滿(mǎn)足LMFC對(duì)齊要求。

此外���,設(shè)計(jì)人員還需確保在每一個(gè)數(shù)據(jù)轉(zhuǎn)換器輸入端觀(guān)察到相對(duì)于器件時(shí)鐘而言可以接受的SYSREF信號(hào)建立和保持時(shí)間��。如果設(shè)計(jì)中使用了單時(shí)鐘芯片�����,則滿(mǎn)足建立和保持時(shí)間要求直接保證了具有適當(dāng)?shù)臅r(shí)序裕量��,而在基于簡(jiǎn)單時(shí)鐘緩沖器的多器件時(shí)鐘樹(shù)結(jié)構(gòu)中����,控制建立和保持時(shí)間的難度更大。建議的時(shí)鐘樹(shù)結(jié)構(gòu)具有不同層級(jí)之間的確定性同步��,有助于滿(mǎn)足所有層級(jí)的全部SYSREF/器件時(shí)鐘對(duì)建立/保持時(shí)序的要求���。這種時(shí)鐘樹(shù)結(jié)構(gòu)可以滿(mǎn)足同步限制����,并在不同層級(jí)之間實(shí)現(xiàn)每一個(gè)數(shù)據(jù)轉(zhuǎn)換器高速器件時(shí)鐘的相位對(duì)齊����。

時(shí)鐘樹(shù)設(shè)計(jì)

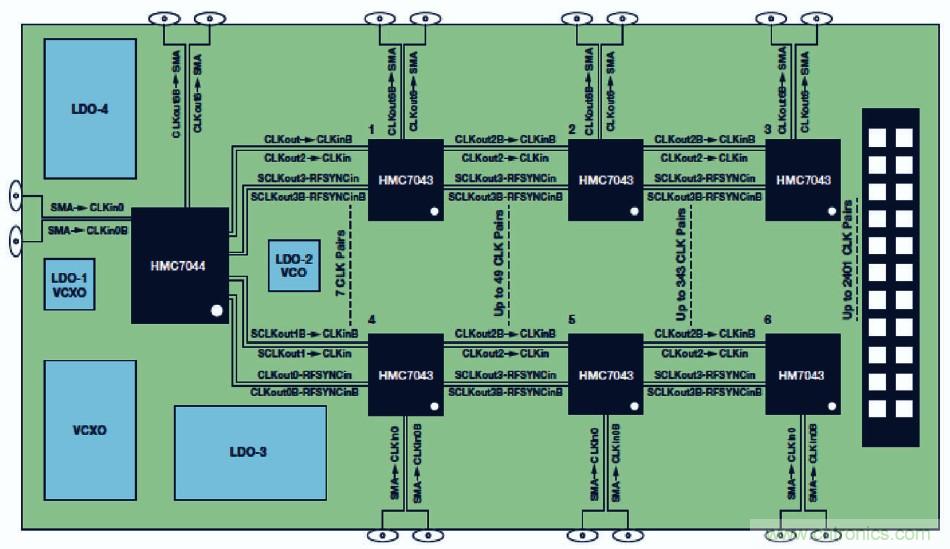

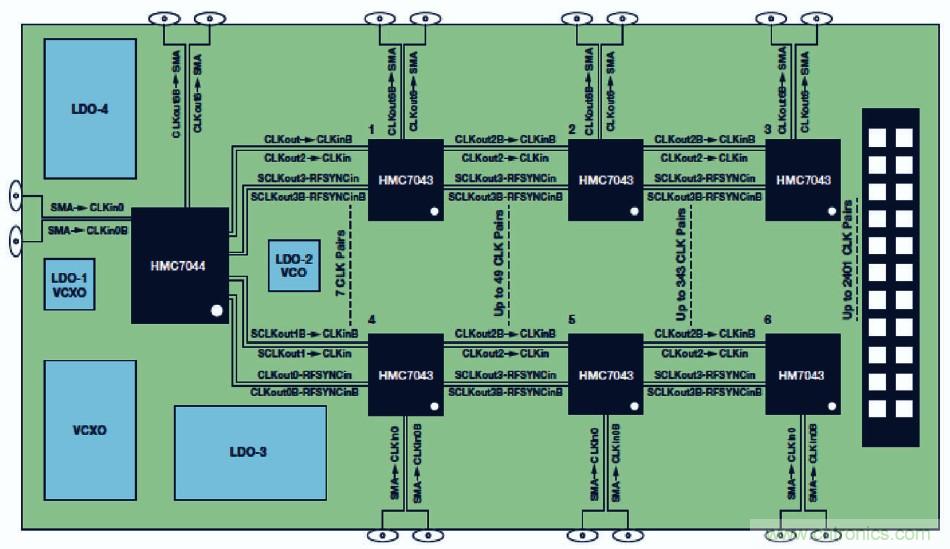

圖3顯示了一個(gè)四級(jí)時(shí)鐘樹(shù)示例,它采用了一個(gè)主時(shí)鐘生成器件(HMC7044)和三級(jí)扇出緩沖器(HMC7043)來(lái)創(chuàng)建多個(gè)同步時(shí)鐘����,用于采樣板。

使用一個(gè)HMC7044器件作為時(shí)鐘樹(shù)的根��;它是一個(gè)14路輸出時(shí)鐘生成器����,抖動(dòng)衰減支持JESD204B同步。HMC7043器件— 14路輸出扇出緩沖器— 用于每一級(jí)分支�����。這些器件完全兼容,它們的編程特性非常相似�,因而可以很方便地進(jìn)行器件匹配以及增加或減少時(shí)鐘分配級(jí),提升了系統(tǒng)的靈活性�����。

在時(shí)鐘樹(shù)的每一級(jí)�,各輸出之間也許可以實(shí)現(xiàn)同步�����。在本系統(tǒng)中�����,HMC7044的輸出可以通過(guò)SPI命令(或者使用更精確的SYNC脈沖)進(jìn)行相位對(duì)齊�����。該命令將復(fù)位HMC7044的通用SYSREF定時(shí)器�����,它控制所有時(shí)鐘的輸出分頻器����。所有輸出時(shí)鐘分頻器均通過(guò)SYSREF定時(shí)器命令同步對(duì)齊�。SYNC命令到SYSREF定時(shí)器的延遲��,以及開(kāi)啟和關(guān)斷時(shí)間之間的延遲非常明確����,并提供輸出之間具有確定性延遲的同步。此外����,可以編程任意輸出,生成確定數(shù)量的脈沖��,用作系統(tǒng)中的SYSREF脈沖�����。

時(shí)鐘分配器件HMC7043還含有非常相似的SYSREF定時(shí)器結(jié)構(gòu)�。該器件利用RFSYNC信號(hào)來(lái)實(shí)現(xiàn)對(duì)齊。RFSYNC脈沖將啟動(dòng)與HMC7044的SYNC信號(hào)相同的過(guò)程�����, 并且所有輸出都將以高精度同步��。同樣,輸出可以設(shè)為脈沖模式�����,用作SYSREF脈沖���。

建議的時(shí)鐘樹(shù)結(jié)構(gòu)基本使用SYSREF信號(hào)作為HMC7043的下一級(jí)RFSYNC信號(hào)�,同時(shí)在每一級(jí)的輸出端保持相位對(duì)齊�。通過(guò)仔細(xì)的架構(gòu)設(shè)計(jì),所有這些時(shí)序信號(hào)都可以是確定性的�,從而具有嚴(yán)格的偏斜控制�����。此外�,每個(gè)器件都包含一個(gè)模擬延遲結(jié)構(gòu),因此輸出之間的任何偏斜差異或任何線(xiàn)路長(zhǎng)度的不相等都可以在源頭進(jìn)行補(bǔ)償��。

圖3:四級(jí)時(shí)鐘樹(shù)示例

對(duì)于RF系統(tǒng)中的復(fù)雜數(shù)據(jù)轉(zhuǎn)換器陣列而言��,可能需要使用不同的頻率����,因?yàn)锳DC�、DAC���、FPGA�、本振和混頻器可能采用不同頻率的時(shí)鐘信號(hào)�����。HMC7044和HMC7043都集成了分頻器�,可生成多種頻率的信號(hào)。另外����,HMC7044具有雙PLL結(jié)構(gòu),集成VCO����,無(wú)需額外元件即可生成高頻時(shí)鐘。

常見(jiàn)通信系統(tǒng)的額外復(fù)雜性在于�,大部分RF前端元件依賴(lài)串行接口連接到發(fā)送/接收模塊,要求數(shù)據(jù)和時(shí)鐘通過(guò)數(shù)字處理器或FPGA來(lái)嵌入/消除�。這個(gè)過(guò)程通常會(huì)產(chǎn)生干擾基準(zhǔn)時(shí)鐘抖動(dòng),要求在較大的RF時(shí)鐘生成和分配器件中集成抖動(dòng)衰減能力�����,比如HMC7044。

測(cè)試結(jié)果

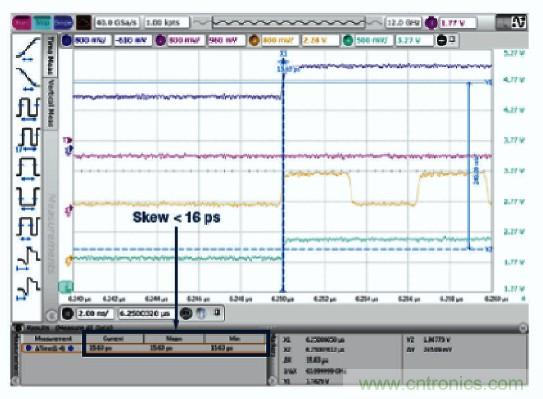

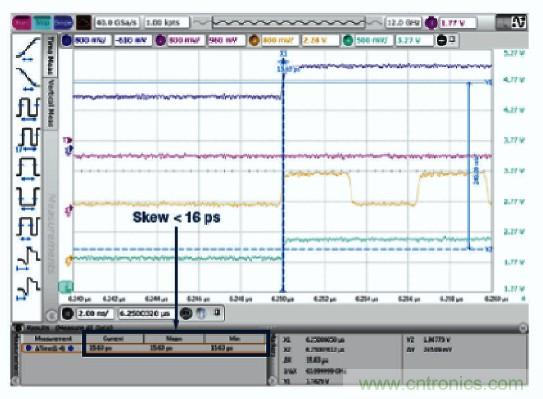

圖4顯示了所有輸出之間的偏斜���。黃線(xiàn)和青線(xiàn)信號(hào)是脈沖SYSREF信號(hào)和第4級(jí)輸出的連續(xù)時(shí)鐘信號(hào)��,它們無(wú)需額外的延遲調(diào)節(jié)即可同步���。藍(lán)線(xiàn)信號(hào)是HMC7044的連續(xù)SYSREF信號(hào),它通過(guò)模擬延遲功能與第4級(jí)輸出同步�。本例中的總偏斜低于16ps。

圖4:四級(jí)輸出的時(shí)間域響應(yīng)

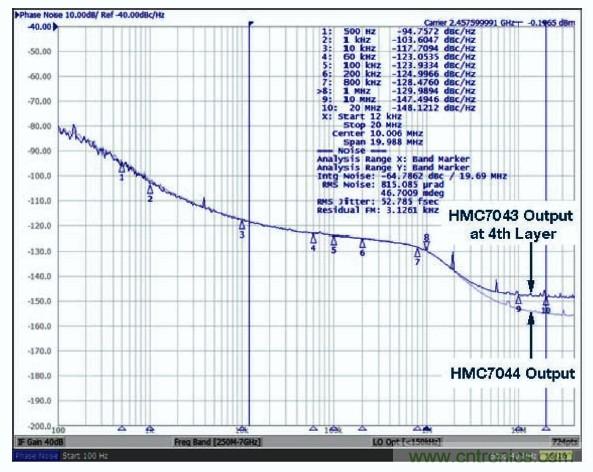

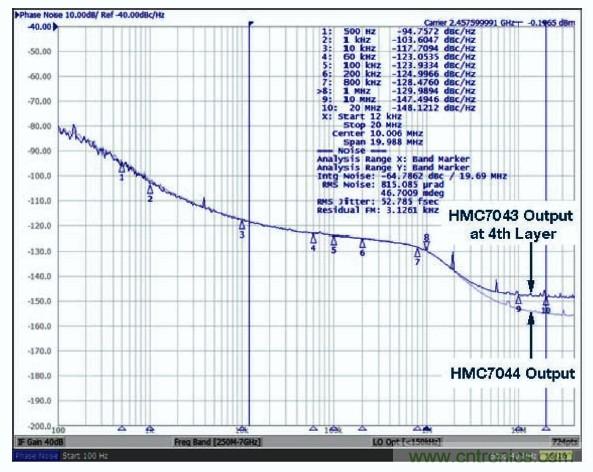

圖5顯示了四級(jí)時(shí)鐘樹(shù)的相位噪聲性能����。時(shí)鐘發(fā)生器的相位噪聲同樣以淺藍(lán)色線(xiàn)表示?�?傁辔辉肼曉诟哌_(dá)2MHz失調(diào)范圍內(nèi)無(wú)下降�。給定每一級(jí)的加性噪聲( 加性抖動(dòng))�, 則噪底性能不可避免地會(huì)下降,且在圖中的這一部分可以看出噪聲增加了6dB�。HMC7044和HMC7043具有相同的輸出噪底(約為154dBc/Hz),并且全部四個(gè)器件的噪聲下降至148dBc/Hz���,這對(duì)于大多數(shù)系統(tǒng)而言仍然可以接受���。

2457.6MHz時(shí)�����,12kHz到20MHz的積分噪聲計(jì)算得到52.7fs抖動(dòng)rms�, 相對(duì)于HMC7044輸出僅下降了數(shù)fs rms�。在幾乎所有的實(shí)際系統(tǒng)中,這種性能下降是可以忍受的���;但是如果不能接受的話(huà)�,那么最終級(jí)可以用HMC7044來(lái)代替(而不是HMC7043)���,它可以衰減時(shí)鐘樹(shù)本身的一切累積抖動(dòng)�����。

圖5:四級(jí)輸出的時(shí)間域響應(yīng)

如前所述�����,在大量使用數(shù)據(jù)轉(zhuǎn)換器的系統(tǒng)中�,功耗是最關(guān)鍵的問(wèn)題之一。影響這類(lèi)時(shí)鐘樹(shù)功耗的一個(gè)重要因素是使用的信號(hào)類(lèi)型����。HMC7044和HMC7043的輸出信號(hào)模式可以通過(guò)軟件控制單獨(dú)更改,從而提供了功耗與驅(qū)動(dòng)強(qiáng)度及頻率之間的權(quán)衡選擇���。原則上��,低頻時(shí)可以使用低功耗LVDS�, 而高頻時(shí)使用LVPECL和CML可以實(shí)現(xiàn)最佳性能��。

結(jié)論

本文中的討論適用于采用分布式大型數(shù)據(jù)轉(zhuǎn)換器陣列的各種不同系統(tǒng)�����,范圍涉及無(wú)線(xiàn)基礎(chǔ)設(shè)施��、軍用雷達(dá)以及測(cè)試與測(cè)量系統(tǒng)��。最近5G通信系統(tǒng)提出的更高頻率和帶寬調(diào)制方案的基礎(chǔ)是多RF輸入/輸出接口的當(dāng)前趨勢(shì)���, 需要更多的數(shù)據(jù)轉(zhuǎn)換通道。此外��,在某些最新的5G架構(gòu)方案中,相位陣列天線(xiàn)出現(xiàn)的頻率很高��,它是降低功耗����、提升輸出容量的一種途徑。

相位陣列技術(shù)廣泛用于軍事通信系統(tǒng)中���,這項(xiàng)技術(shù)不僅需要大量時(shí)鐘����, 還需要對(duì)這些時(shí)鐘進(jìn)行精確同步���。

大型數(shù)據(jù)轉(zhuǎn)換器陣列的另一個(gè)重要使用場(chǎng)景是測(cè)試與測(cè)量系統(tǒng)���,這類(lèi)系統(tǒng)要求以高采樣速率捕獲大量數(shù)據(jù)、引入的噪聲盡可能低�����,并要求同步處理�。這些系統(tǒng)同樣需要大量的同步時(shí)鐘。類(lèi)似地�,在高級(jí)醫(yī)療成像系統(tǒng)中�,數(shù)據(jù)處理吞吐速率非常高���,且要求并行數(shù)據(jù)采集路徑能同步操作��。

正如本文所指出的�,IC公司正在推出創(chuàng)新和實(shí)用的解決方案��,以便實(shí)現(xiàn)這些高級(jí)設(shè)計(jì)��。HMC7044和HMC7043等元件的設(shè)計(jì)考慮到了系統(tǒng)挑戰(zhàn)���,它們旨在構(gòu)建高性能和靈活的時(shí)鐘樹(shù)���,同時(shí)在多級(jí)時(shí)鐘擴(kuò)展中保持確定性相位精度。

作者:Kazim Peker�����,Altug Oz����,ADI公司

本文來(lái)源于A(yíng)DI。

推薦閱讀: