【導(dǎo)讀】許多現(xiàn)代工業(yè)和儀器儀表系統(tǒng)可以接入多個(gè)不同電源,最常見的是15 V用于模擬電路,3 V或5 V用于數(shù)字邏輯。其中大部分應(yīng)用要求輸出以10 V擺幅驅(qū)動(dòng)外部大負(fù)載。本文討論為這些應(yīng)用選擇數(shù)模轉(zhuǎn)換器(DAC)時(shí)遇到的各種權(quán)衡因素,并且提出了詳細(xì)的電路原理圖。

電路描述

許多現(xiàn)代工業(yè)和儀器儀表系統(tǒng)可以接入多個(gè)不同電源,最常見的是15 V用于模擬電路,3 V或5 V用于數(shù)字邏輯。其中大部分應(yīng)用要求輸出以10 V擺幅驅(qū)動(dòng)外部大負(fù)載。本文討論為這些應(yīng)用選擇數(shù)模轉(zhuǎn)換器(DAC)時(shí)遇到的各種權(quán)衡因素,并且提出了詳細(xì)的電路原理圖。

可編程邏輯控制器(PLC)、過程控制或電機(jī)控制等工業(yè)應(yīng)用中的模擬輸出系統(tǒng),需要0 V至10 V或10 V以上的單極性或雙極性電壓擺幅。一種可能的解決方案是選擇能夠直接產(chǎn)生所需輸出電壓的雙極性輸出DAC。還有一種解決方案是使用低壓單電源(LVSS)DAC,將其輸出電壓放大至所需輸出電平。為了選擇最適合應(yīng)用的方法,用戶必須了解輸出要求,并且知道每種方案的優(yōu)勢或不足。

能夠直接產(chǎn)生所需輸出擺幅的雙極性DAC具有多項(xiàng)值得考慮的優(yōu)勢和不足。主要優(yōu)勢包括:

* 簡單。電路板的設(shè)計(jì)得以簡化,因?yàn)樗璧? V至10 V或10 V以上輸出電平可直接通過硬件或軟件配置獲得。此外,其通常會(huì)集成故障保護(hù)模式,因而可簡化系統(tǒng)設(shè)計(jì)。

* 可制造性和可靠性得到提高,因?yàn)椴恍枰糯笃?、開關(guān)和電阻等分立式器件。有時(shí)也會(huì)集成基準(zhǔn)電壓源。

* 系統(tǒng)誤差和總非調(diào)整誤差(TUE)的測量。保證線性度、噪聲、失調(diào)和漂移特性;對DAC內(nèi)的各種誤差源求和,很容易計(jì)算總系統(tǒng)誤差或TUE。TUE有時(shí)在數(shù)據(jù)手冊中有規(guī)定。

* 端點(diǎn)誤差。某些情況下,雙極性DAC包括校準(zhǔn)特性,能夠隨時(shí)調(diào)整系統(tǒng)失調(diào)和增益誤差。

雙極性DAC的主要缺點(diǎn)包括:

* 靈活性有限。集成高壓放大器對應(yīng)用而言可能不是最佳的。輸出放大器通常針對特定負(fù)載和噪聲要求進(jìn)行優(yōu)化。雖然數(shù)據(jù)手冊給出的范圍可能與系統(tǒng)中的實(shí)際負(fù)載匹配,但其他參數(shù)(如建立時(shí)間或功耗等)可能無法滿足系統(tǒng)要求。

* 成本和電路板面積。雙極性DAC通常是在較大的幾何工藝上設(shè)計(jì),導(dǎo)致芯片和封裝尺寸較大且成本較高。

使用帶外部信號(hào)調(diào)理的低壓DAC是另一種產(chǎn)生工業(yè)應(yīng)用所需高壓輸出擺幅和范圍的方法。同樣,它也有值得考慮的重要權(quán)衡因素。分立式解決方案的主要優(yōu)勢包括:

* LVSS DAC往往具有較高的邏輯集成度和高速邏輯接口,使得微控制器有時(shí)間來處理更多任務(wù)。

* 輸出可能必須提供大電流或驅(qū)動(dòng)雙極性DAC片內(nèi)放大器無法處理的大容性負(fù)載。分立式解決方案允許選擇最佳獨(dú)立放大器來滿足應(yīng)用需要。

* 很容易實(shí)現(xiàn)超量程特性(10 V標(biāo)稱范圍提供10.8 V輸出),為最終用戶提供更大的應(yīng)用靈活性,例如在需要打開或關(guān)閉磨損閥門的應(yīng)用中。

* 成本。LVSS DAC通常比雙極性DAC便宜,從而使總體物料成本更低。

* 減少電路板面積。LVSS DAC采用低壓亞微米或深微米工藝設(shè)計(jì),可提供小尺寸封裝。

分立式解決方案的主要缺點(diǎn)包括:

* 需要花費(fèi)更多的時(shí)間來優(yōu)化電路板和設(shè)計(jì)端點(diǎn)調(diào)整電路。

* 總誤差或TUE的計(jì)算變得更困難,因?yàn)楸仨毧紤]更多誤差源。

* 分立式器件數(shù)量的增加導(dǎo)致可制造性和可靠性降低。

* 應(yīng)用必須有低壓電源(5 V或3 V)可用。

總之,在精密10 V工業(yè)應(yīng)用的設(shè)計(jì)中,有許多因素需要考慮。顯然,設(shè)計(jì)人員必須清楚地知道輸出負(fù)載要求和系統(tǒng)可以接受的總誤差。此外,電路板面積和成本也是選擇最佳方案的重要考慮因素。對于必須驅(qū)動(dòng)大容性負(fù)載(1 μF),同時(shí)要求低噪聲和快速建立(20 V范圍小于10 s)的應(yīng)用,分立式方案幾乎總是勝出。雖然雙極性DAC在靈活性上不如分立式方案,但簡單的設(shè)計(jì)和不費(fèi)力的TUE計(jì)算使其對廣泛的工業(yè)和儀器儀表應(yīng)用很有吸引力。

下面的討論說明如何利用雙電源雙極性輸出DAC和帶外部信號(hào)調(diào)理的低壓單電源DAC實(shí)現(xiàn)精密10 V輸出。

電路概覽:雙電源雙極性輸出DAC

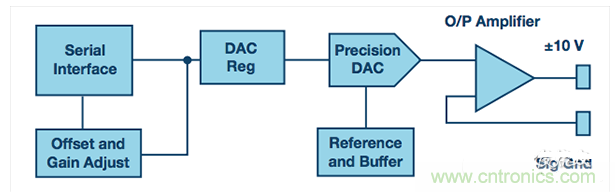

圖1. AD5764雙極性DAC的功能框圖

雙極性輸出DAC的主要元件如以上功能框圖(圖1)所示。它由精密DAC、基準(zhǔn)電壓源、基準(zhǔn)電壓緩沖器、失調(diào)和增益調(diào)整以及輸出放大器組成。集成精密基準(zhǔn)電壓源以適應(yīng)16位應(yīng)用非常困難,但最近的工藝進(jìn)步和設(shè)計(jì)技術(shù)允許在片內(nèi)設(shè)計(jì)和集成具有出色漂移和熱特性的基準(zhǔn)電壓源。熱關(guān)斷、短路保護(hù)等故障保護(hù)模式,以及上電/關(guān)斷等狀況下的輸出控制,是雙極性DAC通常會(huì)集成的重要特性,可以簡化系統(tǒng)設(shè)計(jì)。DAC提供數(shù)字碼以相對于基準(zhǔn)電壓轉(zhuǎn)換輸出電壓。調(diào)整模塊提供偏移和調(diào)整DAC傳遞函數(shù)的功能。

有關(guān)AD5764的更多信息

AD5764是一款四通道、16位串行輸入、電壓輸出DAC,工作電壓范圍為12 V至15 V。其標(biāo)稱滿量程輸出范圍為10 V,內(nèi)置輸出放大器、基準(zhǔn)電壓緩沖器、精密基準(zhǔn)電壓源以及專有上電/關(guān)斷控制電路。AD5764采用ADI公司的工業(yè)CMOS (iCMOS?)制造工藝技術(shù)設(shè)計(jì),該工藝集高壓互補(bǔ)雙極性晶體管和亞微米CMOS于一體。它還有一個(gè)模擬溫度傳感器,每通道均有對應(yīng)的數(shù)字失調(diào)和增益調(diào)整寄存器。

電路概覽:低壓單電源DAC和外部信號(hào)調(diào)理

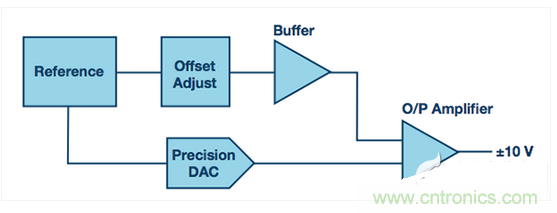

圖2顯示如何利用LVSS DAC產(chǎn)生工業(yè)應(yīng)用所需的10 V輸出范圍。它由5個(gè)不同的模塊組成:LVSS DAC、基準(zhǔn)電壓源、失調(diào)調(diào)整、基準(zhǔn)電壓緩沖器和輸出放大器。

圖2. 分立式±10 V模擬輸出框圖

DAC提供數(shù)字碼以相對于基準(zhǔn)電壓轉(zhuǎn)換輸出電壓。失調(diào)調(diào)整模塊提供偏移DAC單極性傳遞函數(shù)以產(chǎn)生雙極性輸出的功能,以及校準(zhǔn)0 V端點(diǎn)的功能?;鶞?zhǔn)電壓緩沖器為基準(zhǔn)電壓和失調(diào)調(diào)整模塊提供負(fù)載隔離(多個(gè)DAC可共用這一緩沖輸出)。輸出放大器在計(jì)入失調(diào)調(diào)整后,提供所需的增益來將輸出擺幅提高到所需電平。此外,輸出放大器還提供將大容性負(fù)載驅(qū)動(dòng)到供電軌的功能。

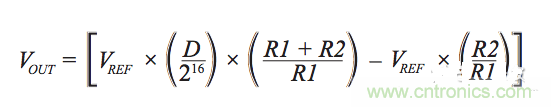

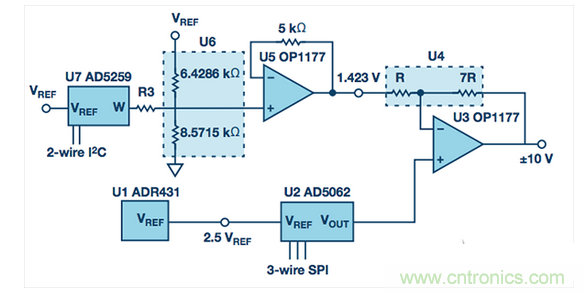

圖3所示電路說明了如何放大一個(gè)精密LVSS 16位DAC來實(shí)現(xiàn)10 V的輸出擺幅。DAC具有0到2.5 V輸出范圍,連接到放大器U3的同相輸入端。此輸入的同相增益為(1 + R2/R1),本例中為8。運(yùn)算放大器的反相輸入端連接到基準(zhǔn)電壓源和電阻分壓器網(wǎng)絡(luò)U6產(chǎn)生的1.429 V電壓。此輸入的反相增益為(–R2/R1),本例中為–7。因此,當(dāng)DAC設(shè)為0代碼0000h時(shí),此電路的輸出為:

(0/65535 2.5 8) – (7 1.429 V) = –10 V.

當(dāng)DAC設(shè)置為滿量程代碼FFFFh時(shí),輸出為:

(65535/65535 2.5 8) – (7 1.429 V) = +10 V.

一般而言,任意輸入代碼的輸出電壓可以按如下公式計(jì)算:

其中D代表精密16位DAC(如同本例)的十進(jìn)制輸入代碼(0至65535)。VREF = 2.5 V,R1 = R,R2 = 7 R。利用一個(gè)帶非易失性存儲(chǔ)器的數(shù)字電位計(jì)來調(diào)整系統(tǒng)的零失調(diào)誤差,這樣即使斷電也能保留失調(diào)值??梢赃x擇U7、U6和R3來形成電阻網(wǎng)絡(luò),以便提供0 V所需的調(diào)整范圍??梢暂p松進(jìn)行配置PLC模擬輸出模塊所需的其他輸出范圍,例如+5 V、5 V、+10 V或10.8 V (適用于超量程較為重要的情況)。

圖 3. 10 V精密模擬輸出電路詳情

該電路包括如下器件:U1—ADR421,精密、低噪聲2.5 V基準(zhǔn)電壓源,3 ppm/°C漂移,MSOP封裝;U2—AD5062,16位、最大1 LSBINL、5 V/3 V電源、串行輸入nanoDAC?,SOT-23封裝;U3和U5—OP1177,精密運(yùn)算放大器,15 V電源,MSOP封裝;U4和U6—帶ESD保護(hù)的精密電阻網(wǎng)絡(luò);U7—AD5259,256抽頭非易失性數(shù)字電位計(jì),MSOP封裝。

有關(guān)AD5062的更多信息16位AD5062保證單調(diào)性,最大DNL和INL誤差為1 LSB。其單極性輸出的最大失調(diào)誤差為50 V,最大增益誤差為0.02%。高速串行接口支持高達(dá)30 MHz的時(shí)鐘速率。 該器件采用SOT-23小型封裝。

結(jié)論

越來越多的工業(yè)和儀表應(yīng)用要求使用精密轉(zhuǎn)換器來實(shí)現(xiàn)各種工藝的精確控制與測量。此外,這些最終應(yīng)用還要求更高的靈活性、可靠性和功能集,同時(shí)降低成本和電路板面積。元件制造商正在解決這些難題,并推出了一系列產(chǎn)品來滿足系統(tǒng)設(shè)計(jì)人員對當(dāng)前與未來設(shè)計(jì)的要求。

如本文所述,有多種途徑可選擇合適的元件用于精密應(yīng)用,每一種都各有優(yōu)缺點(diǎn)。隨著系統(tǒng)精度的提高,人們需要更加注重合適元件的選擇,以滿足應(yīng)用要求。