【導(dǎo)讀】電磁兼容性(EMC)是指設(shè)備或系統(tǒng)在其電磁環(huán)境中符合要求運行并不對其環(huán)境中的任何設(shè)備產(chǎn)生無法忍受的電磁干擾的能力�����。

什么是電磁兼容

電磁兼容性(EMC)是指設(shè)備或系統(tǒng)在其電磁環(huán)境中符合要求運行并不對其環(huán)境中的任何設(shè)備產(chǎn)生無法忍受的電磁干擾的能力���。因此,EMC包括兩個方面的要求:一方面是指設(shè)備在正常運行過程中對所在環(huán)境產(chǎn)生的電磁干擾不能超過一定的限值�;另一方面是指器具對所在環(huán)境中存在的電磁干擾具有一定程度的抗擾度,即電磁敏感性����。

電磁兼容的主要研究對象

①各種人為噪聲,如輸電線電暈噪聲��、汽車噪聲�、接觸器自身噪聲及導(dǎo)體開臺時放電引起的噪聲、電氣機車噪聲�、城市噪聲等��。

②共用走廊內(nèi)各種公用事業(yè)設(shè)備(輸電線��、通信���、鐵路、公路、石油金屬管線等)相互間的影響����。

③超高層建筑�����、輸電線、鐵塔等大型建筑物引起的反射問題����。

④電磁環(huán)境對人類及各種生物的作用。其中包括強電線等工頻場���,中��、短波及微波電磁輻射的影響�����。

⑤核電磁脈沖的影響�����。高空核爆炸產(chǎn)生的電磁脈沖能大面積破壞地面上的指揮�����、控制�、通信����、計算機及報系統(tǒng)。

⑥探譜(TEMPEST)技術(shù)�。其實質(zhì)內(nèi)容是針對信息設(shè)備的電磁輻射與信息泄漏問題�����,從信息接收和防護(hù)兩方面所開展的一系列研究工作���。

⑦電子設(shè)備的誤動作。為了防止誤動作��,必須采取措施以提高設(shè)備的抗干擾能力���。

⑧頻譜分配與管理����。無線電頻譜是一種有限的資源��,但不是消耗性的���,既要科學(xué)地管理�,又要充分地利用��。

⑨電磁兼容與測量�����。

⑩自然界影響等�����。

提高電磁兼容性的措施

①使用完善的屏蔽體可防止外部輻射進(jìn)入本系統(tǒng)����,也可防止本系統(tǒng)的干擾能量向外輻射。屏蔽體應(yīng)保持完整性�����,對必不可少的門����、縫、通風(fēng)孔和電纜孔等須妥善處理�,屏蔽體要有可靠的接地。

②設(shè)計合理的接地系統(tǒng)��,小信號����、大信號和產(chǎn)生干擾的電路盡量分開接地,接地電阻盡可能小���。

③使用合適的濾波技術(shù),濾波器的通帶經(jīng)過合理選擇,盡量減小漏電損耗��。

④使用限幅技術(shù),限幅電平應(yīng)高于工作電平����,并且應(yīng)雙向限幅。

⑤正確選用連接電纜和布線方式��,必要時可用光纜代替長電纜����。

⑥采用平衡差動電路、整形電路�����、積分電路和選通電路等技術(shù)����,

⑦系統(tǒng)頻率分配要恰當(dāng)。當(dāng)一個系統(tǒng)中有多個主頻信號工作時���,盡量使各信號頻率避開���,甚至避開對方的諧振頻率。

⑧共用走廊的各種設(shè)備����,在條件許可時,應(yīng)保持較大的隔距�����,以減輕相互之間的影響�����。

電磁兼容性設(shè)計的基本原理

1.接地

接地是電子設(shè)備的一個很重要問題��。接地目的有三個:

(1)接地使整個電路系統(tǒng)中的所有單元電路都有一個公共的參考零電位��,保證電路系統(tǒng)能穩(wěn)定地干作�。

(2)防止外界電磁場的干擾�。機殼接地可以使得由于靜電感應(yīng)而積累在機殼上的大量電荷通過大地泄放,否則這些電荷形成的高壓可能引起設(shè)備內(nèi)部的火花放電而造成干擾��。另外�����,對于電路的屏蔽體�,若選擇合適的接地,也可獲得良好的屏蔽效果�。

(3)保證安全工作。當(dāng)發(fā)生直接雷電的電磁感應(yīng)時���,可避免電子設(shè)備的毀壞�;當(dāng)工頻交流電源的輸入電壓因絕緣不良或其它原因直接與機殼相通時�,可避免操作人員的觸電事故發(fā)生。此外�,很多醫(yī)療設(shè)備都與病人的人體直接相連�,當(dāng)機殼帶有110V或220V電壓時,將發(fā)生致命危險��。

因此��,接地是抑制噪聲防止干擾的主要方法����。接地可以理解為一個等電位點或等電位面,是電路或系統(tǒng)的基準(zhǔn)電位��,但不一定為大地電位���。為了防止雷擊可能造成的損壞和工作人員的人身安全��,電子設(shè)備的機殼和機房的金屬構(gòu)件等����,必須與大地相連接,而且接地電阻一般要很小��,不能超過規(guī)定值����。

電路的接地方式基本上有三類�����,即單點接地����、多點接地和混合接地。單點接地是指在一個線路中,只有一個物理點被定義為接地參考點���。其它各個需要接地的點都直接接到這一點上�����。多點接地是指某一個系統(tǒng)中各個接地點都直接接到距它最近的接地平面上,以使接地引線的長度最短�����。接地平面��,可以是設(shè)備的底板���,也可以是貫通整個系統(tǒng)的地導(dǎo)線,在比較大的系統(tǒng)中�,還可以是設(shè)備的結(jié)構(gòu)框架等等。

混合接地是將那些只需高頻接地點����,利用旁路電容和接地平面連接起來����。但應(yīng)盡量防止出現(xiàn)旁路電容和引線電感構(gòu)成的諧振現(xiàn)象����。

2.屏面

屏蔽就是對兩個空間區(qū)域之間進(jìn)行金屬的隔離���,以控制電場、磁場和電磁波由一個區(qū)域?qū)α硪粋€區(qū)域的感應(yīng)和輻射����。具體講�,就是用屏蔽體將元部件、電路�、組合件����、電纜或整個系統(tǒng)的干擾源包圍起來,防止干擾電磁場向外擴散��;用屏蔽體將接收電路�����、設(shè)備或系統(tǒng)包圍起來�,防止它們受到外界電磁場的影響。

因為屏蔽體對來自導(dǎo)線����、電纜、元部件���、電路或系統(tǒng)等外部的干擾電磁波和內(nèi)部電磁波均起著吸收能量(渦流損耗)、反射能量(電磁波在屏蔽體上的界面反射)和抵消能量(電磁感應(yīng)在屏蔽層上產(chǎn)生反向電磁場�,可抵消部分干擾電磁波)的作用,所以屏蔽體具有減弱干擾的功能���。

屏蔽體材料選擇的原則是:

(1)當(dāng)干擾電磁場的頻率較高時,利用低電阻率(高電導(dǎo)率)的金屬材料中產(chǎn)生的渦流(P=I2R�����,電阻率越低(電導(dǎo)率越高)�,消耗的功率越大),形成對外來電磁波的抵消作用�����,從而達(dá)到屏蔽的效果�����。

(2)當(dāng)干擾電磁波的頻率較低時�����,要采用高導(dǎo)磁率的材料�����,從而使磁力線限制在屏蔽體內(nèi)部�,防止擴散到屏蔽的空間去�。

(3)在某些場合下�,如果要求對高頻和低頻電磁場都具有良好的屏蔽效果時,往往采用不同的金屬材料組成多層屏蔽體����。

3.其它抑制干擾方法

(1)濾波

濾波是抑制和防止干擾的一項重要措施�����。

濾波器可以顯著地減小傳導(dǎo)干擾的電平,因為干擾頻譜成份不等于有用信號的頻率�,濾波器對于這些與有用信號頻率不同的成份有良好的抑制能力��,從而起到其它干擾抑制難以起到的作用�����。所以��,采用濾波網(wǎng)絡(luò)無論是抑制干擾源和消除干擾耦合�,或是增強接收設(shè)備的抗干擾能力��,都是有力措施��。用阻容和感容去耦網(wǎng)絡(luò)能把電路與電源隔離開�,消除電路之間的耦合����,并避免干擾信號進(jìn)入電路。對高頻電路可采用兩個電容器和一個電感器(高頻扼流圈)組成的CLCMπ型濾波器��。濾波器的種類很多�,選擇適當(dāng)?shù)臑V波器能消除不希望的耦合。

(2)正確選用無源元件

實用的無源元件并不是“理想”的�����,其特性與理想的特性是有差異的���。實用的元件本身可能就是一個干擾源���,因此正確選用無源元件非常重要��。有時也可以利用元件具有的特性進(jìn)行抑制和防止干擾����。

(3)電路技術(shù)

有時候采用屏蔽后仍不能滿足抑制和防止干擾的要求,可以結(jié)合屏蔽���,采取平衡措施等電路技術(shù)。平衡電路是指雙線電路中的兩根導(dǎo)線與連接到這兩根導(dǎo)線的所有電路�,對地或?qū)ζ渌鼘?dǎo)線都具有相同的阻抗���。其目的在于使兩根導(dǎo)線所檢拾到的干擾信號相等��。這時的干擾噪聲是一個共態(tài)信號�����,可在負(fù)載上自行消失�。另外�,還可采用其它一些電路技術(shù),例如接點網(wǎng)絡(luò)���,整形電路,積分電路和選通電路等等����。總之�����,采用電路技術(shù)也是抑制和防止干擾的重要措施���。

1、電磁兼容的分層設(shè)計原則

這主要是按照電磁兼容設(shè)計的先后順序來考慮的,從先到后可分為以下幾層:

(1)元器件的選擇和PCB設(shè)計�����,這是關(guān)鍵的�;

(2)接地設(shè)計,這是主要的手段��。以上兩層如果設(shè)計的好��,可完成電磁兼容的80%以上的工作��。

(3)屏蔽設(shè)計���;

(4)濾波設(shè)計和瞬態(tài)騷擾抑制��。以上兩層是輔助手段���,多為事后補救措施��,也是我們最不提倡的�。

(5)可根據(jù)實際電路需要,結(jié)合以上幾層來綜合設(shè)計�����。

2、保證電磁兼容的方法

主要根據(jù)構(gòu)成干擾的三要素從下幾方面來保證電磁兼容��。

2.1在不同等級上保證電磁兼容

1)從元器件級上來說�����,當(dāng)是無源元件時����,考慮

(1)工作頻帶以外的元件參數(shù)與工作頻帶上的有很大的區(qū)別�����;

(2)插件元件的末端引線有電感存在���,當(dāng)高頻時這個電感易發(fā)生電磁兼容問題;

(3)元件有寄生電容����,寄生電感,在電路上表現(xiàn)為分布參數(shù),在分析電路時也要考慮由它帶來的等效電路��。當(dāng)是有源元件時����,工作中產(chǎn)生的電磁輻射也會以傳導(dǎo)電流的方式成為干擾源���,當(dāng)是非線性元件時還可能發(fā)生頻譜成分的變化�,這種變化也會引起干擾�����。

2)從設(shè)備級上來說�����,主要是保證減少對敏感設(shè)備的耦合�,可考慮

(1)增加脈沖前沿時間以減少干擾的頻寬�;

(2)消除電路中震蕩器產(chǎn)生的諧波及信號的諧波���;

(3)限制干擾輻射或消除干擾的傳播途徑�����。

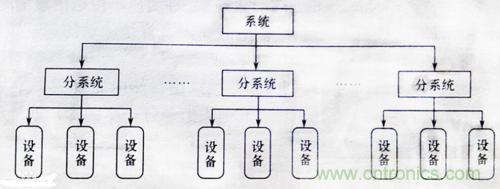

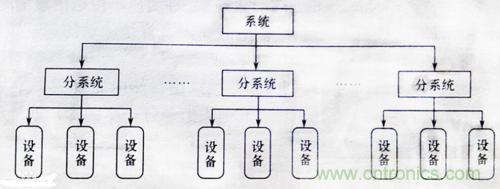

3)從系統(tǒng)級上來說��,主要是靠組織或系統(tǒng)工程的方法來保證�,因為有可能在單個設(shè)備上的電磁兼容得到了改善����,但同時卻影響了其它設(shè)備的工作條件����,使得其它設(shè)備的性能指標(biāo)變壞,此時需要從系統(tǒng)上折中考慮�,另外�����,重要的一點是電磁兼容設(shè)計必須得到系統(tǒng)總體設(shè)計的高度重視����。

2.2減小導(dǎo)線之間的耦合

主要是從增大導(dǎo)線之間的距離,使用屏蔽�����,使用雙絞線或使用屏蔽加雙絞這幾個方面來考慮�����。

2.3接地

主要應(yīng)考慮

(1)接地導(dǎo)線及公共線的阻抗應(yīng)最小�����,最好小于產(chǎn)品最高工作頻率的λ/20以內(nèi)���;

(2)接地導(dǎo)線應(yīng)采用橫截面為管形的接地線�����;

(3)可靠接地,并防止連接點形成氧化層����;

(4)使用一點并聯(lián)接地(低頻用)或者多點接地(高頻用)。

2.4屏蔽

當(dāng)是低頻磁場時�����,主要考慮磁屏蔽,當(dāng)屏蔽層越厚���,材料導(dǎo)電率越高,屏蔽效能越好��;當(dāng)是高頻磁場���、電場或電磁場時,主要考慮用薄金屬屏蔽并良好接地�。另一個值得注意的是在線纜制作時�����,要求電纜屏蔽層和連接器插頭的金屬外殼要有?360度的完整搭接����,不能出現(xiàn)“豬尾巴”現(xiàn)象,否則效果大大打折扣�����。

2.5濾波

主要考慮

(1)抑制工作頻帶以外的干擾�����;

(2)在信號電路中用吸收濾波器消除無用的頻譜成分���;

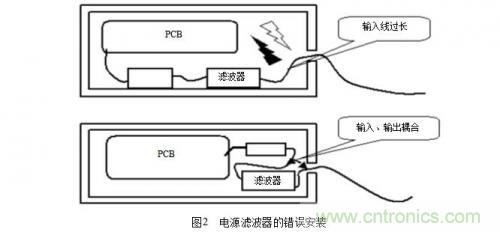

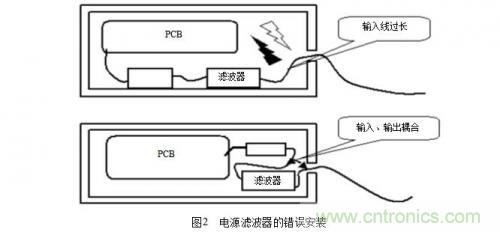

(3)在電源電路(尤其是開關(guān)電源中)���,操縱電路�,控制電路,以及轉(zhuǎn)換電路中消除產(chǎn)生的干擾�。在工程實際中,一個最值得注意的地方是電源濾波器的安裝����,常見的濾波器的錯誤安裝如圖2所示�����。

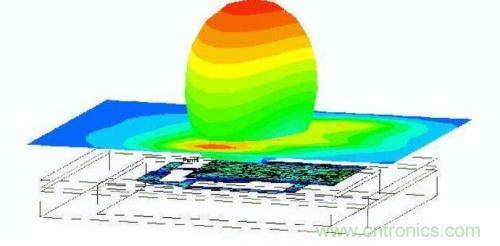

2.6電子設(shè)備的空間位置

由于各種電子設(shè)備的接收特性以及干擾源設(shè)備的輻射特性都具有一定的方向性和一定的作用距離�����,可以利用這些特性適當(dāng)安排電子設(shè)備在設(shè)備空間中的位置以避免干擾和被干擾����,即注意確定電子設(shè)備之間的空間距離和位置的格局�。

3���、PCB設(shè)計技術(shù)

除了元器件的選擇和電路設(shè)計外,良好的印制板(PCB)布線在電磁兼容設(shè)計中也是一個非常重要的因素����。既然PCB是系統(tǒng)的固有成分�,在PCB布線中增強電磁兼容性不會給產(chǎn)品的最終完成帶來附加費用��,從這一點來說也是非常經(jīng)濟(jì)的����。

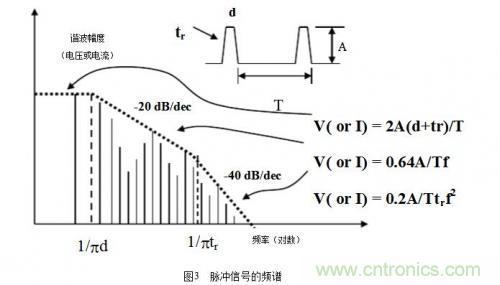

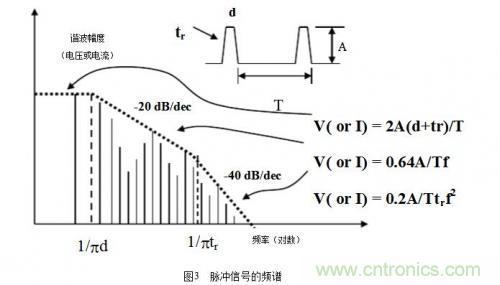

3.1注意電磁兼容設(shè)計的帶寬

在EMC中,除了基本頻率外���,還需考慮諧波因素,通常取十倍頻�����,但在數(shù)字電路中卻有些不同,比如在時鐘電路和邏輯門電路中��,輻射帶寬與數(shù)字信號的上升沿或下降沿有關(guān)系�����,而不是數(shù)字信號的重復(fù)周期���,其關(guān)系為:rtF?/1max?,其中rt是脈沖的上升沿時間�����。例如�����,典型時鐘驅(qū)動的邊沿速率是2ns����,此時���,maxF≈160MHz�����,再考慮十倍頻���,則此時鐘電路可能產(chǎn)生直到1.6GHz的輻射帶寬����。所以在選擇器件時要選擇慢速的邏輯器件系列��,因為器件對電磁輻射貢獻(xiàn)的大小與工作頻率無直接關(guān)系而只取決于邊沿速率(這和從電路功能設(shè)計上選擇快速器件是矛盾的��,在電路設(shè)計時需要折中考慮)�����。還有從器件的抗擾能力上來說,CMOS器件是最好的�,因為它的噪聲容限高�����。從封裝上來說,BGA是最好的����,因為它的引線很短。脈沖信號的頻譜如圖3所示����。

3.2注意用于PCB電磁兼容設(shè)計的電路與電路原理圖不同

主要是由于PCB的電路原理圖沒有考慮電路中元件及PCB線條的分布參數(shù)��,如分布電感��,分布電容�,分布互感,分布互電容以及傳輸延遲等項��。例如導(dǎo)線在高頻時等效于電感和電阻的串聯(lián)��。開關(guān)速度越高��,對負(fù)載阻抗的要求就越高�,要求時鐘驅(qū)動器的輸出阻抗必須等于時鐘線條的波阻抗����,通常時鐘驅(qū)動器都要加串聯(lián)電阻,經(jīng)驗值一般為10~30Ω����。

3.3注意PCB布線原則

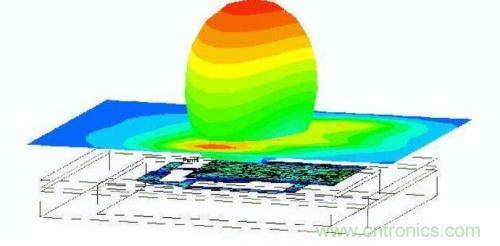

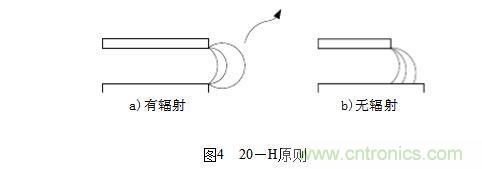

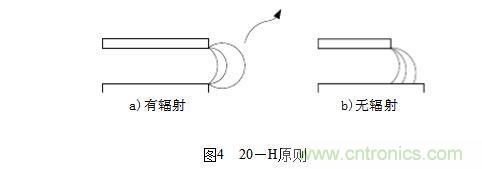

(1)20-H原則,決定印制線條間的距離�,表述如下:所有的具有一定電壓的PCB都會向空間輻射電磁能量(如圖4a)�����,為減小這個效應(yīng)����,PCB的物理尺寸都應(yīng)該比最靠近的接地板的物理尺寸小20H(其中H是兩層PCB的間距),即3mm左右���,這樣可使輻射強度下降70%(如圖4b)���。20-H原則示意圖如圖4所示:

根據(jù)工程實際經(jīng)驗��,采用20-H規(guī)則后會大大提高PCB的自激頻率�����。

(2)3-W原則����,它決定PCB的電源層與邊沿的距離,表述如下:當(dāng)兩條印制線的間距較小時��,兩線之間會發(fā)生電磁串?dāng)_���,從而使電路功能失常。為避免這種影響�����,應(yīng)保持任何線條間距不小于三倍的印制線條寬度���,即3W�,W為印制線條寬度����。印制線條的寬度取決于線條阻抗的要求。

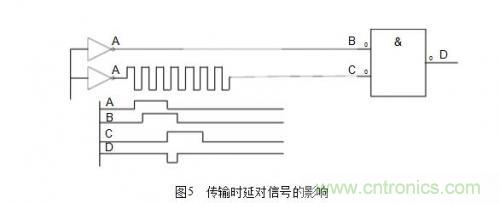

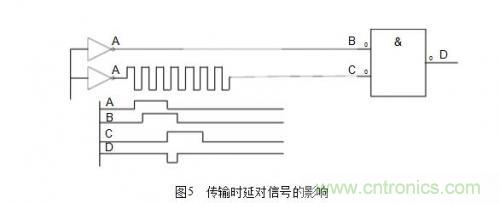

(3)保證信號在PCB上可靠的傳輸�����,確保信號的完整性。這里面主要的問題一般包括時延����、阻抗不匹配�����、地彈跳���、串音等����。這不但影響到電子器件的穩(wěn)定工作�����,還會產(chǎn)生電磁干擾�。一般在高速邏輯設(shè)計中最容易碰到時延問題����,處理不好會產(chǎn)生不希望的脈沖干擾。傳輸時延對信號的影響如圖5所示�。

3.4注意確定PCB布線層數(shù)

首先在設(shè)計中要有一個重要的概念��,就是每個布線層最好與實平面(電源或接地)相鄰�����。原則:

(1)電源平面應(yīng)靠近接地平面并且安排在接地平面之下�����。這樣可以利用兩金屬平板之間的電容作電源的平滑電容����,同時地平面還可以對電源面的輻射電流起到屏蔽的作用�����。

(2)數(shù)字電路和模擬電路分開�����。數(shù)字地和模擬地之間可以不開槽��,但須有一個完整的統(tǒng)一的地平面�,且嚴(yán)格按數(shù)字部分和模擬部分分區(qū)。

(3)中間層的印制線條形成平面波導(dǎo)�,在表面層形成微帶線,兩者傳輸特性不同����。

(4)電路尤其高頻電路是主要的干擾和輻射源,一定要單獨安排��,遠(yuǎn)離敏感電路����。

(5)信號面應(yīng)安排與整塊金屬平面相鄰,這樣是為了產(chǎn)生通量對消作用����。

(6)不同層所含的雜散電流和高頻輻射電流不同�,布線時應(yīng)區(qū)別對待。對于雜散電流可以用去耦電容���,對于高頻輻射電流可以通過減小回路面積��。

以下是常見的PCB層設(shè)計,供參考(S表示信號層�����,G表示地層,P表示電源層)����。四層板:S1����,G���,P�,S2

六層板:S1�,G,S2���,P,G����,S3

八層板:S1,G�,S2�,G���,P�,S3�����,G���,S4

十層板:S1�����,G�����,S2�,S3���,G����,P,S4�����,S5����,G��,S6(但S4對電源噪聲敏感)

3.5注意PCB接地設(shè)計

1)首先���,要建立分布參數(shù)的概念����。高于一定頻率時�,任何金屬導(dǎo)線都可看成是由電阻和電感構(gòu)成的器件,所以��,接地引線具有一定阻抗并且構(gòu)成電氣回路���,不管是單點接地還是多點接地都必須構(gòu)成低阻抗回路進(jìn)入真正地或機架。

2)接地方法

(1)單點接地。如果元件�����,電路的工作頻率小于1MHz時��,單點接地是很好的方式�����,但當(dāng)頻率升高時�,連接線電感作用突出�����,此時接地阻抗將升高�����,當(dāng)接地線的長度為周期信號四分之一波長的奇數(shù)倍時��,不但阻抗高��,還會成為輻射電磁能量的天線����。

(2)多點接地。高頻電路均采用多點接地���,此時可使接地阻抗達(dá)到最小�,可將射頻電流由接地平面分流到金屬地板上去���,因為實體金屬板有較低的電感分量會形成低阻抗回路。

(3)數(shù)字電路應(yīng)當(dāng)作為高頻模擬電路處理���,也應(yīng)該保持低電感接地,并使用高質(zhì)量退耦電容(0.1uF并聯(lián)0.001uF相差兩個數(shù)量級)接地�����。

(4)接地與信號回路����,射頻電流總要找一條道路回饋到起始點去,在電磁兼容設(shè)計中�,通常總是使高速邏輯電路盡可能靠近底版��,接地板安裝,以便更好減少高頻輻射環(huán)路�����。接參考地的地線長度一定要很短�,短到產(chǎn)品最高工作頻率的λ/20以內(nèi)。

(5)接地次序�����,由于一般是電源地騷擾(或噪聲)最大���,故它應(yīng)先接到參考地(這樣做的目的是讓參考地先把騷擾吸收掉)����,然后再送到模擬地和數(shù)字地上去���。

3.6注意PCB中電容的設(shè)計

EMC中的電容可分為退耦電容�,旁路電容��,和容納電容��。退耦電容主要是用來濾除高頻器件在電源板上引起的輻射電流��,為器件提供一個局域化的直流,還能減低印制電路中的電流沖擊的峰值��,通常陶瓷電容被用來作為退耦電容����,其值取決于最快信號的上升時間和下降時間例如����,對于33MHz的時鐘信號,可以使用4.7uF到100uF的電容����,對于100MHz的時鐘信號,可以使用10uF的電容����;另外����,工程上也要考慮ESR對退耦能力的影響�,一般選擇ESR值低于1歐姆的電容。旁路電容能消除高頻輻射噪聲�����,通常鋁電解電容和鉭電容比較適合做旁路電容,其電容值取決于PCB板上的瞬態(tài)電流要求��,一般在10-470uF范圍內(nèi)��,若PCB板上有許多集成電路����,高速開關(guān)電路和具有長引線的電源���,則應(yīng)選擇大容量的電容。容納電容是用來解決開關(guān)器件工作時電源電壓會發(fā)生突降的問題�����。

總之��,選擇電容時��,不但應(yīng)該選擇溫度系數(shù)好的�����,還要選擇等效串聯(lián)電感小的(小于10nH)和等效串聯(lián)電阻小的(小于0.5Ω)電容。從材質(zhì)上說����,低于50MHz時一般選擇Z5U材質(zhì)��,它性能穩(wěn)定��,介電常數(shù)大��,電容容量大��,大于50MHz時一般選擇NPO材質(zhì)����,它介電常數(shù)小�����。通常工程上的實際做法是一大一?�。ㄖ鸽娙葜担﹥蓚€電容并聯(lián)使用����。

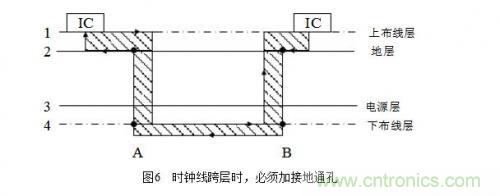

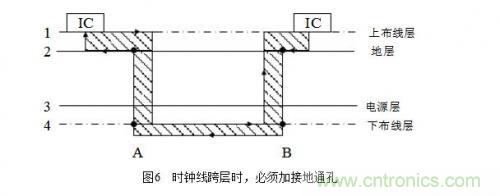

3.7注意PCB過孔的設(shè)計

在布線時盡量少穿過孔���,因為過孔阻抗和線阻抗不一樣�����,存在阻抗突變��,從而產(chǎn)生駐波使信號變壞,容易形成輻射�����,尤其是在時鐘需要穿層時��,要做技術(shù)處理��,時鐘線跨層時的處理如圖6所示�。