【導(dǎo)讀】PCB的有效抗干擾設(shè)計,是電子產(chǎn)品設(shè)計的關(guān)鍵環(huán)節(jié),影響著電路工作的可靠性及穩(wěn)定性。文章剖析了電路板存在電磁干擾的主要原因,從電路板的選取、電路板元器件的布局、電源與地的布線和信號線的布線等方面總結(jié)出在PCB設(shè)計時有效抑制和防止電磁干擾的措施與原則。

印刷電路板(俗稱PCB)是電子產(chǎn)品中電路元件的載體,提供各電路元件之間的電氣連接,是各種電子設(shè)備最基本的組成部分,它的性能直接關(guān)系到電子設(shè)備質(zhì)量的好壞。隨著信息化社會的發(fā)展和電子技術(shù)的發(fā)展,電路的集成度越來越高,電路板的尺寸越來越小,電路板上的元件密度越來越高,電子產(chǎn)品的運行速度越來越快,因此由其自身產(chǎn)生的電磁干擾問題和兼容性問題顯得更加突出,所以,如何減小PCB板的電磁干擾成為當(dāng)今電子技術(shù)的熱門話題。一個電路板的電磁兼容問題是一個電子系統(tǒng)能否正常工作的關(guān)鍵,影響著電路或系統(tǒng)工作的可靠性及穩(wěn)定性,為此在進(jìn)行PCB設(shè)計時要有效解決電磁干擾問題。

在電磁干擾的原因,總結(jié)出在PCB設(shè)計時應(yīng)考慮的減小電磁干擾的措施與原則。

1 電路板存在電磁干擾的原因

在由開關(guān)電源和微處理器構(gòu)成的高速電子系統(tǒng)中,電路板的電磁干擾主要來自于自身存在的射頻干擾源、元器件、基本回路和差模與共模噪聲。

1.1 電路板上存在的射頻干擾源

在智能的高速電子系統(tǒng)中,電路板上的射頻干擾源主要來自微處理器系統(tǒng)、電源供電系統(tǒng)和振蕩器電路。

1.微處理器系統(tǒng)

微處理器的射頻(RF)噪聲產(chǎn)生于芯片內(nèi)部并通過許多不同的可能方式耦合到外部,在所有輸入、輸出、電源和地同時存在,是潛在的噪聲,使到微處理器的每個引腳都可能有問題。而最大的問題是來自微處理器輸入和輸出引腳(I/O)的噪聲。這些噪聲主要產(chǎn)生于芯片內(nèi)部的時鐘切換,通過輸入和輸出引腳連接到內(nèi)部和外部的電纜并輻射出去,主要表現(xiàn)為短時脈沖波形干擾。

2.電源供電系統(tǒng)

電源供電系統(tǒng)包括電源穩(wěn)壓器及其穩(wěn)壓器和微控制器端的旁路電容。這些電路是系統(tǒng)中所有射頻能量的源頭,為芯片內(nèi)的時序電路提供需要的切換電流。

3.振蕩器電路

振蕩器電路為系統(tǒng)提供快速的時鐘信號,在數(shù)字系統(tǒng)中,由于振蕩器的輸出緩沖是數(shù)字的,因此在將正弦波轉(zhuǎn)化為方波時會在輸出側(cè)產(chǎn)生諧波。內(nèi)部運行產(chǎn)生的任何噪聲,比如時鐘緩沖,都會在輸出端顯示出來,并通過元件耦合傳播。

1.2 其他的電磁干擾原因

1.貼片器件和通孔元器件

貼片器件(SMD)因為感抗較小和元器件放置較近、在處理射頻能量時比引線芯片更好。通常,通孔元器件的引線電容在約80MHz時都會產(chǎn)生自振蕩(由容性變?yōu)楦行裕?。因此高?0MHz的噪聲要受到控制,如果設(shè)計中采用通孔元器件就要考慮許多嚴(yán)重的問題。

2.基本回路

從微處理器傳送到另一芯片的每個邊緣跳變都是一個電流脈沖,電流脈沖流向接收芯片,流出接收芯片的接地引腳,然后通過地線返回到微處理器的接地引腳,就構(gòu)成了一個基本回路。這樣的回路在電路中到處存在,任何噪聲電壓和它的附屬電流經(jīng)過最低阻抗路徑回到它產(chǎn)生的地方,從而造成影響。一個回路可以是信號線和它的返回路徑,電源和地之間的旁路,晶振和微處理器內(nèi)的驅(qū)動器,或者是從電源供應(yīng)的電壓穩(wěn)壓器到旁路電容的回路?;芈返膸缀蚊娣e越大,輻射就越強(qiáng),因此,我們可以通過控制返回路徑的形狀和阻抗來減輕噪聲的傳播。

3.差模與共模噪聲

差模噪聲是信號通過線路傳輸?shù)浇邮招酒缓笱胤祷鼐€路返回時產(chǎn)生的噪聲。兩條線路間存在著差分電壓,這是每個信號要完成功能必然要產(chǎn)生的噪聲。這種噪聲產(chǎn)生的電場強(qiáng)度正比于頻率的平方、電流的大小和電流環(huán)路的面積,反比于觀測點到噪聲源的距離。因此,減小差模輻射的方法為:降低電路的工作頻率、減小信號環(huán)路的面積或減小信號電流的強(qiáng)度。在實際工作中最有效的方法是控制信號環(huán)路的面積。

共模噪聲是電壓同時沿信號線和返回線傳輸,兩者之間沒有差分電壓,由信號線和返回線共有的阻抗引起的噪聲。共模阻抗噪聲是大多數(shù)基于微處理器的系統(tǒng)最常見的噪聲源。這種噪聲產(chǎn)生的電場強(qiáng)度正比于頻率的大小、電流的大小和電纜的長度,反比于觀測點到噪聲源的距離。減小共模輻射的方法有:降低地線阻抗,縮短線路的長度,使用共模扼流圈。

2 PCB的設(shè)計原則

由于電路板集成度和信號頻率隨著電子技術(shù)的發(fā)展越來越高,不可避免的要帶來電磁干擾,所以在設(shè)計PCB時應(yīng)遵循以下原則,使電路板的電磁干擾控制在一定的范圍內(nèi),達(dá)到設(shè)計要求和標(biāo)準(zhǔn),提高電路的整體性能。

2.1 電路板的選取

PCB設(shè)計的首要任務(wù)是要適當(dāng)?shù)剡x取電路板的大小,尺寸過大會因元器件之間的連線過長,導(dǎo)致線路的阻抗值增大,抗干擾能力下降;而尺寸過小會導(dǎo)致元器件布置密集,不利于散熱,而且連線過細(xì)過密,容易引起串?dāng)_。所以應(yīng)根據(jù)系統(tǒng)所需元件情況,選擇合適尺寸的電路板。

電路板分為有單面板、雙面板和多層板。電路板層數(shù)的選取取決于電路要實現(xiàn)的功能、噪聲指標(biāo)、信號和網(wǎng)線數(shù)量等。合理的層數(shù)設(shè)置可以減小電路自身的電磁兼容問題。通常的選取原則是:①對于信號頻率為中低頻,元器件較少,布線密度屬于較低或中等時,選用單面板或雙面板;②對于布線密度高、集成度高且元器件較多時采用多層板;③對于信號頻率高、高速集成電路、元器件密集的選4層或?qū)訑?shù)更多的電路板。多層板在設(shè)計時可單獨某一層作為電源層、信號層和接地層。信號回路面積減小,降低差模輻射,為此多層板可以減小電路板的輻射和提高抗干擾能力。

2.2 電路板元器件的布局

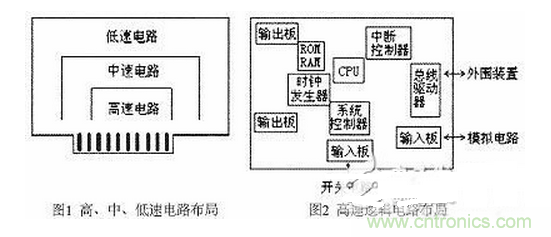

在確定PCB尺寸后,應(yīng)先確定特殊元件的位置,最后根據(jù)電路的功能單元,分塊的對電路的全部元件進(jìn)行布局。數(shù)字電路單元、模擬電路單元和電源電路單元應(yīng)分開,高頻電路單元和低頻電路單元也應(yīng)分開。通常,在布置高速、中速和低速電路時,應(yīng)參考圖1的方式排列元器件;在布置帶有時鐘、CPU、存儲器、控制器和輸入輸出電路時,應(yīng)參考圖2的方式排列元器件。常用電路板的布局原則如下。

1.確定特殊元件位置的原則:

?、侔l(fā)熱元件應(yīng)放置在利于散熱的位置,例如PCB的邊緣,并遠(yuǎn)離微處理器芯片;

?、谔厥獾母哳l元件應(yīng)緊挨著放置,以縮短他們之間的連線;

?、勖舾性?yīng)遠(yuǎn)離時鐘發(fā)生器、振蕩器等噪聲源;

?、茈娢黄鳌⒖烧{(diào)電感器、可變電容器、按鍵開關(guān)等可調(diào)元件的布局應(yīng)符合整機(jī)的結(jié)構(gòu)需求,方便調(diào)節(jié);

⑤質(zhì)量較重的元件應(yīng)采用支架固定;

?、轊MI濾波器應(yīng)靠近EMI源放置。

2.根據(jù)電路功能單元對電路的傘部元器件進(jìn)行布局的原則:

?、俑鞴δ茈娐窇?yīng)按照之間的信號流向確定相應(yīng)的位置,方便布線;

②每個功能電路應(yīng)先確定核心元件的位置,并圍繞核心元件放置其他元件,盡量縮短元件之間的連線;

?、蹖Ω哳l電路,應(yīng)考慮元件之間的分布參數(shù);

④放置于電路板邊上的元件,應(yīng)離電路板邊緣不小于2mm。

?、軩C/DC變換器、開關(guān)管和整流器應(yīng)盡量靠近變壓器放置,以減小對外的輻射;

?、拚{(diào)壓元件和濾波電容器應(yīng)靠近整流二極管放置。

2.3 電源與地的布線原則

PCB的電源與地的布線是否合理是整個電路板減小電磁干擾的關(guān)鍵所在。電源線和地線的設(shè)計是PCB中不可忽視的問題,往往也是難度最大的一項設(shè)計,設(shè)計時應(yīng)遵循以下原則。

1.電源與地的布線技巧

PCB上的布線是有阻抗、容抗和感抗等分布參數(shù)的特性。為了減小PCB布線的分布參數(shù)對高速電子系統(tǒng)的影響,對電源與地的布線原則為:①增大走線的間距以減少電容耦合的串?dāng)_;②電源線和地線應(yīng)平行走線,以使分布電容達(dá)到最佳;③根據(jù)承載電流的大小,盡量加粗電源線和地線的寬度,減小環(huán)路電阻,同時使電源線和地線在各功能電路中的走向和信號的傳輸方向一致,這樣有助于提高抗干擾能力;④電源和地應(yīng)直接走線在各自的上方,從而減小感抗和使回路面積最小,盡量使地線走在電源線下面;⑤地線越粗越好,一般地線的寬度不小于3mm;⑥將地線構(gòu)成閉環(huán)路以縮小地線上的電位差值,提高抗干擾能力;⑦在多層板布線設(shè)計時,可將其中一層作為“全地平面”,這樣可以減少接地阻抗,同時又起到屏蔽作用。

2.各功能電路的接地技巧

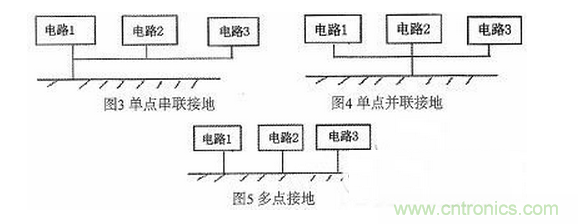

PCB各功能電路的接地方式分為單點接地和多點接地。單點接地根據(jù)連接形式分為單點串聯(lián)接地和單點并聯(lián)接地兩種方式,如圖3和圖4所示。單點串聯(lián)接地由于各接地導(dǎo)線長度不同,各電路接地阻抗不同,電磁兼容性能降低,常用于保護(hù)接地。單點并聯(lián)接地各電路有獨自的接地線,因此相互之間的干擾小,但可能延長接地線,增大接地阻抗,常用于信號接地、模擬接地、電源接地。多點接地是指各電路都有一個接地點,如圖5所示。多點接地常用于高頻電路,具有接地線短,接地阻抗值較小,減少高頻信號的干擾。

為了減少接地帶來的干擾,接地也要滿足一定的要求:①接地線盡可能要短,接地面要大;②避免產(chǎn)生不必要的接地回路,減小公共接地的干擾電壓;③接地原則是對于不同信號采取不同接地方式,不能把所有接地采取同一接地點;④在設(shè)計多層PCB時,要把電源層和接地層盡可能放置在相鄰的層中,以便電路中形成層問的電容,減小電磁干擾;⑤盡量避免強(qiáng)電和弱電信號,數(shù)字和模擬信號共地。

3.放置格柵化平面

對兩層板來說,格柵化是最重要的設(shè)計技術(shù)。格柵化是在PCB上延伸地線并使用地填充模式來構(gòu)建連接到地的格柵網(wǎng)絡(luò),構(gòu)成一個有效的地平面,和四層板一樣能夠減小噪聲。它有兩個目的:①模仿四層板的地層,為每一條信號線提供處于下方的返回路徑;②降低微處理器和電壓穩(wěn)壓之間的阻抗。設(shè)計時應(yīng)注意的原則是:①每條地線延伸盡可能填充印刷電路板的空間;②在兩層板上盡可能多的放置格柵;③尺寸上合適時使用盡可能多的通孔將頂層和底層的格柵連接起來;④線路不一定要直角或同樣的寬度。

4.高頻去耦電容和鐵氧體磁珠的使用

數(shù)字電路中,當(dāng)邏輯門的狀態(tài)發(fā)生變化時,會在電源上產(chǎn)生一個很大的尖峰脈沖,形成瞬間的噪聲電壓,這種情況普遍采用去耦電容或鐵氧體磁珠來限制電流的突然變化,減小輻射。通常在每個芯片的電源和地之間加上容量約為0.01μF~0.1μF的高頻去耦電容,在靠近芯片的電源線上放置鐵氧體磁珠,以阻斷來自電源線的射頻電流源。設(shè)計時應(yīng)盡量做到:①采用鉭電容,而不要使用鋁電解電容,后者具有較大的內(nèi)部電感;②電容距離芯片越近越好,去耦電容的引線不宜太長;③鐵氧體磁珠只用在+V的電源線上,不用在地線上;④鐵氧體磁珠盡量靠近噪聲源放置。

2.4 信號線的布線原則

1.減小線路的容性和感性串?dāng)_

布線時,即使在很短的距離內(nèi)并行走線的線路之間也存在容性和感性串?dāng)_。容性耦合時,源端的上升沿會在受害者上引起一個上升沿。感性耦合時,受害者上的電壓改變與源端的改變正好相反。大部分串?dāng)_都是容性的,噪聲的大小正比于并行的距離、頻率、源端電壓的振幅和受害者的阻抗,反比于兩條線路離開的距離。因此減小串?dāng)_的措施有:①使連接到微處理器的攜帶射頻噪聲的線路遠(yuǎn)離其他信號;②應(yīng)將可能成為噪聲受害者的信號的返回地線走線在其下方;③不要在電路板的外部邊緣走噪聲線路;④如果可能,將一些噪聲線路走線在一起然后用地線包圍;⑤使非噪聲線路遠(yuǎn)離電路板上容易接收噪聲的區(qū)域,比如接插件、振蕩器電路、繼電器和繼電器驅(qū)動器。

2.合理安排返回地線數(shù)目

在計算機(jī)工業(yè)中,電纜或?qū)Ь€中每9條信號線至少要有1根地線,這是很普遍的經(jīng)驗。高速時,這個比例變到5:1??梢栽谠O(shè)計信號線和返回線路時考慮的原則:①最好是電纜中的每條信號線都有一條返回地線,組成雙絞線對;②不要超過每9條信號線有一條返回地線;③如果電纜超過一英尺長,應(yīng)該每4條信號線有一條返回地線;④如果可能,應(yīng)該使用一個實心金屬支架作為機(jī)械支架,焊接在兩塊電路板之間,既作為安裝支架,也作為可靠的射頻返回地線。

3.其他的布線原則

?、儆米鲗?dǎo)線的銅箔在90度轉(zhuǎn)彎處會使導(dǎo)線的阻抗不連續(xù),有可能產(chǎn)生反射干擾,所以應(yīng)將90度的導(dǎo)線改成135度的走線,這樣有助于減少發(fā)生反射干擾;②雙面布線的PCB,上下兩層的布線應(yīng)垂直交叉,以減少耦合,有利于抑制干擾;③采用隔離走線,在許多不得不平行走線的電路布線時可考慮在兩條信號線中加一條接地的隔離走線;④所有線路盡量沿直流地鋪設(shè),盡量避免沿交流地鋪設(shè);⑤采用短接線,在線路無法排列或只有繞大圈才能走通的情況下,干脆用絕緣“飛線”連接,不用印刷線,或者用阻容元件引線直接跨接;⑥直流電路應(yīng)遠(yuǎn)離交流電路布線,輸入信號線與輸出信號線應(yīng)分開;⑦信號走線不要有分支,應(yīng)連貫地從一個元件到下一個元件,以避免反射干擾或諧波干擾;⑧時鐘等高頻信號線應(yīng)靠近地線進(jìn)行布線,使環(huán)路面積最小,以減小差模輻射。

3 結(jié)束語

想完全消除電子產(chǎn)品中的電磁干擾是不可能的,我們只能采取必要措施減小電磁干擾,使電磁干擾控制在一定范圍內(nèi),而一個良好的印刷電路板的設(shè)計,是減小電磁干擾的重要環(huán)節(jié)。在印刷電路板設(shè)計時,可參考以上所提到的設(shè)計原則,但這些原則并不是一成不變,應(yīng)該根據(jù)具體電路情況,靈活應(yīng)用各種抗干擾的方法,才能最大程度地滿足電磁兼容的要求,這需要設(shè)計者平時的經(jīng)驗積累和總結(jié)。