【導(dǎo)讀】汽車電系上的負載多種多樣,對外是潛在的干擾發(fā)射源,也是對車載電子產(chǎn)品的干擾源。而電磁干擾耦合也會影響汽車電子電氣系統(tǒng)的正常運行。

汽車電器的電磁兼容設(shè)計

造成電器功能降級或失效的電磁干擾的發(fā)生必須同時具備3個要素:干擾源、干擾耦合通路以及敏感設(shè)備。抑制干擾源、阻斷耦合以及提高敏感設(shè)備的抗擾閾值是解決電磁兼容問題的根本措施。

1 電磁干擾的傳輸和傳輸途徑

電磁干擾的發(fā)生必然存在干擾能量的傳播和傳播通道。干擾的傳輸有兩種基本方式:傳導(dǎo)和輻射。輻射耦合細分為:天線對天線耦合、場對線耦合和線對線耦合。針對干擾的傳播和耦合途徑,在汽車電器工程實踐中要采取如下的系統(tǒng)方法來改善EMC特性:濾波、屏蔽、搭鐵和布線。

2 干擾源和敏感設(shè)備的電磁兼容設(shè)計

在方案已定的功能電路中,檢驗電磁兼容指標是否滿足要求;此時如不滿足要求,則可通過參數(shù)修改來達到指標,如調(diào)整數(shù)字化控制器的工作頻率、圓整脈沖的上升率或重新選擇元件等。其次進行防護設(shè)計,包括濾波、屏蔽、搭鐵與搭接設(shè)計,甚至采用時空隔離和頻率回避等改進措施。最后是做布局調(diào)整性設(shè)計,包括對總體布局的檢驗、屏蔽體縫隙的檢驗、組件和印制板布局檢驗等。電路和分系統(tǒng)的電磁兼容設(shè)計包括如下的步驟:元件選擇、電路選擇、濾波技術(shù)應(yīng)用、搭鐵設(shè)計、屏蔽設(shè)計、電路布局和系統(tǒng)布局規(guī)劃。

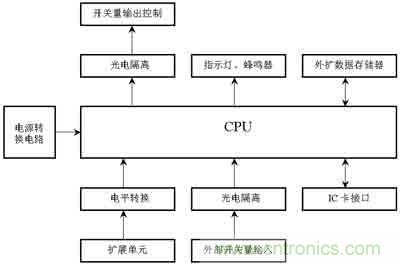

圖1 汽車行駛記錄儀硬件結(jié)構(gòu)原理圖

3 ESD防護設(shè)計

為了消除靜電放電的危害,可采取的措施有:建立完善的屏蔽結(jié)構(gòu),通過搭鐵的金屬殼將靜電荷釋放到地;內(nèi)部電路與金屬殼的連接應(yīng)采用一點搭鐵;增加諸如硅瞬變電壓吸收二極管(STVS)之類的快速保護元件,將高壓電荷泄放到地;印制電路板設(shè)計中增加保護環(huán)帶,將人手拔插線路板的電荷通過最短的路徑泄放到地。

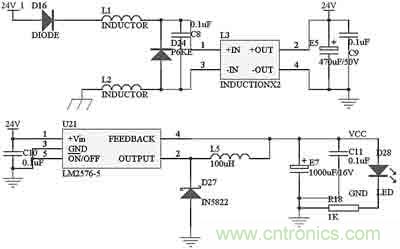

圖2 開關(guān)電源電路

汽車行駛記錄儀的抗干擾設(shè)計

1 汽車行駛記錄儀的硬件結(jié)構(gòu)

圖1為汽車行駛記錄儀硬件結(jié)構(gòu)原理。信號的抗干擾處理是通過光電隔離來實現(xiàn)。車載設(shè)備的電源系統(tǒng)對設(shè)備的可靠運行影響很大,好的電源電路能夠過濾掉許多通過電源線傳入的干擾信號。

2 電源部分的抗干擾設(shè)計

本控制模塊的電源電路如圖2所示。車載蓄電池—發(fā)電機的電源從24V_1處進入,二極管D16主要是防止電源的正負極被誤接反。電感L1、L2對電源進行濾波,和共模電感L3、電容C8配合,可以過濾掉電源中的尖峰脈沖。二極管D24 P6KE51A是脈沖干擾抑制器(TVS),它可以快速吸收超過額定電壓的尖峰脈沖,瞬時通過電流很大,最大功率可達500~1000W。電容E5和C9進一步對電源進行濾波。過濾干凈的電流通過開關(guān)電源芯片LM2576變換為系統(tǒng)使用的5V電源。電容E7和C11對輸出5V電源進行濾波,電阻R18和發(fā)光二極管D28指示當(dāng)前是否有電。

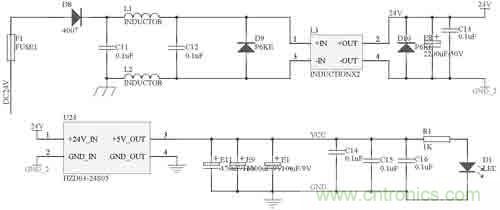

圖3 DC/DC電源電路

在某些對可靠性要求更高的電源系統(tǒng)中,可以考慮采用寬輸入電壓范圍的DC-DC模塊進行電源變換,如圖3所示。這種DC-DC模塊的輸入和輸出完全隔離,輸入范圍很寬。標稱輸入電壓為12V的DC-DC電源的允許輸入范圍是9~18V;標稱輸入電壓為24V的DC-DC電源模塊的允許輸入范圍是18~36V。

這兩種電路都經(jīng)歷了實際應(yīng)用的考驗,實踐證明,不管在汽油車上還是在柴油車上都穩(wěn)定可靠。

線路板設(shè)計需注意的抗干擾問題

線路板的布線對系統(tǒng)的抗干擾性能影響很大,本系統(tǒng)布線主要從以下幾點進行考慮:

1.盡量加粗電源線和地線,在電源入口處盡量使用大儲能電容,在線路板空余處鋪設(shè)覆銅,這樣會大大增強線路板的抗干擾性能。

2.在芯片的電源和地兩端增加去耦電容,電容值為0.01~0.1μF,最好用陶瓷電容,每個芯片處都要加,這非常重要。

3.IO引腳處加上一個去耦電容,可以濾除大量的外部干擾。

4.盡量減少高頻信號線的布線長度,特別是時鐘信號線,由于頻率很高,布線越長發(fā)出的電磁干擾就越強烈。同時,也要盡量減小其他信號線的長度。

5.盡量使用表面貼裝芯片,這樣不僅可以縮短電路長度,還不會發(fā)生因振動、沖擊而松動的情況。