【導(dǎo)讀】本文首先介紹了高速串行鏈路設(shè)計中AC耦合電容阻抗優(yōu)化的重要性,然后闡述如何利用軟件ViaExpert對AC耦合電容設(shè)計進行前仿真,然后指導(dǎo)后續(xù)PCB設(shè)計,最后在PCB完成后進行仿真,完成仿真的閉環(huán)設(shè)計。

1.引言

隨著高速串行總線的速率越來越高,鏈路的阻抗也隨之成為SI工程師關(guān)注的焦點。由于高速串行總線鏈路中唯一的無源器件就是AC耦合電容,所以在我們對傳輸線阻抗以及過孔或者連接器的PIN的阻抗優(yōu)化之后,剩下的也就是AC耦合電容的阻抗的優(yōu)化,當然25Gbps鏈路為了進一步減小AC耦合通道阻抗不連續(xù)性的影響,IC廠家直接把AC耦合電容設(shè)計在接收端芯片這里,所以對于正在設(shè)計10Gbps鏈路的應(yīng)用,AC耦合電容成為SI工程師的必修課了。

AC耦合電容的阻抗仿真,因為需要考慮到焊盤和GND或者POWER平面的容性耦合,所以常規(guī)在HFSS中建模會比較耗費時間,目前芯禾科技推出的ViaExpert建模工具可以針對各種疊層和電容封裝進行AC耦合電容阻抗優(yōu)化前仿真,后續(xù)布線階段也可以導(dǎo)入Brd文件提取出AC耦合電容的焊盤尺寸和掏空的層數(shù)和大小,最終仿真出你所能接受的阻抗設(shè)計。

2.AC耦合電容的掏空設(shè)計

AC耦合電容焊盤相比鏈路的走線會比較寬,這樣對于高速信號傳輸來說就是一處阻抗不連續(xù)點(如圖1),為保證阻抗的一致性,AC耦合電容的下方需要做多層的掏空,但是由于PCB設(shè)計的第3層或者倒數(shù)第3層通常是POWER層,挖空后可能會導(dǎo)致BGA IO口模擬電源的壓降問題;目前很多電源模塊都具有Remote Sense功能,可以補償PCB壓降問題,所以AC耦合電容焊盤下方做多層掏空也是可以的。

在此背景下,我們就需要一種仿真工具可以對掏空大小和掏空層數(shù)做阻抗優(yōu)化仿真,通過調(diào)整AC耦合電容焊盤下方的挖空大小以及挖空的層數(shù)來確定單板基于某種疊層下的焊盤阻抗是否比較接近差分傳輸線的阻抗,最終給出PCB設(shè)計的優(yōu)化規(guī)則。后續(xù)我將介紹如何利用ViaExpert軟件進行AC耦合電容阻抗優(yōu)化仿真的設(shè)計。

圖1 高速串行鏈路中AC耦合電容的設(shè)計

3.AC耦合電容阻抗前仿真優(yōu)化

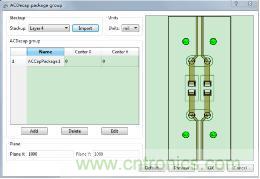

在最新ViaExpert版本中,有專門針對AC耦合電容阻抗仿真的優(yōu)化流程,軟件界面如下圖2所示。疊層可以利用軟件默認設(shè)置也可以由用戶PCB疊層,通過Import按鈕導(dǎo)入。AC耦合電容這里可以支持一對差分也可以支持多對差分進行AC耦合電容的串擾仿真,這里我們只以單對差分為例進行仿真。

圖2 AC耦合電容建模初始界面

上圖確定好疊層和AC耦合電容的對數(shù)之后我們就可以對單對AC耦合電容的出線及信號孔和地孔做更詳細的設(shè)置,具體設(shè)置信息如下圖3所示。

圖3 AC耦合電容建模設(shè)置

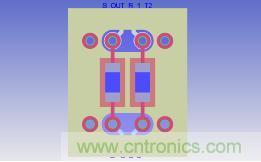

這里我們以0402的AC耦合電容為例進行仿真,一端Botm層通過換層過孔連接Top面的AC耦合電容,另外一端通過過孔再連接到Art12層,這里我們分別仿真3種情況;電容掏空到GND02層,X方向掏34mil,Y方向掏66mil(Case1)。模型建好后的3D效果圖如圖4所示。

圖4 AC耦合電容3D效果圖(Case1)

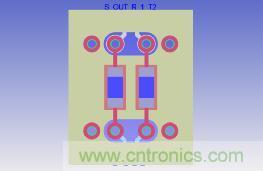

電容掏空到GND02層,X方向掏28mil,Y方向掏58mil(Case2),如圖5所示。

圖5 AC耦合電容3D效果圖(Case2)

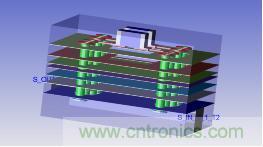

電容掏空到POWER04層,X方向掏34mil,Y方向掏66mil(Case3),如圖6所示。

圖6 AC耦合電容3D效果圖(Case3)

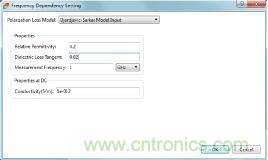

模型生成好后,電容出線的兩端會自動生成Wave Port,所以不需要你手動去設(shè)置Port,這里還有一點就是材料的參數(shù)以及孔徑需要你去設(shè)置,材料參數(shù)設(shè)置因為是前仿真,所以用Djordjevic-Sarkar Model Input簡單的頻變模型(圖7),只需要設(shè)置一個頻點的Dk和Df值就可以求解寬帶的頻變曲線。具體設(shè)置界面如下所示,這里我們板材選用FR-4,Dk和Df的值選擇1GHz頻點。

圖7 Djordjevic-Sarkar Model Input

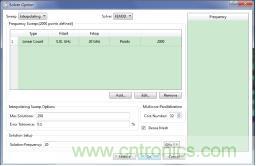

Case1和Case2參數(shù)分別設(shè)置好之后,我們就可以開始仿真,仿真頻率范圍設(shè)為10MHz-20GHz頻段。具體設(shè)置如下圖8所示,芯禾科技在最新的版本當中加入了Dense Mesh功能,可以在對結(jié)構(gòu)復(fù)雜區(qū)域增加Mesh的數(shù)量,客戶可以通過勾選項自行選擇。

圖8 仿真引擎設(shè)置

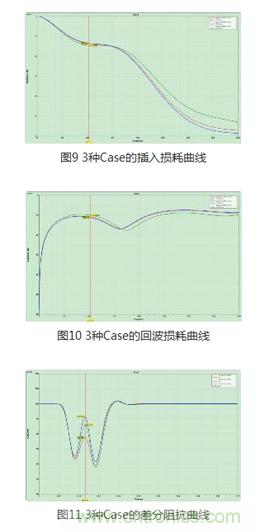

下面是Case1,Case2,Case3三種情況下AC耦合電容插入損耗,回波損耗以及差分阻抗曲線,分別如圖9,圖10及圖11所示。這里使用SnpExpert對S參數(shù)進行比較。

從以上3種情況的仿真結(jié)果可以看出,掏空2層的阻抗是最接近100ohm的,所以在5.16GHz基頻處的插入損耗和回波損耗也是最優(yōu)秀的,但是和掏空1層的結(jié)果差別不是太大,Case2情況是最差的,因為掏空區(qū)域變小了,差分阻抗變低了。所以后續(xù)我們在PCB設(shè)計階段就可以根據(jù)以上前仿真結(jié)果進行指導(dǎo),對于通流比較緊張的情況,我們只掏空GND02層的地,對于POWER03或者ART03空間寬裕的情況下,可以掏2層處理。

4.AC耦合電容阻抗后仿真驗證

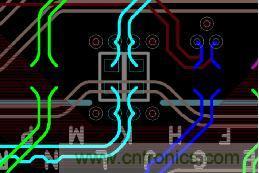

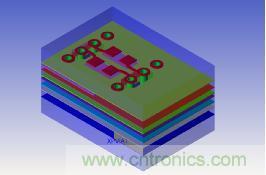

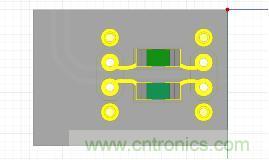

根據(jù)上節(jié)3種Case情況下的仿真結(jié)果和PCB設(shè)計的實際情況,AC耦合電容只掏空GND02層,掏空尺寸為X方向掏34mil,Y方向掏66mil。因為ViaExpert可以直接導(dǎo)入Brd文件,所以在PCB設(shè)計完成后在ViaExpert里面直接對Brd進行解析,提取出板上的AC耦合電容和出線。PCB實際AC耦合電容的設(shè)計以及導(dǎo)入到ViaExpert中提取完成的3D效果圖分別如圖12和圖13所示。

圖12 實際AC耦合電容出線

圖13 實際AC耦合電容3D效果圖

因為ViaExpert里面提取Brd無法獲得電容相應(yīng)的模型,所以后仿真需要把模型導(dǎo)入到HFSS中,然后加上AC耦合電容的Model,最終如圖14所示。

圖14 實際AC耦合電容3D效果圖

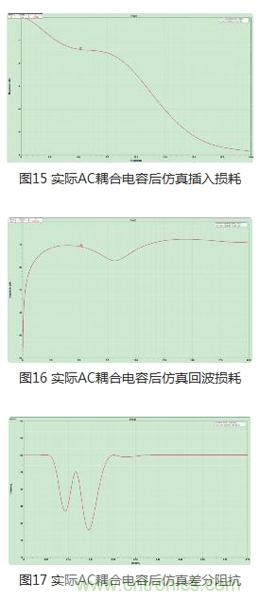

仿真結(jié)果如下圖15,圖16,圖17所示?;竞颓胺抡娼Y(jié)果一致

5.結(jié)論

本文介紹了如何利用ViaExpert軟件對高速串行鏈路AC耦合電容的前仿真差分阻抗優(yōu)化以及PCB后仿真建模,前仿真得出設(shè)計方向后指導(dǎo)PCB設(shè)計,最后后仿真確定設(shè)計是否滿足要求,最終保證高速串行鏈路設(shè)計的一板成功。