【導(dǎo)讀】針對高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化,著重分析封裝與PCB互連區(qū)域差分布線方式,信號布局方式,信號孔/地孔比,布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串?dāng)_的具體影響。

摘要

隨著電子系統(tǒng)通信速率的不斷提升,BGA封裝與PCB互連區(qū)域的信號完整性問題越來越突出。

針對高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化,著重分析封裝與PCB互連區(qū)域差分布線方式,信號布局方式,信號孔/地孔比,布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串?dāng)_的具體影響。

利用全波電磁場仿真軟件CST建立3D仿真模型,時頻域仿真驗證了所述的優(yōu)化方法能夠有效改善高速差分信號傳輸性能,減小信號間串?dāng)_,實現(xiàn)更好的信號隔離。

近年來,球柵陣列(BGA)封裝因體積小,引腳多,信號完整性和散熱性能佳等優(yōu)點而成為高速IC廣泛采用的封裝類型。

為了適應(yīng)高速信號傳輸,芯片多采用差分信號傳輸方式。隨著芯片I/O 引腳數(shù)量越來越多,BGA焊點間距越來越小,由焊點、過孔以及印制線構(gòu)成的差分互連結(jié)構(gòu)所產(chǎn)生的寄生效應(yīng)將導(dǎo)致衰減、串?dāng)_等一系列信號完整性問題,這對高速互連設(shè)計提出了嚴(yán)峻挑戰(zhàn)。

目前國內(nèi)外學(xué)者對于板級信號完整性問題的研究仍多集中于水平傳輸線或者單個過孔的建模與仿真,頻率大多在20 GHz以內(nèi)。對于包括過孔、傳輸線的差分互連結(jié)構(gòu)的傳輸性能以及耦合問題研究較少。并沒有多少技術(shù)去減少封裝與PCB互連區(qū)域垂直過孔間的串?dāng)_。

文章針對高速BGA封裝與PCB差分互連結(jié)構(gòu)進(jìn)行設(shè)計與優(yōu)化。著重分析改進(jìn)差分布線方式,信號布局方式,信號孔/地孔比,布線層與背鉆這四個方面對改善高速差分信號傳輸性能和串?dāng)_的具體影響。利用全波電磁場仿真軟件CST微波工作室建立3D仿真模型。仿真頻率達(dá)到40 GHz,在時域和頻域同時驗證了所述優(yōu)化方法的有效性。

1、物理模型

1.1 差分互連結(jié)構(gòu)

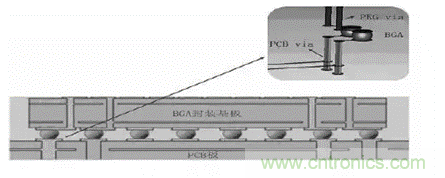

在高速信號傳輸中,差分信號因具有減小軌道塌陷和電磁干擾、提高增益、消除共模噪聲和開關(guān)噪聲干擾等優(yōu)點而被廣泛使用。高速差分信號通過IC封裝到達(dá)PCB板各層進(jìn)行傳播,為了實現(xiàn)BGA封裝基板與PCB各層的電氣連接,由水平差分線和垂直差分過孔共同構(gòu)成了差分互連結(jié)構(gòu),如圖1所示。

圖1 BGA封裝與PCB板垂直互連結(jié)構(gòu)

1.2 仿真環(huán)境及參數(shù)設(shè)置

本文采用的仿真環(huán)境為全波電磁場仿真軟件CST微波工作室,集時頻域算法為一體,含多個全波及高頻算法,可仿真任意結(jié)構(gòu)、任意材料下的S 參數(shù),并可以與電路設(shè)計軟件聯(lián)合仿真。

幾種優(yōu)化方案均由CST微波工作室建立三維物理模型,PCB 的層疊結(jié)構(gòu)如圖2 所示,PCB板共12層,第1,3,5,8,10,12層為信號層(走線層),第2,4,6,7,9,11 層為電源或地層。板厚為97.6 mil,板材介電常數(shù)3.8,損耗正切0.012。

0.8 mm間距BGA扇出過孔間距為31.4 mil,過孔孔徑8 mil,線寬/線距5 mil,差分走線在第10層。

圖2 PCB板層疊結(jié)構(gòu)剖面圖

2、優(yōu)化與設(shè)計

從四個方面進(jìn)行設(shè)計優(yōu)化,以改善高速差分信號的傳輸性能及信號間串?dāng)_。分別為差分布線方式,信號分布方式,信號孔/地孔比,布線層選擇與過孔殘樁。CST仿真的結(jié)果以S 參數(shù)的形式體現(xiàn),仿真頻率達(dá)40 GHz,在時域和頻域同時驗證所述優(yōu)化方法的有效性。

2.1 布線方式

差分信號從過孔引出時,不同的布線方式會對差分信號的傳輸特性有很大的影響,如果傳輸線不能等長等距,就會引起信號失真,產(chǎn)生共模噪聲。

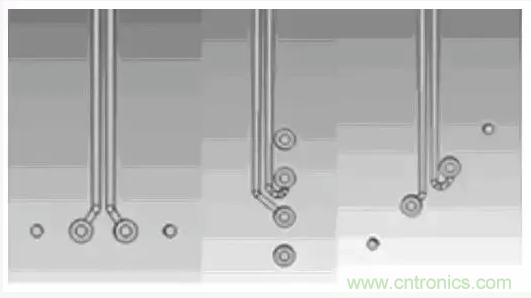

如圖3所示,信號從過孔引出時分別采取三種布線方式,0°,90°轉(zhuǎn)角,45°轉(zhuǎn)角,每對差分過孔周圍有兩個隔離地孔。布線在PCB板第10層。

圖3 三種差分線引出方式

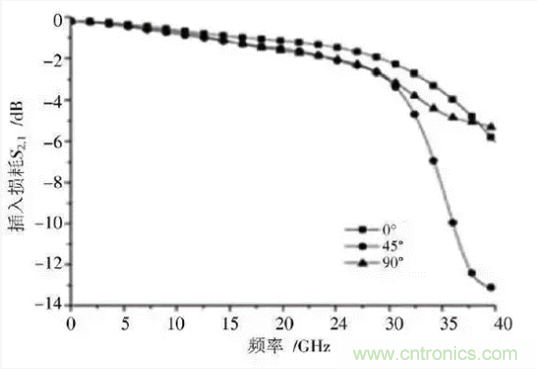

圖4是以上三種不同布線方式的插入損耗。顯然,種水平對稱的方式傳輸性能。差分信號重要的就是等長等距,等長的目的是要確保時序的準(zhǔn)確與對稱性,兩條傳輸線上的任何時延差或錯位,都會導(dǎo)致差分信號失真,并使部分差分信號變成共模信號,產(chǎn)生電磁干擾。

等距的目的是保持差分阻抗的一致性。45°和90°轉(zhuǎn)角在布線時都無法做到的等長等距,產(chǎn)生相位差和共模噪聲。

圖4 不同布線方式下差分對的插入損耗

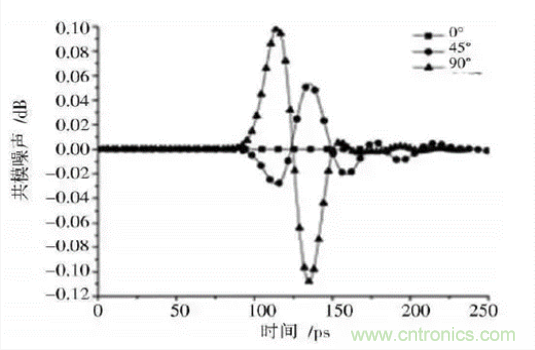

圖5和圖6分別從頻域和時域展示了三種布線方式所產(chǎn)生的共模噪聲。不論是45°轉(zhuǎn)角還是90°轉(zhuǎn)角,產(chǎn)生的共模噪聲都比0°高得多,而45°轉(zhuǎn)角布線要略優(yōu)于90°轉(zhuǎn)角。

圖5 不同布線方式下共模噪聲頻域比較

圖6 不同布線方式下共模噪聲時域比較

根據(jù)經(jīng)驗法則,為了把錯位維持在信號上升邊10%以內(nèi),要求兩線長度匹配至上升邊空間延伸的10%以內(nèi)。這種情況下,對走線總長度的匹配要求如下:

ΔL =0.1×RT×v

式中:ΔL 表示為錯位維持在上升邊的10%以內(nèi),兩條走線之間的長度偏差;RT表示信號的上升邊;v 表示差分信號的傳播速度。如果信號的傳播速度大致為6 in/ns,上升邊為100 ps,那么兩條走線的長度應(yīng)匹配至其偏差小于60 mil。

由于高速信號上升時間越來越短,留給緣于走線長度偏差的錯位預(yù)算在不斷變小,使得走線長度之間的匹配顯得愈加重要。

因此在實際應(yīng)用中,應(yīng)盡量采用0°這樣水平對稱的方式布線,來達(dá)到等長等距的目的。

2.2 信號分布方式

BGA封裝管腳在扇出時通過過孔連接至PCB板其他各層,幾十對差分對同時高密度、長線并行,相鄰的傳輸線由于電場和磁場的作用(耦合電容/耦合電感),一對差分線傳輸?shù)男盘枙ο噜彽膫鬏斁€產(chǎn)生串?dāng)_[9]。

由于BGA焊點的排列是固定的,因此焊盤和過孔的位置取決于焊點的分布,合理的BGA管腳信號布局可以改善差分對之間的串?dāng)_。不同信號分布方式見圖7。

圖7 不同信號分布方式

如圖7所示的兩種布局方式:3對信號橫向水平布置;3對信號正交布置。

每對信號周圍各有兩個隔離地孔。中間為受擾線,兩邊為干擾線,根據(jù)走線將3對差分對定義成6個差分端口,D1~D3為BGA扇出端,通過觀察D4,D6端口對D2端口的遠(yuǎn)端串?dāng)_來分析相鄰?fù)ǖ赖拇當(dāng)_情況,由于兩邊對稱,只需觀察D4端口對D2端口的串?dāng)_。差分對遠(yuǎn)端串?dāng)_比較如圖8所示。

圖8 不同信號分布方式下差分對遠(yuǎn)端串?dāng)_比較

由圖8所示的結(jié)果可以看到,信號正交布局時,由于孔?孔之間距離增大,孔?孔耦合減小,從端口D4到端口D2的遠(yuǎn)端串?dāng)_低于水平布局時的遠(yuǎn)端串?dāng)_。

由表1可知,優(yōu)化后的遠(yuǎn)端串?dāng)_比原設(shè)計在大于5 GHz頻帶內(nèi)有5~15 dB的改善。圖9從時域也驗證了正交布局的優(yōu)越性。優(yōu)化后的設(shè)計瞬態(tài)峰值噪聲比原設(shè)計降低了10 mV,如表1所示。

圖9 不同信號分布方式下差分對遠(yuǎn)端串?dāng)_時域響應(yīng)比較

表1 遠(yuǎn)端串?dāng)_比較

2.3 信號孔/地孔數(shù)量比

由于在設(shè)計中BGA焊點的間距是固定的,一味增加信號之間的距離來降低串?dāng)_不太可能,簡單的方法就是在重要信號孔周圍增加地孔隔離。

以下四種方案信號孔/地孔(S G) 比分別為1∶1,1∶2,1∶3,1∶4,信號布局方式采取第2.2節(jié)中正交布局方式,如圖10所示。

圖10 不同S G 比信號布局

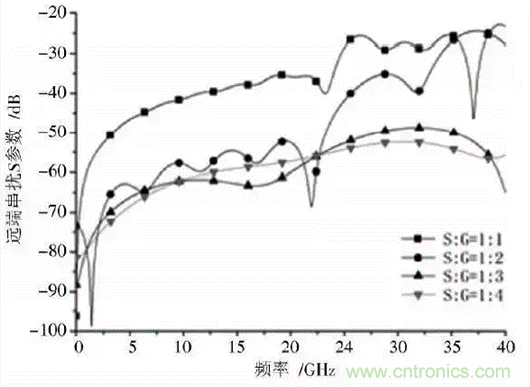

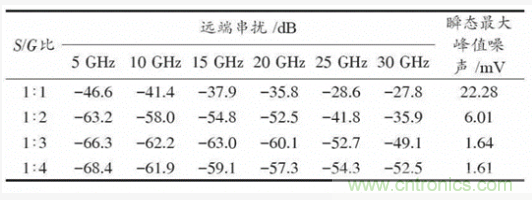

四種方案遠(yuǎn)端串?dāng)_比較如圖11所示,S G 比為1∶2時,差分信號的遠(yuǎn)端串?dāng)_要比1∶1時有很大改善。由表2可知,在5~30 GHz頻段,S G 比1∶2比1∶1遠(yuǎn)端串?dāng)_降低了8~17 dB。

在重要信號孔周圍增加地孔隔離,能夠縮短地回流路徑、降低信號過孔的電感不連續(xù)性,因此可以在一定程度上改善串?dāng)_,但是很快就會飽和,S G 比1∶4與1∶3時差別已然不大,遠(yuǎn)端串?dāng)_的改善很有限。

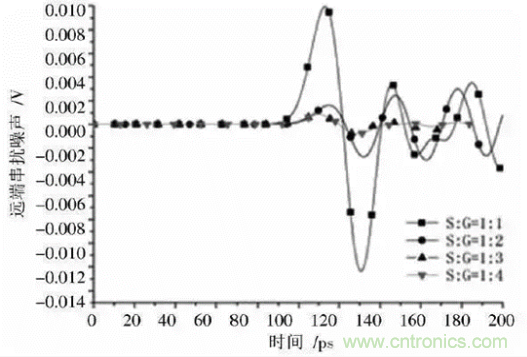

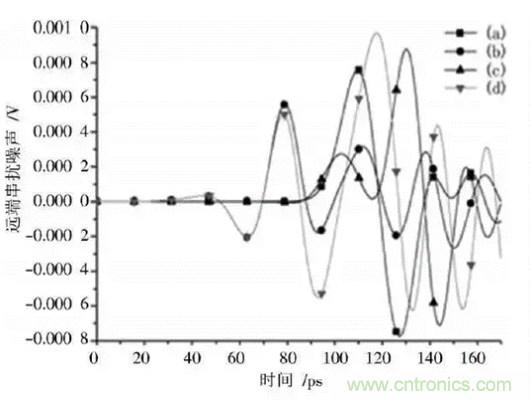

4種方案遠(yuǎn)端串?dāng)_的時域仿真結(jié)果如圖12所示,可以得到與頻域同樣的分析結(jié)果。從時域結(jié)果可得到4種方案的瞬態(tài)峰值噪聲,S G 比1∶1時高達(dá)22 mV,1∶2時則很快降低到6 mV,1∶3和1∶4時均在1.6 mV左右,相差不到0.03 mV,如表2所示。

圖11 四種方案遠(yuǎn)端串?dāng)_比較

圖12 四種方案遠(yuǎn)端串?dāng)_時域響應(yīng)比較

表2 遠(yuǎn)端串?dāng)_比較

由于BGA封裝引腳數(shù)量有限,并不能無上限地增加地孔數(shù)量。在串?dāng)_影響和引腳數(shù)量的權(quán)衡之下,20 GHz以內(nèi)S G 比1∶2與1∶3區(qū)別不大,選擇1∶2即可。20 GHz以上時,S G 比1∶3要明顯優(yōu)于1∶2。

2.4 布線層選擇與過孔Stub的影響

在重要信號孔周圍增加地孔隔離是降低串?dāng)_簡單的方法,但是很快就飽和了,而且這樣很難達(dá)到一個理想的屏蔽。

在封裝與PCB互連區(qū)域,高速差分對之間除了孔的耦合,線耦合也都是引起串?dāng)_的重要因素。此刻,除了考慮之前的三個方面影響,還應(yīng)分析和研究布線層以及過孔殘樁對串?dāng)_的影響。

圖13的情況,三個差分對分別布在不同層且具有不同過孔Stub長度,信號正交布局,每對差分過孔周圍設(shè)置6個隔離地孔。圖13(a)中3個差分對都布在PCB第10層,靠近底層。圖13(b)中兩側(cè)的干擾線從第10層移到第3層,且將長Stub背鉆59.1 mil。

這樣兩邊干擾信號與中間受擾信號之間孔耦合的垂直長度顯著減少。圖13(c)與圖13(b)恰好相反,中間的受擾線布在第3層并且背鉆,兩邊干擾線布在第10 層。圖13(d)中間受擾線布在第10層,兩邊干擾線布在第3層且保留長Stub。

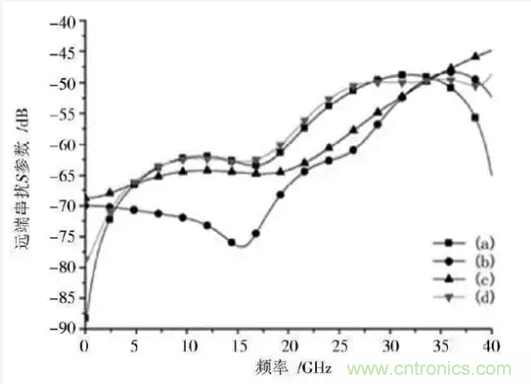

遠(yuǎn)端串?dāng)_的頻域比較如圖14 所示,與方案(a)相比,方案(b)減小了兩邊干擾信號過孔的垂直長度,孔耦合減少,而且3對差分線不在同一層,線?線之間耦合也減小了,串?dāng)_會有很大改善。

由表3 可知,在5~30 GHz頻帶內(nèi),方案(b)比方案(a)遠(yuǎn)端串?dāng)_改善了4~12 dB。方案(c)與(b)的區(qū)別在于(c)有多余的孔線耦合,(c)中受擾線放在第3層且背鉆,干擾線放在第10層,雖然孔耦合也可以減小,但是兩邊長長的干擾信號孔會對中間差分線產(chǎn)生線干擾。

而方案(b)中,由于干擾信號孔背鉆,受擾信號在經(jīng)過時,并沒有長Stub對差分線的干擾。由此,方案(b)的串?dāng)_是的。如果沒有背鉆,如方案(d),雖然三對信號差分線不在同一層,但長長的Stub不僅會影響阻抗的連續(xù)性,使自身差分信號產(chǎn)生諧振,還會增大相鄰差分信號之間的串?dāng)_,甚至都不如方案(a)將信號都布置在靠近底層。

圖14 四種方案遠(yuǎn)端串?dāng)_比較

從時域仿真結(jié)果中可以得到與頻域同樣的分析結(jié)果,如圖15所示。由表3可知,四種方案的瞬態(tài)峰值噪聲,方案(b),方案(d)。因此,在今后的設(shè)計中,為避免過孔長Stub對信號的干擾,差分線應(yīng)盡量靠近PCB板底層布線,多走內(nèi)部帶狀線。

幾對并行的差分信號可分別布置在不同信號層以降低串?dāng)_,但要注意布在淺層的信號過孔一定要背鉆。

圖15 四種方案遠(yuǎn)端串?dāng)_時域響應(yīng)比較

表3 遠(yuǎn)端串?dāng)_比較

3、實驗結(jié)果比較與分析

通過對以上仿真結(jié)果進(jìn)行比較與分析,可以得到如下設(shè)計和優(yōu)化建議:

(1)差分信號從過孔引出時,為滿足等長等距的要求,應(yīng)盡量采用水平對稱的布線方式,以達(dá)到的傳輸性能和的共模噪聲。如果布線時無法做到的水平對稱,45°轉(zhuǎn)角布線要優(yōu)于90°轉(zhuǎn)角布線。

(2)BGA封裝信號引腳布局采用正交方式,可充分降低差分對之間串?dāng)_的影響。與水平布局相比,正交布局在5~30 GHz頻帶內(nèi)串?dāng)_有5~15 dB的改善。

(3)在重要信號孔周圍增加地孔隔離,可以在一定程度上改善串?dāng)_,但是很快就會飽和,由仿真結(jié)果可知:20 GHz以內(nèi)給每一對信號孔周圍布置4個地孔,就可以很好的降低差分信號間的串?dāng)_,滿足信號完整性要求。20 GHz以上時,可在某些高速信號周圍布置6個隔離地孔,以改善信號之間的串?dāng)_。

(4)在選擇布線層時,為避免過孔長Stub對信號的干擾,差分線應(yīng)盡量靠近PCB板底層布線,走內(nèi)部帶狀線。如果很多對差分對并行傳輸,幾對差分信號可分別布置在不同信號層以降低串?dāng)_,但要注意布在淺層的差分信號過孔一定要背鉆。

4、結(jié)論

本文通過對高速BGA封裝與PCB差分互連結(jié)構(gòu)的優(yōu)化設(shè)計,利用CST全波電磁場仿真軟件進(jìn)行3D建模,分別研究了差分布線方式、信號布局方式、信號孔/地孔比、布線層與過孔殘樁這四個方面對高速差分信號傳輸性能和串?dāng)_的具體影響。

時頻域仿真結(jié)果表明,所述優(yōu)化方法能夠有效改善高速差分信號傳輸性能,減小差分信號間串?dāng)_,實現(xiàn)更好的信號隔離。

為保證高速信號傳輸系統(tǒng)的信號完整性提供了重要依據(jù),對于高速PCB設(shè)計具有一定的指導(dǎo)意義。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進(jìn)行侵刪。