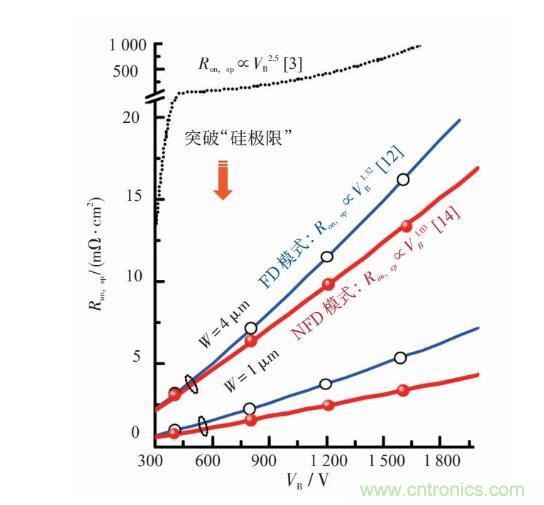

【導讀】超結(jié)功率半導體器件是一類具有超結(jié)耐壓層的重要器件,超結(jié)將PN結(jié)引入到常規(guī)“電阻型”耐壓層中,使之質(zhì)變?yōu)?ldquo;結(jié)型耐壓層”,這種質(zhì)變突破傳統(tǒng)功率器件比導通電阻和耐壓之間的Ron,sp ∝VB2.5“硅極限”關(guān)系,使之降低到Ron,sp ∝VB1.32,甚至 Ron,sp ∝VB1.03,超結(jié)器件也因此被譽為功率半導體器件的“里程碑”。從耐壓層角度回顧功率半導體40年發(fā)展的3個里程碑,綜述了超結(jié)的發(fā)明、概念與機理、技術(shù)與新結(jié)構(gòu),并總結(jié)超結(jié)發(fā)展歷程與趨勢。

摘 要

超結(jié)功率半導體器件是一類具有超結(jié)耐壓層的重要器件,超結(jié)將PN結(jié)引入到常規(guī)“電阻型”耐壓層中,使之質(zhì)變?yōu)?ldquo;結(jié)型耐壓層”,這種質(zhì)變突破傳統(tǒng)功率器件比導通電阻和耐壓之間的Ron,sp ∝VB2.5“硅極限”關(guān)系,使之降低到Ron,sp ∝VB1.32,甚至 Ron,sp ∝VB1.03,超結(jié)器件也因此被譽為功率半導體器件的“里程碑”。從耐壓層角度回顧功率半導體40年發(fā)展的3個里程碑,綜述了超結(jié)的發(fā)明、概念與機理、技術(shù)與新結(jié)構(gòu),并總結(jié)超結(jié)發(fā)展歷程與趨勢。

引 言

功率半導體器件是電能轉(zhuǎn)換與控制的核心器件,所有電子產(chǎn)品均離不開功率半導體器件,無論是毫瓦級的便攜式終端,還是兆瓦級的高鐵?,F(xiàn)代功率半導體技術(shù)已被廣泛應用于國民經(jīng)濟的方方面面,從傳統(tǒng)的工業(yè)電子、擴展到信息通訊、計算機、消費和汽車領域,新能源、軌道交通、電動汽車和智能電網(wǎng)正成為功率半導體市場增長的強大引擎。

在這些應用中,功率MOS和以其為核心的功率集成芯片在整個功率半導體市場份額占比高達74%,在2016年功率單管的118億的銷售中,功率MOS占比達 49%(IHS iSuppli Research,August 30,2017)。超結(jié)的出現(xiàn),使得器件比導通電阻大幅降,被國際上譽為“功率MOS器件的里程碑”,超結(jié)的優(yōu)越特性也帶來了巨大的市場需求,有人預計2020年市場規(guī)模將高達22億美元,功率芯片已被視為中國半導體破局的重要領域。

1.功率半導體器件結(jié)構(gòu)3個里程碑

1.1 功率半導體器件與耐壓層

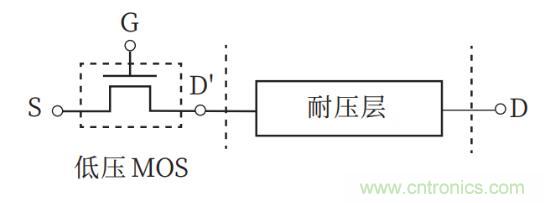

與低壓半導體器件相比,功率半導體器件關(guān)態(tài)條件下需承受高電壓,具有耐壓層結(jié)構(gòu),可以看成低壓控制器件與耐壓層形成的復合結(jié)構(gòu)。如圖1所示,功率MOS器件可視為低壓MOS漏端D與準漏端D''之間插入耐壓層的復合結(jié)構(gòu),其控制部分工作機理與低壓MOS基本相同。功率半導體器件設計的關(guān)鍵之一是耐壓層的設計。

圖1.簡化的血糖儀(BGM)框圖

圖1.功率半導體簡化結(jié)構(gòu)

理想的耐壓層應在關(guān)態(tài)下承受高電壓,在開態(tài)下導通大電流,并實現(xiàn)兩者之間的快速轉(zhuǎn)換。因此,其基本要求是高耐壓、低導通電阻和高開關(guān)速度,其優(yōu)化的本質(zhì)就是實現(xiàn)特定應用場景下的最佳折衷。

1.2 功率半導體器件結(jié)構(gòu)3個里程碑

20世紀70年代發(fā)明的VDMOS,為承受高耐壓采用具有單一導電型的“電阻型”耐壓層,人們很快發(fā)現(xiàn)其比導通電阻和耐壓之間存在Ron,sp ∝VB2.5極限關(guān)系,使器件功耗隨耐壓劇增。大量研究致力于如何使器件性能盡可能接近甚至突破“硅極限”,從耐壓層演變角度,需要在保證耐壓前提下盡可能增加開態(tài)載流子濃度,功率半導體器件呈現(xiàn)了不同的發(fā)展階段。

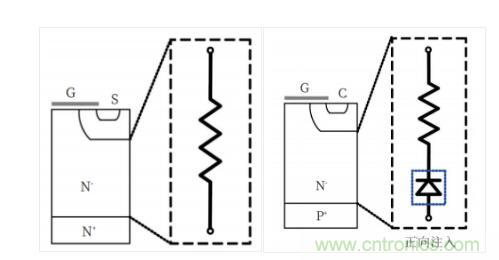

圖2給出功率半導體40年發(fā)展的3個里程碑:(a)里程碑I阻型耐壓層器件,器件耐壓層為具有N或P單一導電類型的低摻雜半導體層,其特性受“硅極限”限制,典型結(jié)構(gòu)為常規(guī)VDMOS器件;(b)里程碑II電導增強阻型耐壓層,通過將PN結(jié)正向注入特性引入到阻型耐壓層中,大注入非平衡載流子增加開態(tài)載流子濃度,典型結(jié)構(gòu)為IGBT;(c)里程碑III結(jié)型耐壓層,將異型摻雜引入到耐壓層內(nèi)部形成周期性交替摻雜的耐壓層結(jié)構(gòu),其特點是將PN結(jié)反向耗盡特性引入到耐壓層內(nèi)部,實現(xiàn)兩區(qū)之間的電荷平衡,典型結(jié)構(gòu)為本文重點闡述的超結(jié),耐壓層從“阻型”到“結(jié)型”的轉(zhuǎn)變?yōu)槟蛪簩咏Y(jié)構(gòu)的一次質(zhì)變。

(a)里程碑Ⅰ:阻型耐壓層 (b) 里程碑Ⅱ:阻型+正向注入

(c)里程碑Ⅲ:結(jié)型耐壓層

圖2.功率半導體器件40年發(fā)展的3個里程碑

從上面的論述可以看出,耐壓層演變的特點是巧妙地將PN結(jié)的正向與反向特性引入常規(guī)阻型耐壓層中,從而實現(xiàn)耐壓層電阻降低。

2.超結(jié)概念與機理

2.1 二維電荷場調(diào)制與電荷平衡

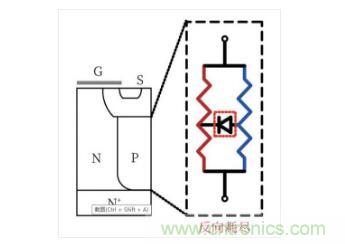

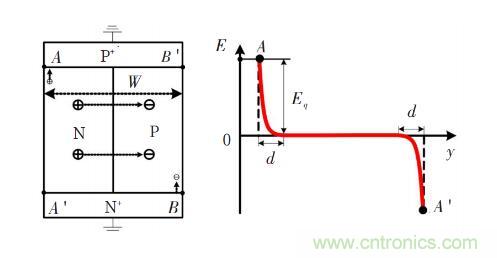

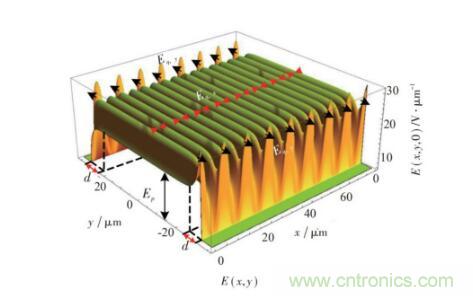

與阻型耐壓層相比,超結(jié)結(jié)型耐壓層由于內(nèi)部引入PN結(jié),關(guān)態(tài)條件下N區(qū)電離正電荷發(fā)出電場線大部分流向毗鄰P區(qū)電離負電荷,在耐壓層內(nèi)部引入顯著的二維場效應,這種復雜場調(diào)制極大降低器件表面電場峰值并優(yōu)化了體內(nèi)場分布。結(jié)型耐壓層電場線與零電勢邊界條件下由電離電荷產(chǎn)生的電荷場Eq(x,y) 分布,如圖3所示,其中W為超結(jié)條寬度,由于耐壓層內(nèi)部電場線橫向流走,導致AA′上大部分區(qū)域電離電荷產(chǎn)生縱向場為零,只有在表面A點所在P+N結(jié)位置產(chǎn)生局部電場分布,高電場在縱向很短的距離d(據(jù)筆者計算d≈0.78W)范圍內(nèi)以指數(shù)函數(shù)迅速衰減,由于對稱性在A′點產(chǎn)生負的電場峰值,BB′線上電場可以類似分析。

圖3.超結(jié)電荷場分布

上述橫向電荷場對縱向電荷場調(diào)制使得超結(jié)關(guān)態(tài)條件下二維場分布如圖4所示,結(jié)型耐壓層內(nèi)部電場呈周期函數(shù)分布,以耐壓層縱向中線電場為例,峰值位于每個PN結(jié)面,谷值位于每個P條或N條中心位置。器件結(jié)型耐壓層端面亦呈現(xiàn)周期性峰值分布,與內(nèi)部不同,其波峰與波谷皆位于每個P條或N條中心位置上,峰值位于上表面P+N結(jié)或者下表面N+P結(jié)位置,而谷值位于P+P或N+N結(jié)位置。縱向高電場局限在W距離內(nèi),因此耐壓層內(nèi)部縱向場分布幾乎不受影響。且隨長度增加,高場區(qū)保持相同分布且與表面相對位置不變。

圖4.超結(jié)二維電場分布

常規(guī)理論認為,理想的超結(jié)器件需滿足耐壓層內(nèi)部電場線全部從N區(qū)指向P區(qū),即滿足電荷平衡條件以實現(xiàn)縱向場分量為矩形,電荷非平衡將導致器件耐壓降低。然而筆者發(fā)現(xiàn),在開態(tài)條件下,當考慮載流子電荷影響時,巧妙應用電荷非平衡可以降低器件損耗并增加器件的安全工作區(qū)。

2.2 超結(jié)理論發(fā)展

超結(jié)器件出現(xiàn)后,不同研究者分別對其進行理論分析:一維近似法將超結(jié)在耐壓方向上視為具有均勻場的一維PIN、垂直耐壓方向上視為一維PN結(jié),兩個方向上電場同時達到Ec時最優(yōu)?;蛘邔⒊Y(jié)電場看成耐壓方向與垂直耐壓方向上兩個一維場的疊加,可得到類似結(jié)果。一維近似主要用于超結(jié)器件的概念分析或者參數(shù)估算。

超結(jié)二維場優(yōu)化法建立在二維精確解析場分布的基礎上,其二維精確解在超結(jié)發(fā)明后很長一段時間才于1998年由電子科技大學陳星弼院士率先提出,進一步將擊穿時耐壓層恰好全耗盡選為優(yōu)化條件,從而獲得經(jīng)典Ron,sp ∝VB1.32關(guān)系。此外,還提出一種分區(qū)求解二維泊松方程的方法,結(jié)論類似,不再贅述。

上述優(yōu)化方法均未給出超結(jié)器件的最低比導通電阻Ron,min。由于超結(jié)二維場調(diào)制效應,研究發(fā)現(xiàn)擊穿條件下圖3中A ′和B ′局部非全耗盡時器件Ron,sp更低,筆者團隊基于該特性提出超結(jié)非全耗盡(nonfull depletion,NFD)模式,通過全域Ron,sp優(yōu)化尋求Ron,min,理論上證明新模式下平衡對稱超結(jié)滿足:

Ron,sp=1.437×10-3W1.108VB1.03(mΩ·cm²)(1)

圖5給出超結(jié)Ron,sp-VB關(guān)系與傳統(tǒng)硅極限Ron,sp ∝ VB2.5關(guān)系比較,與傳統(tǒng)“硅極限”相比,超結(jié)器件Ron,sp正比于超結(jié)條寬度W,依賴于元胞尺寸,因此在一定范圍內(nèi)(W>0.2μm)可以通過工藝改進縮小元胞寬度增加摻雜濃度的形式進一步降低Ron,sp。

圖5.超結(jié)與Ron,sp - VB關(guān)系與傳統(tǒng)“硅極限”比較

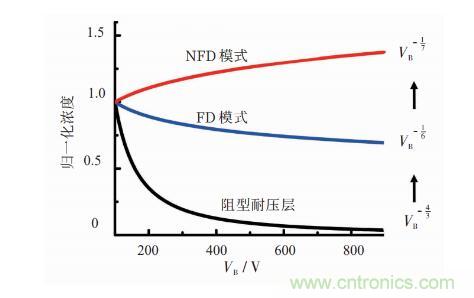

器件Ron,sp主要由耐壓層長度與摻雜濃度決定,為實現(xiàn)高擊穿電壓,不同類型的耐壓層長度無顯著差異,因此超結(jié)突破常規(guī)“硅極限”的實質(zhì)是突破了器件摻雜濃度與VB的依賴關(guān)系。圖6給出NFD、FD超結(jié)與常規(guī)阻型耐壓層濃度變化規(guī)律,圖中采用100V器件優(yōu)化摻雜濃度進行歸一化。由于阻型耐壓層摻雜濃度依賴于耐壓層長度,其優(yōu)化摻雜濃度隨VB顯著降低,而NFD超結(jié)摻雜濃度甚至隨 VB略有增加。這種變化源于結(jié)型耐壓層摻雜劑量由超結(jié)條寬度W決定,且?guī)缀酹毩⒂谀蛪簩娱L度。

圖6.歸一化摻雜濃度比較

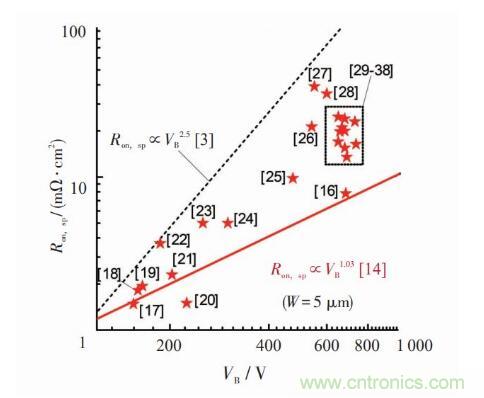

圖7表明超結(jié)在不同耐壓級別上都實現(xiàn)了對“硅極限”的突破。以文獻中實驗結(jié)果為例,分別采用寬度為1.3μm的P條和1.7μm的N條,實現(xiàn)VB為685V,Ron,sp僅為7.8mΩ·cm²,傳統(tǒng)“硅極限”在相同VB下Ron,sp為 101.9mΩ·cm²,超結(jié)器件Ron,sp降低了一個數(shù)量級。目前實驗獲得的超結(jié) Ron,sp主要位于式(1)中W為5μm所對應關(guān)系以上。

圖7.超結(jié)Ron,sp水平

超結(jié)概念也被引入到橫向器件中以降低器件的功率損耗,由于橫向超結(jié)可以通過表面注入形成且與常規(guī)CMOS工藝兼容,橫向超結(jié)器件已成為高壓功率集成技術(shù)的重要發(fā)展方向。與縱向超結(jié)器件不同,橫向器件常常將超結(jié)置于P型襯底之上,表面超結(jié)區(qū)由于受到襯底輔助耗盡(substrate-assisted depletion,SAD)效應的影響,導致耐壓降低。

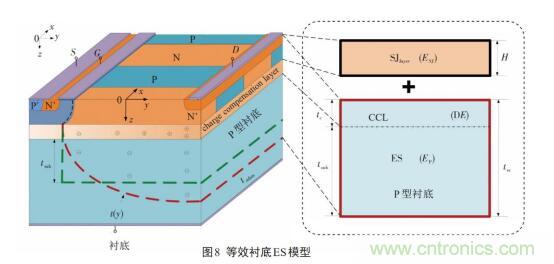

襯底輔助耗盡效應可以通過等效襯底(equivalent substrate,ES)模型描述 ,其原理如圖8所示。將除超結(jié)之外的耐壓結(jié)構(gòu),即電荷補償層(chargecompensation layer,CCL)與襯底視為一個整體,定義為等效襯底ES,研究其整體對表面超結(jié)的調(diào)制作用。

圖8.等效襯底ES模型

ES模型揭示了襯底輔助耗盡效應的本質(zhì)是襯底電離電荷影響表面超結(jié)電荷平衡,致使P條非全耗盡而N條全耗盡,器件耐壓降低。為消除其影響,理論上ES層需滿足的理想襯底條件:

(a)電中性條件:ES凈電荷QES→0,等效襯底為準電中性,超結(jié)中N區(qū)和P區(qū)之間的電荷平衡得以滿足。

(b)均勻表面場條件:E (x,y,0) = 常數(shù),等效襯底均勻表面場條件避免器件表面提前擊穿。

一種實現(xiàn)理想襯底條件的版圖如圖9所示,在超結(jié)耐壓方向上通過開不同窗口形成優(yōu)化摻雜分布使得CCL與襯底保持電荷平衡,同時調(diào)制ES電場實現(xiàn)矩形分布。

圖9.滿足理想襯底條件的橫向超結(jié)版圖

3.超結(jié)工藝技術(shù)與新結(jié)構(gòu)

由于結(jié)型耐壓層實現(xiàn)難度較大,很長一段時間內(nèi)對超結(jié)器件的研究主要體現(xiàn)在工藝上,包括耐壓層實現(xiàn)技術(shù)與終端技術(shù)。同時將超結(jié)耐壓層用于不同的功率半導體器件中,實現(xiàn)特性改善或形成新型功率半導體器件。

3.1 工藝技術(shù)

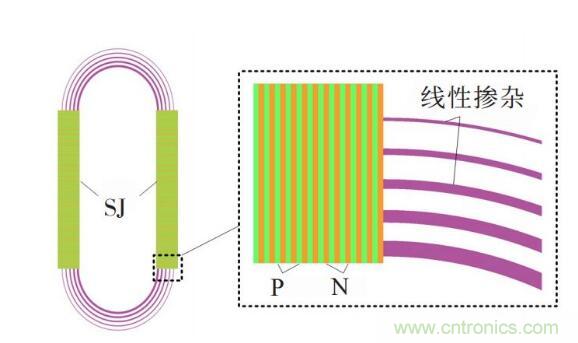

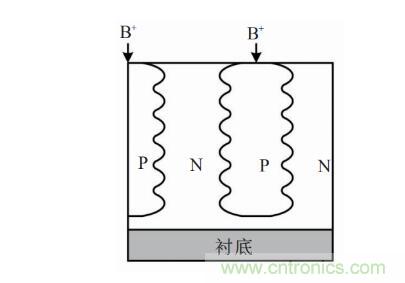

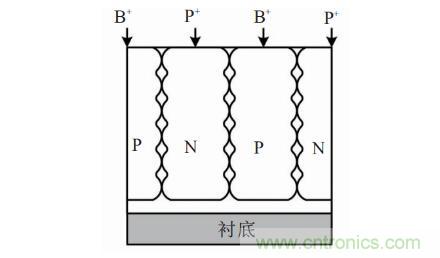

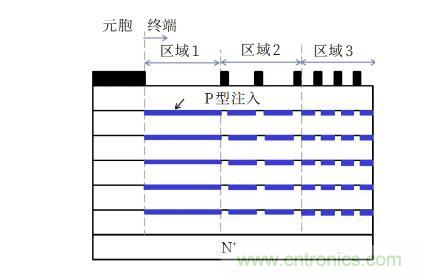

超結(jié)工藝的難點是如何在耐壓層內(nèi)部引入周期性的異型摻雜,如圖10所示為多次外延摻雜工藝,其中第一種方法通過多次外延一定濃度的N型區(qū),然后僅采用P型注入補償形成超結(jié)P區(qū);第二種方法是每次外延濃度較低,然后同時引入N和P型注入,分別形成超結(jié)的N區(qū)和P區(qū),第二種工藝可以控制更好的均勻性,但工藝上需增加一次光刻與注入。此類工藝的優(yōu)點是形成超結(jié)耐壓層的晶格質(zhì)量較好,缺陷與界面態(tài)少。然而為形成較好超結(jié)形貌,每次外延層厚度相對固定且較薄,外延次數(shù)將隨著器件耐壓增大而增多,導致成本增加。

(a)單雜質(zhì)注入

(b)雙雜質(zhì)注入

圖10.多次外延工藝

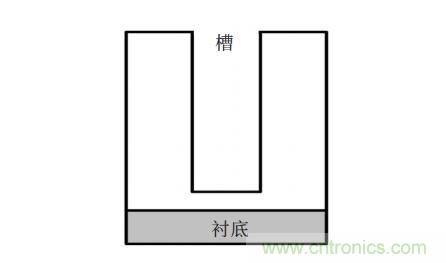

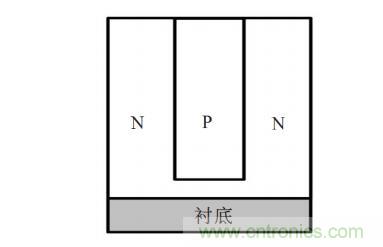

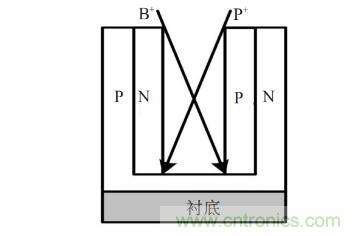

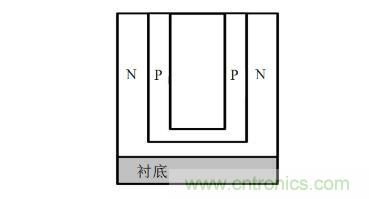

另一種結(jié)型耐壓層實現(xiàn)工藝基于深槽刻蝕,如圖11所示,其中圖11(a)給出具有刻蝕槽的耐壓層結(jié)構(gòu)。通過在超結(jié)耐壓層中刻蝕形成一定深寬比的槽,再對槽內(nèi)部摻雜。第一種方式是在槽內(nèi)外延填充P型硅,然后采用化學機械拋光平坦化實現(xiàn)超結(jié)耐壓層,拋光后耐壓層如圖11(b)所示。還可以在槽壁上形成薄氧化層結(jié)構(gòu),再進行多晶硅填充形成耐壓層;第2種方式是采用傾斜注入分別在槽壁上形成N區(qū)和P區(qū),這樣可以控制N和P型雜質(zhì)的注入劑量來實現(xiàn)電荷平衡,如圖11(c)所 示;第3種方式通過對槽壁氣相摻雜形成P型區(qū),如圖11(d)所示。此外,還可以在槽壁選擇性外延薄層N與P型硅或者是直接通過P型雜質(zhì)擴散形成超結(jié)耐壓層。采用刻槽填充工藝實現(xiàn)的超結(jié)耐壓層較多次外延技術(shù)更易實現(xiàn)較小的深寬比,同時形成的超結(jié)N區(qū)與P區(qū)摻雜分布也較均勻,有利于降低 Ron,sp。

(a)深槽刻蝕工藝

(b)外延填充

(c)斜角注入摻雜

(d)氣象摻雜

圖11.深槽工藝

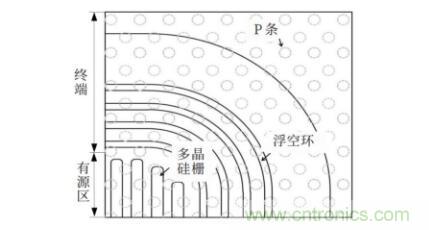

為實現(xiàn)超結(jié)器件終端區(qū)高耐壓,有兩種典型超結(jié)器件終端結(jié)構(gòu),如圖12所示。圖12(a)表示具有變摻雜的終端結(jié)構(gòu),對多外延型工藝,可以改變P型注入?yún)^(qū)窗口,P型摻雜濃度從元胞到終端方向逐漸降低,保持終端區(qū)新的電荷平衡?;谏畈劭涛g的超結(jié)器件則主要通過優(yōu)化終端區(qū)刻蝕窗口來實現(xiàn)類似變摻雜終端。圖12(b)給出采用常規(guī)表面終端技術(shù)的超結(jié)器件終端結(jié)構(gòu),其特點是將結(jié)型耐壓層埋入器件體內(nèi),減少超結(jié)內(nèi)部PN結(jié)對器件表面場的影響,同時在器件終端區(qū)表面采用常規(guī)結(jié)終端技術(shù)實現(xiàn)高耐壓。

(a)變摻雜終端

(b)表面終端技術(shù)

圖12.典型超結(jié)器件終端結(jié)構(gòu)

超結(jié)不僅可以用來降低器件比導通電阻,同時可用以優(yōu)化電場分布,如圖13所示為基于超結(jié)的終端結(jié)構(gòu),在常規(guī)浮空場限環(huán)間引入表面超結(jié),建立新的電荷平衡,削弱了界面寄生電荷的影響,縮小終端區(qū)面積。

圖13.基于超結(jié)的終端結(jié)構(gòu)

對橫向叉指型超結(jié)器件而言,由于表面超結(jié)結(jié)深較淺,容易在終端指尖位置提前擊穿,為解決此問題,作者團隊提出如圖14所示的襯底終端技術(shù),通過將部分襯底電荷引入到器件表面,降低曲率效應,實現(xiàn)終端區(qū)新的電荷平衡,提高器件耐壓,且具有工藝兼容的優(yōu)點。

圖14.襯底終端結(jié)構(gòu)

3.2 超結(jié)新結(jié)構(gòu)

3.2.1 縱向超結(jié)結(jié)構(gòu)

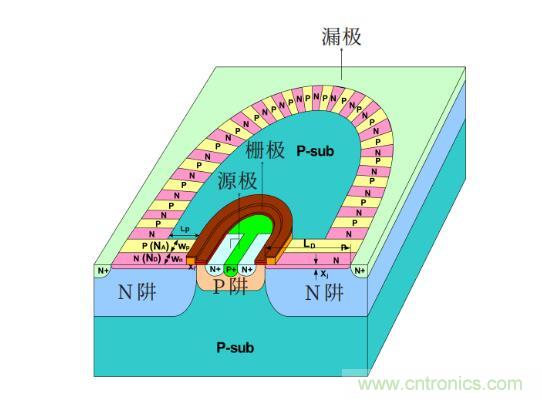

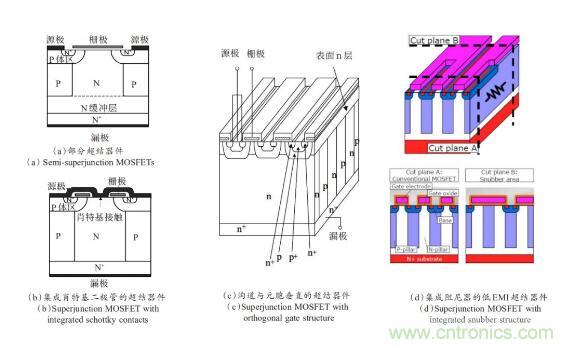

對超結(jié)功率MOS器件而言,大量新結(jié)構(gòu)致力于如何利用兼容工藝改善器件特性,圖15給出幾種改善器件特性的典型結(jié)構(gòu)。圖15(a)為部分超結(jié)結(jié)構(gòu),超結(jié)器件給定元胞寬度下N區(qū)和P區(qū)的深寬比隨器件VB增加而增加,工藝難度增加。部分超結(jié)結(jié)構(gòu)降低工藝難度,在相同深寬比條件下實現(xiàn)比全超結(jié)器件更低的Ron,sp且利于器件的反向恢復特性。

為了改善超結(jié)體二極管的反向恢復特性,通過集成肖特基二極管,提出如圖 15(b)所示的變形結(jié)構(gòu),通過肖特基結(jié)的反向抽取作用,削弱載流子存儲效應;隨著器件元胞寬度的進一步縮小,可能導致超結(jié)兩個P條之間距離過小難以形成溝道區(qū),因此提出如圖15(c)所示的溝道與超結(jié)元胞相垂直的結(jié)構(gòu),該結(jié)構(gòu)適用于窄元胞器件,減少溝道區(qū)工藝難度;此外還可以通過版圖優(yōu)化減少部分溝道區(qū)面積,以實現(xiàn)更低的電磁干擾(EMI)噪聲。

圖15.改善超結(jié)MOS特性的新結(jié)構(gòu)

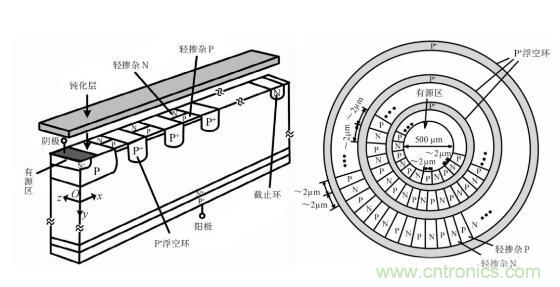

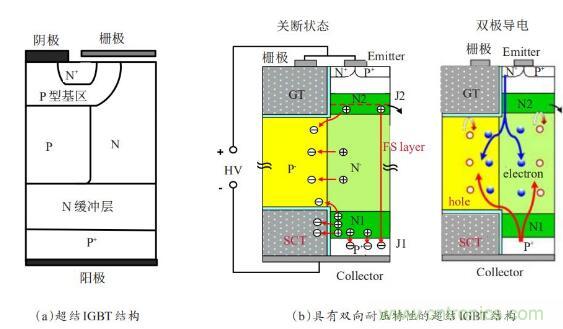

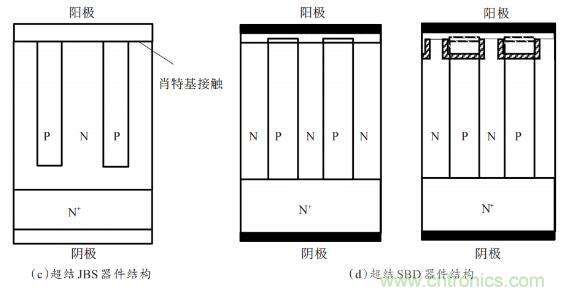

超結(jié)作為一種典型的結(jié)型耐壓層結(jié)構(gòu),用于不同的器件可實現(xiàn)不同的功率半導體器件,典型結(jié)構(gòu)如圖16所示。圖 16(a)為超結(jié)IGBT結(jié)構(gòu),與傳統(tǒng)IGBT相比,超結(jié)IGBT一方面通過電場調(diào)制縮小漂移區(qū)長度,另一方面還可以引入準單極傳導模式,即大注入電子和空穴分別流經(jīng)低阻的超結(jié)N區(qū)和P區(qū),器件關(guān)斷時通過內(nèi)部PN結(jié)耗盡區(qū)擴展可以迅速抽取過剩載流子,實現(xiàn)快速關(guān)斷;作者團隊提出如圖16(b)所示的具有雙向耐壓特性的超結(jié)IGBT結(jié)構(gòu),該結(jié)構(gòu)打破了一般超結(jié)IGBT正向壓降與超結(jié)區(qū)摻雜的依賴關(guān)系,實現(xiàn)開態(tài)雙極高電導調(diào)制與關(guān)態(tài)準單極關(guān)斷特性。如果將超結(jié)耐壓層用于二極管結(jié)構(gòu),則形成圖16(c)和 16(d)所示的超結(jié)junctionbarrier schottky rectifier(JBS)和 schottky barrier diode(SBD)器件結(jié)構(gòu),由于超結(jié)區(qū)的摻雜濃度很高,肖特基結(jié)開啟后有更小的正向壓降和更大的電流密度。同時由于反向阻斷狀態(tài)下P區(qū)之間的N型漂移區(qū)的耗盡層重疊形成勢壘,使器件反向漏電流降低。超結(jié)SBD器件還可采用槽型電極結(jié)構(gòu)來降低肖特基接觸位置的電場,降低反向漏電。

圖16.具有超結(jié)耐壓層的新型功率半導體器件

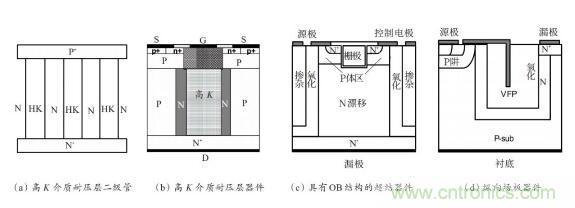

電荷平衡不僅可以通過PN結(jié)電離電荷實現(xiàn),還可以通過金屬絕緣層半導體(metal insulator semiconductor,MIS)介質(zhì)耦合實現(xiàn),如圖17所示。其中圖17(a)和圖17(b)為具有高K介質(zhì)的復合耐壓層結(jié)構(gòu),器件耐壓時大部分電通量通過高K介質(zhì)流向表面,從而優(yōu)化了硅層區(qū)電場;圖17(c)和圖17(d)為典型的體內(nèi)場板結(jié)構(gòu),通過體內(nèi)場板在耐壓層內(nèi)部引入電荷,與硅層電離電荷保持平衡,優(yōu)化體內(nèi)電場降低器件Ron,sp。

圖17.采用電荷平衡概念的新結(jié)構(gòu)

3.2.2 橫向超結(jié)結(jié)構(gòu)

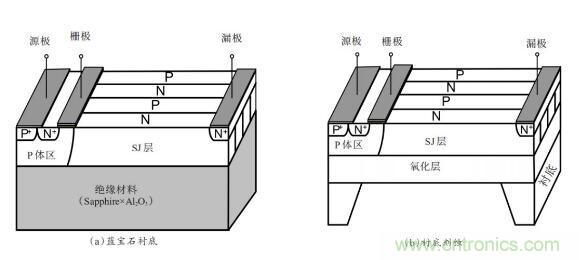

橫向超結(jié)器件的發(fā)展主要集中在如何消除襯底輔助耗盡效應,典型方法有兩種。第1種方法如圖18所示,通過采用圖18(a)藍寶石襯底或者圖18(b)刻蝕去除硅襯底,其共同點都是消除襯底電位對表面超結(jié)區(qū)的影響,解決縱向耐壓低的問題。該方法可以很好地抑制襯底輔助耗盡效應,但具有工藝不兼容或者材料成本高的特點。

圖18.去除襯底影響的橫向超結(jié)結(jié)構(gòu)

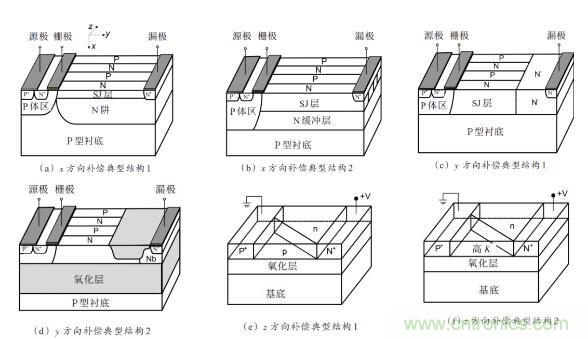

第2種方法如圖19所示,其基本思想是電荷補償,通過在耐壓層中引入補償電荷,與襯底電離電荷保持電荷平衡從而抑制襯底輔助耗盡效應的影響。從空間維度可以分為圖19(a)、圖19(b)x方向補償,主要是通過在超結(jié)區(qū)下方添加深N阱或者N緩沖層的形式實現(xiàn);圖19(c)、圖19(d)y方向補償,超結(jié)區(qū)位于靠近源區(qū),漏區(qū)為單一摻雜的N型摻雜,特別對SOI器件,為解決其耐壓較低的問題,可以采用局部薄層結(jié)構(gòu);圖19(e)、圖19(f)z方向補償,通過設計使超結(jié)N區(qū)和P區(qū)為非對稱形狀實現(xiàn)補償,與縱向器件類似,P區(qū)亦可采用高K介質(zhì)。

圖19.電荷補償橫向超結(jié)結(jié)構(gòu)

3.3 寬禁帶超結(jié)功率半導體器件

超結(jié)概念同樣被應用到寬禁帶半導體材料如SiC和GaN中,超結(jié)概念與理論完全適用,由于禁帶寬度更大,相同深寬比條件下,寬禁帶半導體超結(jié)器件對Ron,sp - VB關(guān)系的貢獻主要體現(xiàn)在系數(shù)項,可以降低約3個數(shù)量級,特別在超高壓領域非常具有吸引力。

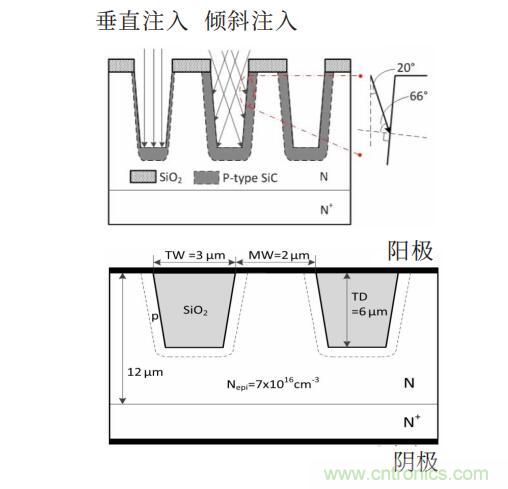

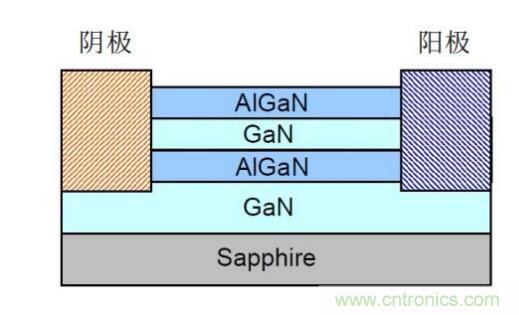

如圖20所示是典型SiC基超結(jié)器件,采用與硅基類似的深槽刻蝕注入摻雜工藝實現(xiàn),并且在槽內(nèi)填充介質(zhì)實現(xiàn)結(jié)型耐壓層結(jié)構(gòu),該工藝比較容易實現(xiàn)較高深寬比的超結(jié)區(qū)。對GaN材料而言,可以通過異型摻雜形成一般結(jié)型耐壓層結(jié)構(gòu),還可以利用疊層結(jié)構(gòu)中電荷平衡極化電荷同時形成二維電子氣與二維空穴氣,典型結(jié)構(gòu)如圖21所示。器件開態(tài)時電子氣和空穴氣同時參與導電,降低器件導通電阻,關(guān)態(tài)時極化電荷自動滿足電荷平衡,優(yōu)化耐壓層電場,從而形成新型的電荷平衡耐壓層結(jié)構(gòu)。

圖20.碳化硅基超結(jié)器件

圖21.氮化鎵基超結(jié)器件

3.4 超結(jié)功率半導體器件發(fā)展歷程

綜上所述,超結(jié)發(fā)展歷程如圖22所示。超結(jié)結(jié)型耐壓層高壓低比導通電阻特性可實現(xiàn)高功率密度與低成本下的低損耗,理論上實現(xiàn)比導通電阻與耐壓的從Ron,sp ∝VB2.5關(guān)系降低到Ron,sp ∝VB1.32甚至Ron,sp ∝VB1.03關(guān)系,橫向超結(jié)器件優(yōu)化可由等效襯底模型統(tǒng)一描述。

圖22.超結(jié)發(fā)展歷程

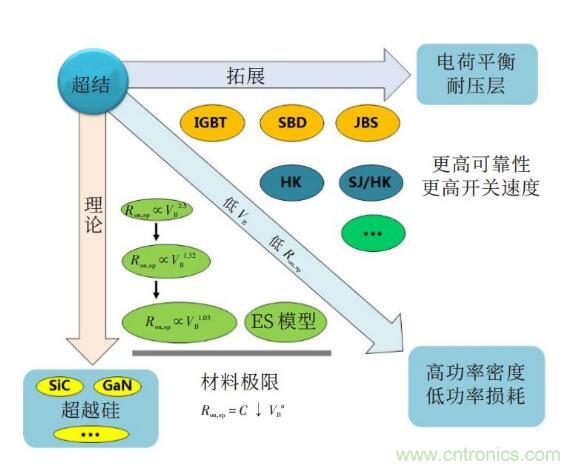

隨著元胞寬度進一步縮小,寄生JFET效應及齊納擊穿等變得更加顯著,經(jīng)筆者計算,齊納擊穿限制下硅基超結(jié)的條寬極限約為0.1~0.2μm;超結(jié)概念完全適用于SiC、GaN等其他半導體材料,突破對應“硅極限”關(guān)系;另一方面,超結(jié)概念還被拓展到IGBT、SBD等其他功率半導體器件中,實現(xiàn)電荷平衡的耐壓層結(jié)構(gòu),并向著更高可靠性、更高開關(guān)速度的方向發(fā)展。

4.超結(jié)功率半導體器件展望

總結(jié)起來,目前在理論方面已經(jīng)對超結(jié)器件做了較為深入的研究,獲得了其理論最低Ron,sp。然而,在實驗方面,超結(jié)器件特性仍有很大的提升空間,現(xiàn)有實驗結(jié)果與Ron,sp ∝VB1.03最低理論比導通電阻相比,在W為5~10μm范圍內(nèi),Ron,sp可以再降低20%~40%,而在W寬度為1~4μm范圍內(nèi),Ron,sp降低量達60%~80%,余量可觀。橫向超結(jié)器件是高壓功率集成技術(shù)的重要發(fā)展方向,目前研究主要集中在如何消除襯底輔助耗盡效應提高耐壓,然而超結(jié)本身優(yōu)越的低阻特性尚待挖掘,特別采用具有縱向高深寬比的超結(jié)可以大幅降低 Ron,sp,作者團隊開發(fā)的具有N-top的橫向超結(jié)器件以及多次注入形成的NFD 橫向超結(jié)器件,Ron,sp均較Triple RESUF器件更優(yōu)。因此橫向可集成超結(jié)器件有望成為Triple RESUF之后的下一代低阻可集成器件。

文獻來源:

張波, 章文通, 蒲松,等. 超結(jié)功率半導體器件[J]. 微納電子與智能制造, 2019, 1 (1): 5-19.

ZHANG Bo, ZHANG W T, PU S, et al. Superjunction power semiconductor devices[J]. Micro/nano Electronics and Intelligent Manufacturing, 2019, 1 (1): 5-19.

《微納電子與智能制造》刊號:CN10-1594/TN

主管單位:北京電子控股有限責任公司

主辦單位:北京市電子科技科技情報研究所 北京方略信息科技有限公司