【導讀】在物聯(lián)網(wǎng)和云計算成為生活一部分,在行業(yè)媒體大肆宣揚之際,通過采用最先進的技術和優(yōu)化設計,老式電子元件并未停止前進的步伐。其中一個例子是模數(shù)轉(zhuǎn)換器,該器件現(xiàn)在可以超過每秒一兆次采樣(MSPS)的速率實現(xiàn)32位分辨率,輕松通過傳統(tǒng)的計量基準測試。

在物聯(lián)網(wǎng)和云計算成為生活一部分,在行業(yè)媒體大肆宣揚之際,通過采用最先進的技術和優(yōu)化設計,老式電子元件并未停止前進的步伐。其中一個例子是模數(shù)轉(zhuǎn)換器,該器件現(xiàn)在可以超過每秒一兆次采樣(MSPS)的速率實現(xiàn)32位分辨率,輕松通過傳統(tǒng)的計量基準測試。

這些高精度轉(zhuǎn)換器可以顯示高于16位的分辨率,規(guī)定可比靜態(tài)和動態(tài)特性,并且在儀表儀器和大型通用采集系統(tǒng)(測試、設備認證)、專業(yè)系統(tǒng)(醫(yī)療應用和光譜學數(shù)字成像)等專用領域以外,它們已經(jīng)進入許多過程控制應用、可編程控制器、大型電機控制以及電能輸配等領域。目前,幾種ADC架構在精度方面不相上下;根據(jù)不同需求,具體的選擇視模數(shù)轉(zhuǎn)換原理、逐次逼近寄存器(SAR)以及∑-Δ而定,在數(shù)MSPS速率下,這些架構分別支持最高24位或以上的分辨率,為24位或更多,在幾百kSPS速率下支持32位分辨率。

當面對這些分辨率和精度水平時,這些轉(zhuǎn)換器提供的有用動態(tài)范圍很容易超過100dBFS(滿量程)的神奇屏障,用戶面臨的真正挑戰(zhàn)體現(xiàn)在為要數(shù)字化的信號設計模擬調(diào)理電路,以及相關抗混疊濾波器的設計兩個方面。在過去的二十年中,采樣速率和濾波技術已經(jīng)有了很大的發(fā)展,現(xiàn)在我們可以結合運用模擬和數(shù)字濾波器,在性能和復雜性之間達到更好的平衡。

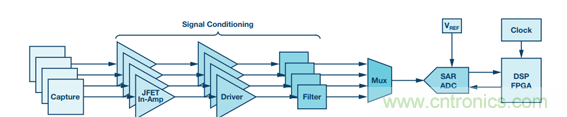

圖1. 典型測量信號鏈

圖1所示為適用于數(shù)據(jù)采集系統(tǒng)的這類分區(qū)的一個典型示例。在調(diào)節(jié)差分或非差分信號(放大、縮放、自適應和電平轉(zhuǎn)換等)之后,在數(shù)字化之前對后者進行濾波以滿足奈奎斯特準則。根據(jù)ADC的過采樣速率,要使用額外的數(shù)字濾波來達到采集系統(tǒng)的規(guī)格要求。

由于對超寬輸入動態(tài)范圍的需求增加,許多上述應用采用了最先進的高分辨率ADC。隨著動態(tài)范圍的增加,系統(tǒng)性能預計會提高,模擬調(diào)節(jié)鏈會減小,擁堵、能耗,甚至是材料成本都會下降。

過采樣及其好處

在超快高分辨率模數(shù)編碼器出現(xiàn)之前,一般通過以下辦法解決動態(tài)范圍問題:使用快速可編程增益放大器、更快的比較器和/或并聯(lián)若干ADC,最后加上合適的數(shù)字處理模塊,以實現(xiàn)強信號的數(shù)字化,區(qū)分接近噪聲水平的小信號。在這些陳舊并且現(xiàn)已過時的架構中,這樣做會帶來復雜的電路,很難開發(fā),并且在線性度、帶寬和采樣頻率方面都受到限制。當今的替代方案是,借助更經(jīng)濟的現(xiàn)代ADC的高采樣速率,達到運用過采樣技術的目的。

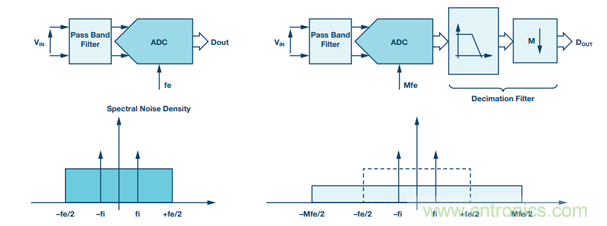

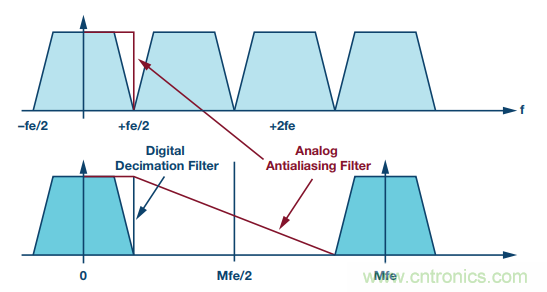

圖2.通過添加數(shù)字抽取濾波器比較頻譜噪聲密度

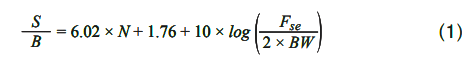

以高于奈奎斯特定理要求的最小值的FSE速率對信號進行采樣,可以通過處理和增加編碼器的信噪比來執(zhí)行增益運算,并因此增加有效位的數(shù)量。實際上,量化噪聲和熱噪聲被同化為白噪聲,該噪聲在整個奈奎斯特頻帶及以外均勻分布。過采樣之后,通過濾波和嚴格以最小所需采樣速率(或2×BW)限制有用頻帶,頻帶每降低一個倍頻程,噪聲能量將降低3dB,如圖2所示。換句話說,過采樣因子為4時最為理想,在理論上使信噪比增加了6dB;即是說,增加了一位,如等式1所示:

總之,過采樣有兩個優(yōu)點,一是可以提升信噪比,二是可以放寬對位于ADC之前的抗混疊模擬濾波器的要求。

抗混疊濾波器:分區(qū)困境

理想情況下,與ADC相關的濾波器,特別是那些負責解決頻譜混疊問題的濾波器,相比其精度,其幅度響應帶寬必須盡可能平坦,同時其帶外衰減還要能滿足其動態(tài)范圍要求。過渡帶一般要盡可能陡。因此,這些抗混疊低通濾波器在特性上有特定的要求,必須能消除寄生鏡像、噪聲和其他雜散音。根據(jù)具體應用,還要特別注意相位響應,也要補償任何過大的相移。雖然有許多建議被認為屬于基礎建議,但是,如果要將這些建議與指定的24位或32位轉(zhuǎn)換器的要求結合起來,并且這些轉(zhuǎn)換器的積分非線性誤差僅為幾LSB,再加上其他類似的靜態(tài)和動態(tài)參數(shù),有些建議實現(xiàn)起來會極其困難。

如前所述,過采樣在此非常重要,因為它不僅能提升信噪比,還能放寬對模擬抗混疊濾波器規(guī)格及其截止頻率的要求。如圖3所示,過采樣分布在-3dB條件下截止頻率與阻帶起點之間的過渡帶。

圖3.過采樣分布在-3dB條件下截止頻率與阻帶起點之間的過渡帶

最新的技術為近年來顯著提升的高精度SAR ADC轉(zhuǎn)換速率提供了可能,目前在18位分辨率下,此等轉(zhuǎn)換速率在1MSPS與15MSPS之間。相比之下,具有同等分辨率的寬帶∑-ΔADC的速率幾乎要低一個數(shù)量級,存在突出的延遲問題,并且其通帶紋波太高,無法用于數(shù)據(jù)采集系統(tǒng)、其他測量儀器儀表等應用?;径?,總體計量精度決定著后者的特性,這與靜態(tài)(dc)和動態(tài)(ac)參數(shù)都有關系,因此這些系統(tǒng)中的轉(zhuǎn)換器和附帶的模擬調(diào)理電路在規(guī)格上必須達到頂級要求。

這些規(guī)格包括失調(diào)、增益和對應的漂移誤差、積分非線性(INL)和差分(DNL)誤差等常見特性,還包括信噪比(SNR)、諧波失真和雜散音(無雜散動態(tài)范圍(SFDR))。SAR ADC在部分這些參數(shù)以及瞬態(tài)響應、模擬輸入過載和零延遲方面具有明顯的競爭優(yōu)勢(INL),為單次模式下多路輸入系統(tǒng)的運行或采集的觸發(fā)提供了保障。

相反,除LTC2512和LTC2500-32以外,大多數(shù)SAR ADC不包括數(shù)字濾波器,因此其運行不受一些不可避免的數(shù)字低通濾波的阻礙或限制,否則,就會在計算精度、帶通紋波、衰減阻帶抑制、傳播時間和功耗之間進行平衡。在大多數(shù)情況下,用戶無法控制這些∑-Δ轉(zhuǎn)換器的內(nèi)部濾波器系數(shù)值,不得不湊合了事。

LTC2378-20:市場上的首款20位SAR ADC

在對性能的角逐中,2014年,凌力爾特公司(現(xiàn)為ADI公司的一部分)向客戶推出了具有20位分辨率和真正線性度的第一款逐次逼近型ADC,將競爭對手打了個措手不及。LTC2378-20是一款出色的轉(zhuǎn)換器,在接近MSPS的所有其他競爭產(chǎn)品中仍然保持著自己的優(yōu)勢。

LTC2378曾經(jīng)的友敵,AD4020是ADI公司首款能以1.8MSPS速率數(shù)字化10V峰峰值差分信號的20位SAR ADC。它結合了低噪聲、低功耗以及LTC2378的所有特性:動態(tài)壓縮、鉗位電路、電荷轉(zhuǎn)移補償,支持使用低功耗精密放大器(高阻抗模式)等。采用1.8V電源供電,1.8MSPS速率下,功耗僅為15mW。350ns的轉(zhuǎn)換時間創(chuàng)下紀錄,使其在延長采集時間或讀取數(shù)據(jù)方面游刃有余。其采用10引腳MSOP或10引腳QFN封裝,與AD40xx家族的其他16位至18位成員相同。在–40°C至125°C溫度范圍內(nèi),其規(guī)格和運行完全有保證。

LTC2378-20和AD4020的采樣速率分別為1MSPS和1.8MSPS,為過采樣帶來了具有重要意義的可能性,特別是音頻頻段或更高頻段。為此,必須在外部FPGA或DSP中搭載定制型抽取濾波器。如前所述,可以繞過后者,以在必要時將其延遲降至最低。基于這些初級采樣速率值,考慮到0kHz至25kHz頻段,相應的過采樣因子約為16或32,處理增益為12dB至18dB,同時還嚴格按照奈奎斯特定理,簡化了常規(guī)操作條件下的抗混疊低通濾波器。

ADC至DSP鏈路:一切皆為串行

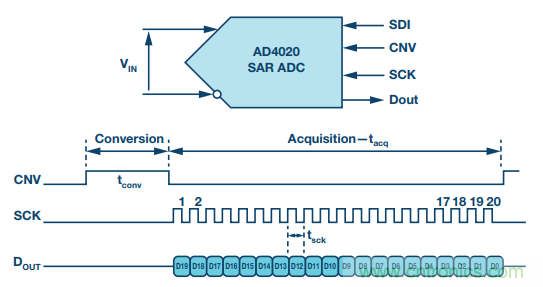

近年來,半導體行業(yè)及其設計師圈子明顯傾向于減小元件尺寸,使外殼引腳真正瘦身,并且還要調(diào)整需要與SPI總線、同步串口等連接的幾乎所有串行數(shù)字輸入或輸出。問題是,這些轉(zhuǎn)換器卻沒有留下用于抽取樣本和控制ADC的各功能選項的串行接口。根據(jù)其規(guī)格,這些串行接口兼容SPI或DSP串口,但實際并非如此。它們最多隱藏了負責設置時鐘信號節(jié)奏的移位寄存器,用于從器件中提取數(shù)據(jù),或者在配置期間注入數(shù)據(jù)。就如所有這些SAR ADC一樣,LTC2378-20和AD4020在頻率上要求串行時鐘(SCK)在額定采樣速率下,以20位為單位恢復數(shù)據(jù)。由于數(shù)據(jù)讀取階段嚴格限制在采集時間(約300ns)范圍以內(nèi),因此在轉(zhuǎn)換期間,必須將外部訪問時的數(shù)字活動減至完全靜音;并且要以1MSPS的采樣速率,在分配的時間內(nèi)從采樣恢復所有位,時鐘頻率必須達到60MHz以上。無論是產(chǎn)生這樣的時鐘頻率,還是要在接收器端實現(xiàn)的時間規(guī)格,對于負責從ADC收集數(shù)據(jù)的控制器上的接口來說,這都是嚴格的限制。

LTC2378-20要求最低SCK信號頻率達到64MHz,這意味著,它不能連接任何通用微控制器或搭載最高頻率略微超過50MHz的同步串口(SPORT)的DSP,Blackfin處理器?家族的一些成員除外,如ADSP-BF533、ADSP-BF561,其速率可以達到90Mbps。因此,有人擔心,需要使用搭載了低抖動時鐘產(chǎn)生電路相關的大型CPLD或FPGA。串行輸出SAR ADC的大多數(shù)數(shù)字接口或多或少具有相同的時序和邏輯信號模式,如圖4所示。對于SDI配置輸入,除了級聯(lián)模式之外,還對它提出了低得多的頻率要求。ADC采樣周期的等效全周期時間為

故定義最大采樣頻率,其構成為:

其本身由輸出數(shù)據(jù)的讀取速率調(diào)理,其中,

圖4.AD4020的時序圖

幸運的是,AD4020的轉(zhuǎn)換時間超短,為325ns,采樣速率為1MSPS,采樣時間為675ns,基于此,其串行數(shù)據(jù)讀取頻率低于33MHz,與DSP同步串口(如SHARC?ADSP-21479)相當,功耗也非常低。

一款超低功耗的多通道系統(tǒng)

出于能耗、精度和操作模式選擇靈活性的原因,同時也是出于商業(yè)考慮,在這些應用中不能考慮基于FPGA的解決方案。要處理來自這些20位ADC的串行輸出并實現(xiàn)最優(yōu)抽取濾波器,只能使用DSP浮點處理器。

如今,有許多數(shù)據(jù)采集系統(tǒng)都能通過大量信道同時采樣。這就導致許多ADC并行運行,同時由同一個控制器控制,該控制器還要負責收集數(shù)據(jù)并將其存儲在存儲器中以供后續(xù)分析。

運用SHARCADSP-21479或其快速版ADSP-21469和ADSP-21489(時鐘頻率為450MHz)等高性能SAR ADC構建的系統(tǒng)不但現(xiàn)實可行,而且在性能、開發(fā)時間、能耗和緊湊性等方面也是可圈可點。這些處理器具有支持8個模數(shù)數(shù)字化通道所需要的全部功能和外設,包括同步串行接口、不同時鐘信號的發(fā)生以及觸發(fā)轉(zhuǎn)換等。在所有SHARC處理器中,ADSP-21479是唯一一款采用低泄漏65納米CMOS工藝制造的32/40位浮點DSP,其優(yōu)勢是能大幅降低泄漏或靜態(tài)電流,并且其結溫幾乎呈指數(shù)級演進。作為處理器及其外設頻率和活動函數(shù)的動態(tài)電流也低于以標準或快速CMOS工藝制造的處理器。不足之處則在于,相比常規(guī)版本,其最大CPU頻率下降了約30%-40%,但仍然足以滿足此類應用的需求。

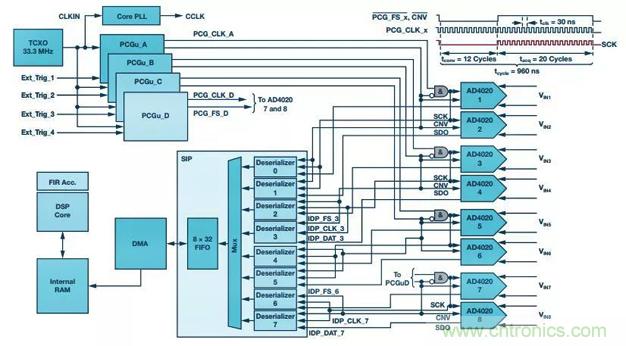

ADSP-21479搭載了多種外設,其中有一個特殊模塊被稱為串行輸入端口(SIP),該模塊能同時從同步運行的8個外部串口發(fā)射器接收信號流以及時鐘和同步信號。事實上,可以將與AD4020類似的8個ADC直接接入該接口,從而接入處理器。如圖5所示,8個通道有自己的IDP_SCK時鐘、IDP_FS同步和IDP_DAT輸入信號,一旦解串行,它們的數(shù)據(jù)會自動復用到32位、8字FIFO存儲器中,然后通過64位DMA數(shù)據(jù)包或CPU執(zhí)行的讀取操作,傳輸?shù)絊HARC內(nèi)部RAM。DMA傳輸操作中,SIP由運行于自動乒乓模式下的雙索引DMA通道伺服。此外,ADSP-21479還搭載有四個精密時鐘發(fā)生器(用于低抖動,縮寫為PCG),能夠從內(nèi)部或外部源(TCXO)生成獨立的時鐘和同步信號對。通過編程20位內(nèi)部分頻器可取得這些激勵的頻率、周期、脈沖寬度和相位。每個PCGx生成單元提供由一對AD4020轉(zhuǎn)換器共享的一對CLK/FS信號,但在轉(zhuǎn)換階段時鐘必須靜音,所以需要一個邏輯門,以便把IDP_FS信號和IDP_SCK信號結合起來形成SCK時鐘。

圖5.通過解串行將8個20位1MSPSSAR ADC接入SHARC DSP;DMA數(shù)據(jù)傳輸進DSP內(nèi)部RAM

圖5中的時序圖顯示,一旦轉(zhuǎn)換時間tconv已經(jīng)過去,必須盡可能快地以33.3MHz的速率,從當前樣本中讀取20位數(shù)據(jù),以在采樣頻率中維持1MSPS的神奇屏障。大約600ns后,數(shù)據(jù)被傳輸?shù)狡渲幸粋€SIP緩沖器中,此時可以使用IDP_FS或CNV信號啟動新的轉(zhuǎn)換周期,使AD4020進行新的轉(zhuǎn)換操作。使后者的最大轉(zhuǎn)換時間達到325ns,這對應于CNV信號的脈沖寬度,即12個IDP_SCK時鐘周期或360ns。總之,如圖5中的時序圖所示,一個完整的掃描周期需要32個IDP_SCK信號周期,總時間為960ns,因此其最大采樣速率為1.040MSPS。

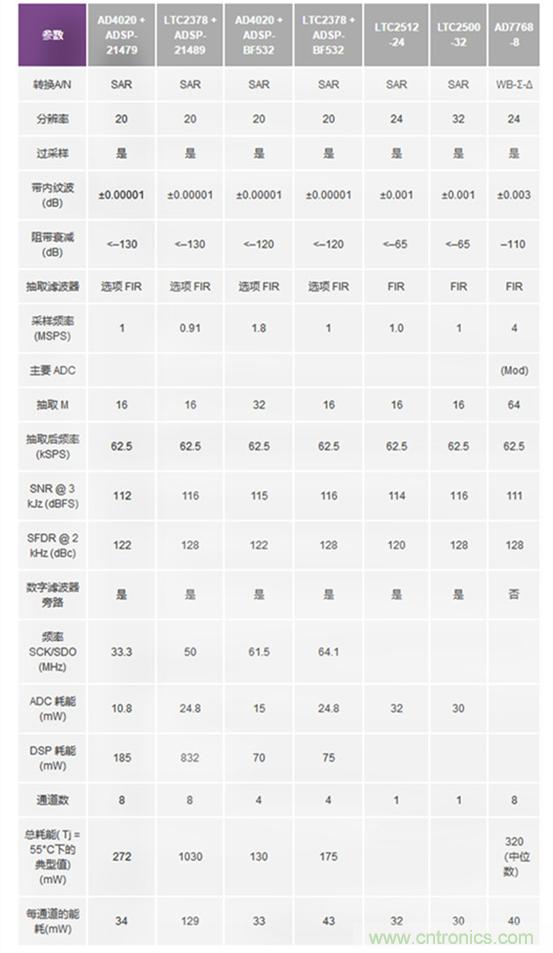

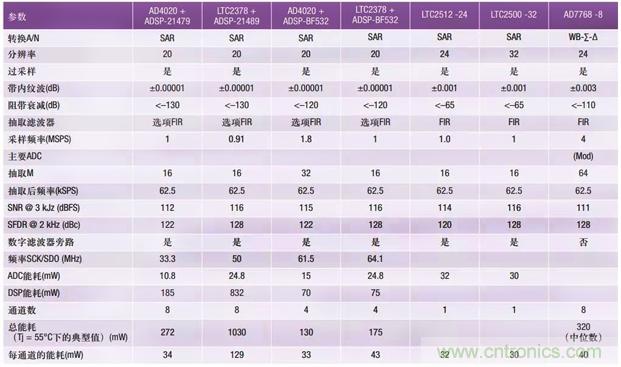

表1.不同SAR ADC與DSP相比的情況對比

同樣,ADCLTC2378-20可以與ADSP-21489相關聯(lián),因為它能夠在高達50MHz的外設時鐘頻率下工作,在這種情況下,采樣速率為900kSPS,如表1所示。遺憾的是,靜態(tài)電源電流(Iddint)或后者的泄漏電流遠高于動態(tài)電流,使得該配置的總功耗超過可用功率,達到不可接受的程度。

抽取濾波

假設將這些轉(zhuǎn)換器用于過采樣模式,如此,就有必要提供一個能滿足上述要求且針對目標頻帶定制的抽取濾波器,在所需計算能力和功耗方面盡量降低對DSP的影響。目前,用于改變采樣速率的程序已經(jīng)成為一種標準的數(shù)字信號處理操作,可以用內(nèi)插器和數(shù)字抽取器實現(xiàn)。出于相位響應線性度考慮,低通抽取濾波器采用有限脈沖響應(FIR)拓撲結構,可以根據(jù)效率要求采用不同的拓撲結構:

● 抽取專用直接或優(yōu)化FIR濾波器

● 級聯(lián)多速率FIR濾波器(1/2頻段)

● 多相FIR濾波器

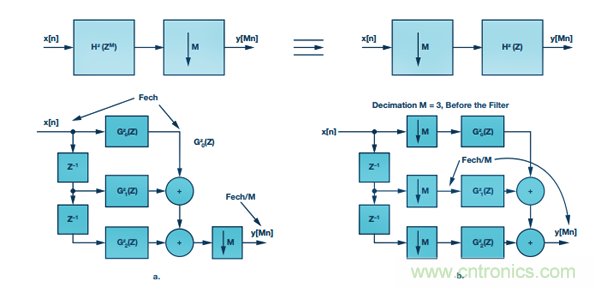

無論是FIR還是IIR類型的多相濾波器都是抽取或插值濾波器最有效的實現(xiàn)方案之一。然而,傳統(tǒng)數(shù)字處理方案要求在抽取之前進行濾波。在此假設下,1/M抽取濾波器由低通濾波器和緊隨其后的采樣頻率降級組成(圖6a)。預先對信號濾波,避免頻譜混疊,然后以M-1的速率定期消除樣本。然而,常規(guī)FIR或其他結構針對這些抽取濾波器的直接實現(xiàn)方案存在資源浪費問題,因為被拒樣本是幾十甚至幾百次累乘(MAC)的結果。使用分解成若干濾波器組的多相濾波器或是針對抽取進行優(yōu)化的濾波器,可以基于某些特點(如圖6b所示)形成高效的濾波器。

圖6a和6b.常規(guī)抽取濾波器和采用多相方案的抽取濾波器

憑借FIR濾波專用SIMD架構和硬件加速器,以及針對數(shù)字信號處理而優(yōu)化的指令集,SHARCADSP-21479特別適合實現(xiàn)這些類型的濾波器。每個SHARC處理單元都有一個32/40位乘法器累加器,能夠在266MHz的CPU頻率下,每秒實現(xiàn)533次定點或浮點MAC計算。然而,對于一些存在顯著延遲(房間均衡或音效)的應用,需要增加計算能力,使內(nèi)核從諸如FIR、IIR、FFT濾波等密集和持續(xù)乘法運算中解脫出來,用專門的硬件加速器去執(zhí)行這些運算。如此,用戶就能完全自主決定,將CPU用于計算需要執(zhí)行復雜搜集的復雜算法。FIR濾波專用加速器有專門的本地存儲器,用于存儲數(shù)據(jù)和系數(shù),并具有以下特征:

● 支持IEEE-754定點或浮點32位算術格式?

● 有四個并行運行的累乘單元?

● 支持單速率和多速率處理模式(抽取或插值)?

● 一次簡單迭代可以處理最多32個FIR濾波器,總共多達1024個系數(shù)

ADSP-21479的加速器的時鐘速率與系統(tǒng)時鐘或PCLK外設的速率相同,為CPUCCLK時鐘頻率的一半;即133MHz?;诖?,其總計算能力為533MAC/秒。加速器不要求執(zhí)行指令;其運算由特定寄存器的配置決定,并且完全依靠DMA傳輸在內(nèi)部和/或外部存儲器之間移動數(shù)據(jù)。

顯然,該加速器能以最優(yōu)方式執(zhí)行多速率濾波器的實現(xiàn)方案(插值或抽?。?。由于簡單的抽取濾波器僅為M個輸入信號提供一個輸出結果,因此,輸出速率比輸入速率低1/M倍。這種優(yōu)化型FIR濾波器的實現(xiàn)方案沒有采用復雜的多相濾波器組,因為后者需要大量的存儲器指針,實現(xiàn)起來非常復雜;相反,該方案只是把M-1個樣本的輸出擱置起來,避免執(zhí)行這些計算,并且只計算能產(chǎn)生有用樣本的數(shù)據(jù)。這就消除了浪費,結果,運算次數(shù)以M-1的比率減少——在本例中為15——從而大大地節(jié)省了CPU周期。然而,在這樣的抽取速率和如此短的計算窗口下,加速器不如有兩個計算單元的內(nèi)核有效,并且在信號從一個過濾器傳到另一個過濾器的過程中,其DMA通道因被重新編程會造成不利影響。如果在SISD模式下用一個計算單元實現(xiàn),則這類濾波器在CCLK周期數(shù)方面的成本可表示為:

N為濾波器的系數(shù)的個數(shù),M為抽取速率。

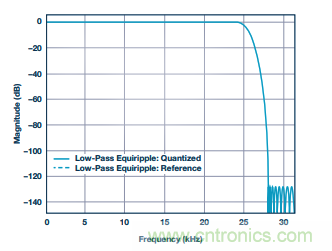

對于這種抽取濾波器一次迭代的實現(xiàn)成本,F(xiàn)IR濾波器條件下約為150個周期(源到匯編器21k),在0kHz至24kHz頻段,紋波規(guī)格為±0.00001dB,在62,500SPS采樣速率下,帶外衰減為-130dB。這款濾波器有97個系數(shù)(以32位FPIEEE-754格式量化),其響應如圖7所示,該圖是用MATLAB?FilterDesigner制成的。對于接入的SIP或ADC的每個活動通道,響應以該采樣頻率在DMA中斷實例中重復出現(xiàn)。

圖7.抽取濾波器的濾波器響應

對于實時和DSP負載,濾波操作以62.5kSPS的頻率重復,代表9,375,053個CCLK周期,而8個ADC轉(zhuǎn)換通道的重復頻率則略多于8倍,因為每個濾波器的存儲器指針值都存儲在SHARC數(shù)據(jù)地址生成器中,可以實現(xiàn)快速保存和恢復。這相當于,在SISD模式下,一個SHARCDSP為每秒8000萬個執(zhí)行周期(或80MIPS),在SIMD模式下,由于兩個處理單元并行運行,則為該值的一半。在前述兩種模式下,這8個抽取器FIR濾波器在執(zhí)行時,分別以30%和15%的速率以及266MHz的時鐘頻率占用ADSP-21479。

功耗

雖然轉(zhuǎn)換器的功耗可以從其規(guī)格中輕松、準確地推算出來,但處理器的功耗則要困難得多,因為處理器功耗的計算公式涉及多個參數(shù),并且實時條件和工作模式會對其造成極大的影響。這里雖然沒有詳細說明,但讀者可以在相關技術筆記中,輕松找到與ADSP-214xx和ADSP-21479處理器各組件功耗估算相關的說明,其中考慮了功能模塊的活動、靜態(tài)電流結溫、電源電壓值、使用的輸入輸出引腳數(shù)、各種外部頻率和容性負載。

依據(jù)圖5中的功能描述,針對DSP和ADC的若干組合,給出了與DSP在這類抽取濾波應用中活動情況相對應的功耗。對于這些搭載四個或八個ADC的相關DSP變體,需要根據(jù)功能容量、輸入/輸出的數(shù)量、處理器的計算能力以及ADC的整體性能確定其功耗。

憑借超低的靜態(tài)電流,以ADSP-21479及其八個SAR ADC集群為核心構建的解決方案不但是功耗最低的解決方案,同時提供豐富的濾波算法選擇和其他數(shù)字功能,在整體性能方面也是出類拔萃。

這個多通道數(shù)據(jù)采集系統(tǒng)(DAQ)的例子同時證明,實施數(shù)字信號處理任務不一定要使用FPGA,浮點DSP更適合高精度SAR ADC,尤其是在高度關注功耗的情況下。

表1. 不同SAR ADC與DSP相比的情況對比