【導讀】在當今競爭激烈的形勢下,使富含嵌入式軟件的復(fù)雜電子設(shè)備更快面市,但是同時確保其更便宜更可靠,是一種相當冒險的做法。未經(jīng)徹底測試的硬件設(shè)計不可避免地導致返工,增加設(shè)計成本并延長布局流程的網(wǎng)表交付時間,并最終延遲上市時間目標,對收益源造成破壞性影響。

推遲嵌入式軟件的測試也潛藏有錯過上市機遇的可能,會帶來更嚴重的后果。

正因為如此,項目周期的驗證部分極大地占用計劃時間變成了很常見的事情。其中的根本原因,在于跟蹤和消除錯誤極為不易,尤其是在片上系統(tǒng) (SoC) 的軟件內(nèi)容以每年約 200% 的速度增長的情況下。與此相反,設(shè)計的硬件部分僅增長約 50%。

硬件仿真作為系統(tǒng)驗證的基礎(chǔ)

雖然虛擬原型和現(xiàn)場可編程門陣列 (FPGA) 原型在早期嵌入式軟件測試上已受到關(guān)注,但對于軟件和硬件的集成并無助益。前者缺乏追蹤硬件錯誤所需的硬件精確性,而對于盡快消除錯誤所需的硬件調(diào)試,后者能力有限。

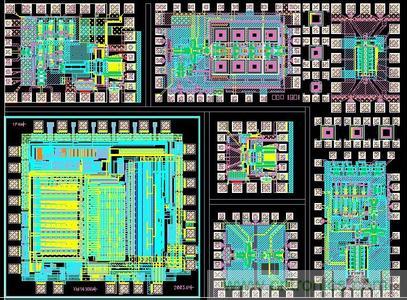

因此,開發(fā)團隊和項目經(jīng)理已轉(zhuǎn)而采用硬件仿真作為其驗證策略的基礎(chǔ)。硬件仿真是一種多功能驗證工具,有許多相關(guān)優(yōu)勢,包括軟硬件協(xié)同驗證或測試硬件和軟件集成的功能。它已受到軟件開發(fā)者的注意,因為這是能夠確保嵌入式系統(tǒng)軟件通過底層硬件正常工作的唯一驗證工具。對于致力于調(diào)試復(fù)雜 SoC 設(shè)計的硬件工程師來說,這也是值得注意的,因為工程師可以憑借該方法追蹤硬件內(nèi)的軟件錯誤或軟件行為中的硬件錯誤。硬件仿真的其他優(yōu)勢包括快速匯編功能、軟件驗證、全面的設(shè)計調(diào)試和可擴展性,可滿足包括數(shù)十億應(yīng)用程序特定集成電路 (ASIC) 門的設(shè)計。此外,它能夠以驗證嵌入式軟件和執(zhí)行系統(tǒng)驗證必需的高速率來處理數(shù)十億驗證周期(圖 1)。

過去,硬件調(diào)試和測試是項目周期驗證部分的唯一工作,此作業(yè)由硬件描述語言 (HDL) 測試平臺驅(qū)動的邏輯軟件仿真進行管理。傳統(tǒng)的大箱式硬件仿真只用于最大型的設(shè)計。很多開發(fā)團隊已采用正式驗證對軟件仿真進行補充,以增加基礎(chǔ)覆蓋范圍并確保不遺漏特殊用例。但是,只有硬件仿真可以在比較可行的時間內(nèi)完成 SoC 設(shè)計的全部驗證任務(wù),并緩解與基于事件的軟件仿真相關(guān)的運行問題。

都是軟件內(nèi)容的問題

SoC 的軟件內(nèi)容使協(xié)同驗證成為驗證策略中一個非常重要的部分,因為它可以在投片前確認一個嵌入式 SoC 的硬件和軟件部分同時得到驗證且正確交互。

過去,如果設(shè)計流片后發(fā)生硬件問題,軟件開發(fā)者必須盡其所能設(shè)法圍繞問題進行編碼。在 SoC 完成之前驗證軟件,設(shè)計團隊可以在進入硅片階段之前解決硬件問題。如前所述,硬件仿真檢查用于確保嵌入式軟件根據(jù)規(guī)范在硬件上運行。

過去使用各種調(diào)試引擎進行軟件調(diào)試。每種引擎有一個核心,充分利用硬件對處理器內(nèi)部工作的可視性和控制功能。雖然提供了部分調(diào)試功能,但由于處理器提供的接入方式,診斷問題的能力受限。此外,由于傳統(tǒng)軟件調(diào)試通常發(fā)生在實際系統(tǒng)中,軟件開發(fā)者以目標系統(tǒng)速度在實際硬件上執(zhí)行實際代碼。這樣他們可以通過大量代碼迅速找到錯誤的程序。

這些傳統(tǒng)技術(shù)在調(diào)試 SoC 時無效,因為沒有實際硬件,無法以真實系統(tǒng)速度執(zhí)行代碼。一般來說,只要執(zhí)行代碼且軟件模擬器提供所有硬件可視性,即可仿真硬件。但問題是速度 - 調(diào)試代碼是很慢的一種方法。

例如,如果 SoC 設(shè)計為在 Linux 上運行程序,軟件開發(fā)者必須以數(shù)十億時鐘周期完成 Linux 啟動,軟件才能開始執(zhí)行。粗略估計這會以約 10 赫茲 (Hz) 的典型軟件仿真速度花費 28 年以上完成 Linux 啟動。

不管調(diào)試硬件還是軟件,傳統(tǒng)硬件和軟件調(diào)試工具都無法得知彼此的任何情況。如果采用復(fù)雜的大型 SoC 設(shè)計,嘗試找到問題時獨立完成兩種調(diào)試是效率低下的。

兩者結(jié)合是最為理想的方法,這樣硬件仿真就可以節(jié)約時間。SoC 硬件通常在 FPGA 或其他可編程器件中實施,速度更快。在此設(shè)置中,根據(jù)運行速度,最快可以 15 分鐘的速度完成 Linux 啟動。硬件仿真可提供與硬件調(diào)試器相似的斷點和波形控制及可視性。

確認 SoC 設(shè)計按預(yù)期工作

硬件仿真以其高性能(這是軟件需求推動的越來越重要的需求)在一眾驗證工具中脫穎而出。它能夠確認 SoC 設(shè)計按計劃工作,并適于處理大到十億 ASIC 等效門的復(fù)雜設(shè)計,且每月可完成超過一萬億驗證周期。即使是這樣,現(xiàn)階段使用硬件仿真進行徹底詳盡的功能驗證仍然是可用的最具成本效益且有效的調(diào)試方法(圖 2)。

引入事務(wù)級建模 (TLM) 和事務(wù)處理器可用性可將硬件仿真轉(zhuǎn)為一系列垂直市場的虛擬平臺測試環(huán)境。事務(wù)處理器作為驗證知識產(chǎn)權(quán) (IP) 組合的一部分,是外設(shè)功能或協(xié)議的一種高級抽象模型。事務(wù)處理器通常作為現(xiàn)成 IP 提供,可用于各種不同的協(xié)議。典型的事務(wù)處理器通常包括 PCIe、USB、FireWire、Ethernet、Digital Video、RGB、HDMI、I2C、UART 和 JTAG 器件。

更好驗證更多的復(fù)雜系統(tǒng)

先前,硬件設(shè)計獨立于要在芯片上執(zhí)行的軟件的開發(fā)。但今非昔比,由于 SoC 處理器數(shù)量翻倍且每代產(chǎn)品包含兩倍的軟件內(nèi)容,軟件問題成為開發(fā)團隊和項目經(jīng)理優(yōu)先考慮的對象?,F(xiàn)在,開發(fā)團隊證實預(yù)期軟件在硬件平臺正常工作后,SoC 才算完整。

SoC 是一個全面的嵌入式系統(tǒng),需要進行硬件仿真來驗證其能否正常工作。通過硬件仿真,開發(fā)團隊可以更策略性地進行計劃,并根據(jù)多個抽象層面實施調(diào)試方法。他們可以同時在硬件和嵌入式軟件之間追蹤錯誤,確定問題所在。通過具有更高性價比且有效的方式,他們在這個過程中節(jié)約了時間,大幅降低錯過上市機遇的風險。