【導讀】隨著DSP處理器在現(xiàn)代工業(yè)的應用越來越廣泛,DSP的功能不僅只有快速運算處理,還需要與其他處理器或者設備之間進行實時數(shù)據(jù)交換,以實現(xiàn)資源的共享。因此,針對不同設備的需求,選擇穩(wěn)定、快速和高效率的接口方式在當今數(shù)字信號處理系統(tǒng)設計中關鍵的組成部分。

DSP的應用

針對8核DSP TMS320C6678與外部設備進行數(shù)據(jù)通信的需求,以片上集成千兆以太網(wǎng)交換子系統(tǒng)為核心,選取芯片88E1111作為PHY設備,設計了千兆以太網(wǎng)通信接口的硬件電路。在嵌入式操作系統(tǒng)SYS/BIOS和網(wǎng)絡開發(fā)環(huán)境NDK上,完成了以太網(wǎng)底層驅動和TCP/IP協(xié)議的程序設計。通過DSP與上位機進行以太網(wǎng)通信測試,證明了以太網(wǎng)接口電路硬件及軟件的正確性和實用性。

隨著DSP處理器在現(xiàn)代工業(yè)的應用越來越廣泛,DSP的功能不僅只有快速運算處理,還需要與其他處理器或者設備之間進行實時數(shù)據(jù)交換,以實現(xiàn)資源的共享。因此,針對不同設備的需求,選擇穩(wěn)定、快速和高效率的接口方式在當今數(shù)字信號處理系統(tǒng)設計中關鍵的組成部分。

TI公司的8核處理器TMS320C6678(以下簡稱C6678)提供豐富的片上接口資源用于處理器與外設之間的通信,這些接口都可以用于DSP與外設之間的通信,但是靈活性有差異,使用SGMII接口來實現(xiàn)千兆以太網(wǎng)通信,可使得通信接口一般化,能夠適用于眾多的設備連接。本文針對C6678的芯片特點以及含有的接口資源,設計實現(xiàn)了千兆以太網(wǎng)通信,主要設計了以太網(wǎng)接口電路、網(wǎng)絡底層硬件驅動、TCP/IP協(xié)議的用戶程序,并完成了與上位機以太網(wǎng)通信測試,實現(xiàn)了數(shù)字信號高速有效地網(wǎng)絡傳輸。

1.C6678以太網(wǎng)交換子系統(tǒng)

C6678是基于KeyStone I構架的8核高性能、定點/浮點處理器,單核最高工作頻率可達1.25 GHz。C6678的以太網(wǎng)交換子系統(tǒng)包括2個以太網(wǎng)媒體訪問控制(Ethernet Media Access Controller,EMAC)、2個SGMII、1個管理數(shù)據(jù)輸入輸出(Management Data Input Output,MDIO)、3-Port以太網(wǎng)交換模塊以及網(wǎng)絡配置總線,其網(wǎng)絡交換子系統(tǒng)如圖1所示。

EMAC的作用是將交換子系統(tǒng)的內(nèi)部信號轉換為GMII信號傳遞給SGMII模塊;MDIO控制物理層芯片執(zhí)行對多數(shù)據(jù)流的控制輸入輸出。

2.PHY芯片88E1111

本文選擇C6678作為主芯片,由于C6678的千兆網(wǎng)絡交換子系統(tǒng)只支持SGMII接口,所以本文選擇對SGMII接口的網(wǎng)絡數(shù)據(jù)傳輸具有較好兼容性的物理芯片88E1111。88E1111芯片的內(nèi)部結構如圖2所示。

88E1111的介質接口有銅介質接口和光纖接口。銅介質接口為MDI[3:0],通過設置HWCFG_MODE[3:0]來選擇運行模式。 88E1111集成的MDIO模塊與EMAC的MDIO接口相連接,可將方便網(wǎng)絡控制端讀取物理芯片狀態(tài)寄存器,達到實時監(jiān)測的效果。

3.硬件接口設計

本文設計的任務是基于C6678片內(nèi)以太網(wǎng)交換子系統(tǒng)和片外PHY芯片88E1111及其外圍電路的接口設計。主要包括:C6678與88E1111芯片連接、88E1111芯片配置以及88E1111芯片與網(wǎng)絡介質連接。

3.1 C6678與88E1111芯片連接

C6678和PHY芯片88E1111的接口電路如圖3所示。88E1111工作在SGMII接口模式下,不需要TXCLK時鐘輸入,更有助于減少電路板上走線的數(shù)量,同時也可減少噪聲的產(chǎn)生。

主要的接口信號包括時鐘和數(shù)據(jù)信號如下:

MDIO_CLK:管理數(shù)據(jù)時鐘。該時鐘信號由C6678片上的MDIO模塊提供,該時鐘頻率通過配置MDIO的控制寄存器CONTROL中的CLKDIV位來控制實現(xiàn)。

SGMII_TXP和SGMII_TXN:串行發(fā)送差分數(shù)據(jù)線。連接DSP內(nèi)部SerDes和物理芯片的S_IN管腳,DSP的SerDes通過該管腳向物理層發(fā)送串行數(shù)據(jù),數(shù)據(jù)中包含發(fā)送數(shù)據(jù)時鐘信號。

SGMII_RXP和SGMII_RXN:串行接收差分數(shù)據(jù)線。連接DSP內(nèi)部SerDes和物理芯片的S_OUT管腳,物理層芯片通過該接口將數(shù)據(jù)傳送到DSP的SerDes,數(shù)據(jù)中包含數(shù)據(jù)接收時鐘信號。

MDIO:管理數(shù)據(jù)I/O??勺疃噙B接32個PHY設備到DSP的EMAC,并且可以枚舉所有PHY設備,讀取PHY設備狀態(tài)寄存器來監(jiān)測PHY的連接狀態(tài)。數(shù)據(jù)幀結構符合802.3標準,包含讀寫指令、PHY地址、寄存器地址和數(shù)據(jù)等。

因為88E1111上集成的MDIO與C6678集成MDIO模塊進行連接時,電壓有所差別,前者電壓為2.5 V,后者電壓為1.8 V,所以在二者之間應該添加電壓轉換器。本文采用一片PCA9306,實現(xiàn)2.5 V和1.8 V之間的電平轉換,其連接電路如圖4所示。

3.2 88E1111芯片配置

88E1111與C6678的MDIO模塊相連接,MDIO最多可識別32個物理芯片,在使用物理芯片之前需要對其進行配置,配置內(nèi)容主要包括芯片的地址、模式等。配置CONFTG[6:0]管腳定義可查詢文獻,本文配置的硬件電路如圖5所示,圖5中可以不使用電阻,本文為了測試方便,加一個0 Ω的電阻。

88E1111硬件配置完成后,系統(tǒng)將固定為一種接口方式,按照文獻的定義,物理芯片的地址為:PHY_ADDRESS=0’b00001,芯片模式為:不帶時鐘,自動協(xié)商的SGMII模式。

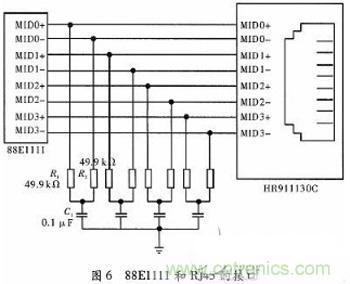

3.3 88E1111芯片與RJ45連接

88E1111和網(wǎng)絡介質之間無法直接連接,因傳輸速度在千兆級,所以更加需要設計合適的網(wǎng)絡隔離變壓器來降低傳輸損耗、回音和串擾。本文選擇千兆網(wǎng)口插座HR911130C,該插座內(nèi)部自帶變壓器電路,只需在外部連接濾波網(wǎng)絡便可實現(xiàn)網(wǎng)絡信號穩(wěn)定地傳輸,如圖6所示。88E1111和 HR9111130C采用差分連接,在PCB布線時需要嚴格等長,且一般還需使用阻抗匹配網(wǎng)絡,如圖6中的R1和C1。

4.軟件程序設計

TI針對網(wǎng)絡開發(fā)發(fā)布了網(wǎng)絡開發(fā)套件(Network Development Kit,NDK),能將多個模塊的配置操作交給NDK網(wǎng)絡框架實現(xiàn),同時數(shù)據(jù)分包和解析也無需程序員過多考慮,加速了網(wǎng)絡開發(fā)進程。NDK構建在實時操作系統(tǒng)SYS/BIOS之上,NDK通過OS抽象層與BIOS進行交互,同時BIOS的cfg配置文件能對NDK各模塊進行可視化查看。

本文基于多核DSP實時操作系統(tǒng)SYS/BIOS上,設計了以太網(wǎng)通信程序。該操作系統(tǒng)能夠提供較多的集成模塊,方便用戶編寫程序,且還有軟硬件中斷管理、多任務同步機制、多核通信機制和存儲器管理機制等,可為用戶進行多線程多任務開發(fā)提供模塊化的框架。以太網(wǎng)通信接口的軟件總體結構如圖7所示。

SYS/BIOS為整個軟件提供集成開發(fā)環(huán)境,不僅擁有適合實時系統(tǒng)的多線程優(yōu)先搶占機制,還可添加需要的封裝庫,使得編寫程序時可以更加方便地調(diào)用庫函數(shù)。NDK是DSP的網(wǎng)絡程序開發(fā)集成工具,其中,stack.lib給出了從頂層socket到底層PPP關于TCP/IP協(xié)議棧的封裝庫;nettool.lib提供用于socket網(wǎng)絡套接字和用于網(wǎng)絡應用開發(fā)工具的封裝庫;os.lib提供應用于SYS/BIOS和網(wǎng)絡編程套件之間的系統(tǒng)協(xié)調(diào)的封裝庫;hal.lib提供外圍設備和網(wǎng)協(xié)議棧之間接口的封裝庫;netctrl.lib提供DSP網(wǎng)絡編程的整體控制,可用來配置底層驅動和協(xié)議。

本文DSP片上系統(tǒng)軟件分為3部分:SYS/BIOS平臺和NDK的TCP/IP協(xié)議棧建立和配置;用戶程序;編制底層驅動程序。

4.1 底層硬件驅動的實現(xiàn)

NDK的基本結構如圖7所示,可看出NDK開發(fā)套件與用戶程序、SYS/BIOS操作系統(tǒng)和底層硬件都有密切的聯(lián)系。NDK中網(wǎng)絡控制層和操作系統(tǒng)接口層與SYS/BIOS系統(tǒng)相連接,NDK的硬件驅動層用于控制底層硬件驅動的配置,這些操作和配置均可在網(wǎng)絡工具庫中找到相應的驅動函數(shù),并可直接由用戶應用程序來調(diào)用實現(xiàn)。

這些功能主要包括:

(1)底層硬件驅動包括:MDIO模塊和EMAC模塊的初始化;PHY芯片搜索配置和狀態(tài)監(jiān)測;EMAC/MDIO中斷使能。(2)TCP/IP協(xié)議棧的建立,配置接收和發(fā)送緩存區(qū)的大小,完成以太網(wǎng)數(shù)據(jù)的收發(fā)任務。(3)利用MDIO模塊,根據(jù)MDIO讀取的PHY狀態(tài)寄存器來監(jiān)測其連接狀態(tài),識別可以是CPU產(chǎn)生中斷的狀態(tài)變化事件,并將信息反饋。(4)關閉驅動,復位前面對寄存器進行的操作,收回占用資源。

如圖7所示,硬件驅動包含在硬件驅動層hal.lib中,用戶需要對按照系統(tǒng)對驅動函數(shù)進行修改。C6000系列NDK的API封裝了許多固定的驅動函數(shù),具有特定的功能,比如_llPacketSerivceCheck()的作用是檢測以太網(wǎng)數(shù)據(jù)包的結構,且將檢測到的結構信息反饋給協(xié)議棧進行分析處理。具體的驅動程序需要按照硬件系統(tǒng)的配置來進行設計,在C6678中,可在集成度較高的片上系統(tǒng)直接對網(wǎng)絡通信模塊的寄存器進行配置查詢,就可以完成硬件底層驅動,使得底層硬件能夠有效地運行。

4.2 DSP端網(wǎng)絡應用程序

DSP軟件設計是基于SYS/BIOS實時多任務操作系統(tǒng)和C語言,采用Socket套接字,創(chuàng)建TCP/IP客戶端(Client)和服務器端 (Server),Client負責與外部設備服務器端建立連接并接收數(shù)據(jù)包,Server用來向PC機發(fā)送處理后的數(shù)據(jù)包。接收任務和發(fā)送任務流程如圖 8所示。在C6678的內(nèi)核Core0中建立兩個同步線程任務,即數(shù)據(jù)接收和發(fā)送任務,分別用來接收TCP服務器發(fā)送過來的數(shù)據(jù)和發(fā)送處理后的數(shù)據(jù)到PC 上位機中進行處理、存儲和顯示。

4.3 上位機測試程序

上位機測試程基于VC++的MFC界面設計,使用套接字Socket進行網(wǎng)絡編程。程序中需設計兩個同步線程,用來實現(xiàn)數(shù)據(jù)的實時接收和動態(tài)顯示功能。使用TCP服務器端發(fā)送船體結構應力數(shù)據(jù),經(jīng)過DSP的接接收、處理和發(fā)送過程,最后發(fā)送到PC上位機進行數(shù)據(jù)動態(tài)顯示,結果如圖9所示。

5.結論

本文以8核處理器C6678為核心,對片上集成的以太網(wǎng)交換子系統(tǒng)接口硬件進行了研究,按照接口的特點設計了包括以太網(wǎng)交換子系統(tǒng)和物理芯片的接口連接、物理芯片與網(wǎng)絡介質接口連接的硬件系統(tǒng),并完成了千兆以太網(wǎng)驅動,最終實現(xiàn)多核DSP C6678與上位機進行千兆以太網(wǎng)通信。通過與上位機進行網(wǎng)絡通信測試,結果顯示以太網(wǎng)數(shù)據(jù)通信接口能實時高效地進行網(wǎng)絡數(shù)據(jù)傳輸。