【導讀】逐次逼近型模數轉換器(ADC)廣泛運用于要求最高18位分辨率和最高5 MSPS速率的應用中。主機處理器可以通過多種串行和并行接口(如SPI、I2C和LVDS)訪問或控制ADC。本文將討論打造可靠、完整數字接口的設計技術,包括數字電源電平和序列、啟動期間的I/O狀態(tài)、接口時序、信號質量以及數字活動導致的誤差。

數字I/O電源電平和序列

多數SAR ADC都提供獨立的數字I/O電源輸入(VIO或VDRIVE),后者決定接口的工作電壓和邏輯兼容性。此引腳應與主機接口(MCU、DSP或FPGA)電源具有相同的電壓。數字輸入一般應在DGND-0.3 V與VIO + 0.3 V之間,以避免違反絕對最大額定值。須在VIO引腳與DGND之間連接走線短的去耦電容。

采用多個電源的ADC可能擁有明確的上電序列。應用筆記AN-932《電源序列》為這些ADC電源的設計提供了良好的參考。為了避免正向偏置ESD二極管,避免數字內核加電時處于未知狀態(tài),要在接口電路前打開I/O電源。模擬電源通常在I/O電源之前加電,但并非所有ADC均是如此。請參閱并遵循數據手冊中的內容,確保序列正確。

啟動期間的數字I/O狀態(tài)

為了確保初始化正確無誤,有些SAR ADC要求處于某些邏輯狀態(tài)或序列,以實現復位、待機或關斷等數字功能。在所有電源都穩(wěn)定之后,應施加指定脈沖或組合,以確保ADC啟動時的狀態(tài)符合預期。例如,一個高脈沖在RESET上持續(xù)至少50 ns,這是配置AD7606以使其在上電后能正常運行所必須具備的條件。

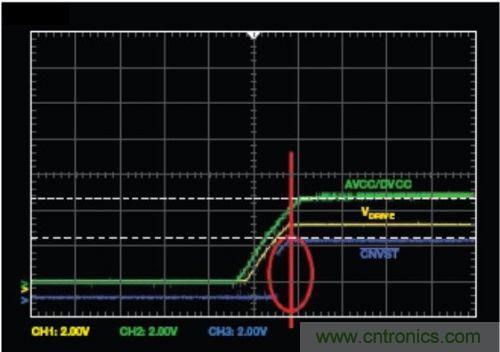

在所有電源均完全建立之前,不得切換數字引腳。對于SAR ADC,轉換開始引腳CNVST可能對噪聲敏感。在圖1所示示例中,當AVCC、DVCC和VDRIVE仍在上升時,主機cPLD拉高CNVST。這可能使AD7367進入未知狀態(tài),因此,在電源完全建立之前,主機應使CNVST保持低電平。

圖1. 在電源上升時拉高CNVST可能導致未知狀態(tài)

數字接口時序

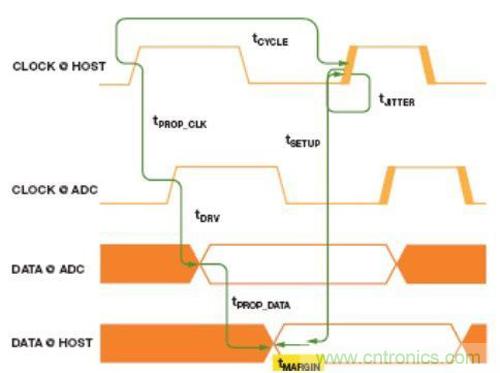

轉換完成之后,主機可以通過串行或并行接口讀取數據。為了正確讀取數據,須遵循特定的時序策略,比如,SPI總線需要采用哪種模式等。不得違反數字接口時序規(guī)范,尤其是ADC和主機的建立和保持時間。最大比特率取決于整個循環(huán),而不僅僅是最小額定時鐘周期。圖2和下列等式展示了如何計算建立和保持時間裕量。主機把時鐘發(fā)送至ADC并讀取ADC輸出的數據。

圖2. 建立和保持時序裕量

tCYCLE: 時鐘周期

tJITTER: 時鐘抖動

tSETUP: 主機建立時間

tHOLD: 主機保持時間

tPROP_DATA: 從ADC到主機的傳輸線路的數據傳播延遲

tPROP_CLK: 從主機到ADC的傳輸線路的數據傳播延遲

tDRV: 時鐘上升/下降沿后的數據輸出有效時間

tMARGIN: 裕量時間大于等于0表示達到建立時間或保持時間要求,小于0表示未達到建立時間或保持時間要求。

主機建立時間裕量

tMARGIN_SETUP = tCYCLE, MIN – tJITTER – tSETUP – tPROP_DATA – tPROP_CLK –

建立時間等式以最大系統延遲項定義最小時鐘周期時間或最大頻率。要達到時序規(guī)格,必須大于等于0。提高周期(降低時鐘頻率)以解決系統延遲過大問題。對于緩沖器、電平轉換器、隔離器或總線上的其他額外元件,把額外延遲加入tPROP_CLK和tPROP_DATA。

類似地,主機的保持時間裕量為

tMARGIN_HOLD = tPROP_DATA + tPROP_CLK + tDRV – tJITTER –

保持時間等式規(guī)定了最小系統延遲要求,以避免因違反保持時間要求而出現邏輯錯誤。要達到時序規(guī)格,必須大于等于0。

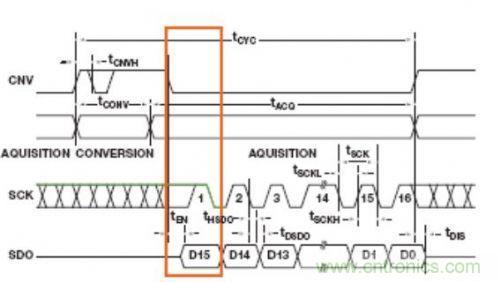

公司帶SPI接口的許多SAR ADC都是從CS或CNV的下降沿為MSB提供時鐘信號,剩余的數據位則跟隨SCLK的下降沿,如圖3所示。在讀取MSB數據時,要使用等式中的tEN而非tDRV。

圖3. AD7980 3線CS模式下的SPI時序

因此,除了最大時鐘速率以外,數字接口的最大工作速率也取決于建立時間、保持時間、數據輸出有效時間、傳播延遲和時鐘抖動。

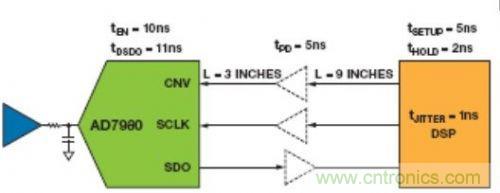

在圖4中,DSP主機訪問AD7980處于3線CS模式下,其中,VIO = 3.3 V。DSP鎖存SCLK下降沿上的SDO信號。DSP的額定最小建立時間為5 ns,最小保持時間為2 ns。對于典型的FR-4PCB板,傳播延遲約為180 ps/in。緩沖器的傳播延遲為5 ns。CNV、SCLK和SDO的總傳播延遲為

tPROP = 180 ps/in × (9 in + 3 in) + 5 ns = 7 ns

tJITTER = 1 ns。主機SCLK的工作頻率為30 MHz,因此,tCYCLE= 33 ns

tSETUP_MARGIN= 33 ns –1 ns – 5 ns – 7 ns – 11 ns – 7 ns = 2 ns

tHOLD_MARGIN= 11 ns + 7 ns + 7 ns – 1 ns – 2 ns = 22 ns

建立時間和保持時間裕量均為正,因此,SPI SCLK可以在30 MHz下工作。

圖4. DSP和AD7980之間的數字接口

數字信號質量

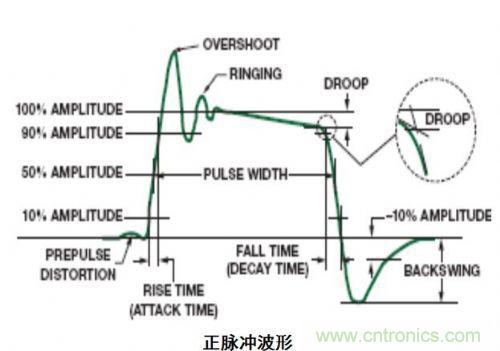

數字信號完整性(包括時序和信號質量)確保:在額定電壓下接收信號;不相互干擾;不損壞其他器件;不污染電磁頻譜。信號質量由多個項定義,如圖5所示。本部分將介紹過沖、振鈴、反射和串擾。

圖5. 常用信號質量規(guī)格

反射是阻抗不匹配導致的結果。當信號沿著走線傳播時,每個接口處的瞬時阻抗都不相同。部分信號會反射回去,部分信號會繼續(xù)沿著線路傳播。反射可能在接收器端產生過沖、欠沖、振鈴和非單調性時鐘邊沿。

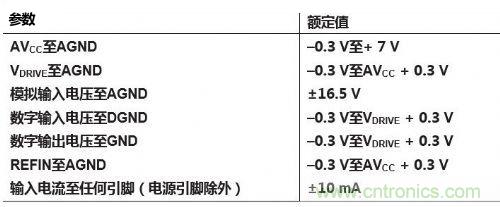

過沖和欠沖可能損壞輸入保護電路,或者縮短IC的使用壽命。圖6所示為AD7606的絕對最大額定值。數字輸入電壓應在–0.3 V和VDRIVE + 0.3 V之間。另外,如果振鈴高于最大VIL或小于最小VIH可能導致邏輯誤差。

絕對最大額定值

除非另有說明,TA = 25℃

圖6. AD7606的絕對最大額定值

為了減少反射:

盡量縮短走線的長度

控制走線的特性阻抗

消除分支

使用適當的端接方案

用環(huán)路面積小的固體金屬作為返回電流參考平面

使用較低的驅動電流和壓擺率

針對走線特性阻抗的計算,目前有許多軟件工具或網站,比如Polar Instruments Si9000 PCB傳輸線路場求解器。借助這些工具,特性阻抗計算起來非常簡單,只需選擇傳輸線路型號并設置相應的參數即可,比如電介質類型和厚度以及走線寬度、厚度和隔離。

作為一種新興標準,IBIS用于描述IC數字I/O的模擬行為。ADI提供針對SAR ADC的IBIS模型。預布局仿真可檢測時鐘分布、芯片封裝類型、電路板堆疊、網絡拓撲結構和端接策略。也可檢測串行接口時序限制以便為定位和布局提供指導。后仿真可驗證設計是否符合所有指導方針和限制的要求,同時檢測是否存在反射、振鈴、串擾等違反要求的情況。

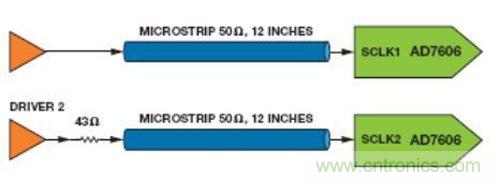

在圖7中,一個驅動器通過一條12英寸的微帶線路連接SCLK1,另一個驅動器通過一個與微帶串聯的43Ω電阻連接SCLK2。

圖7. 驅動

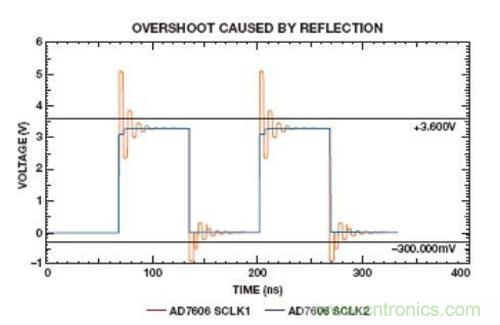

在圖8中,SCLK1上的大過沖違反了–0.3 V至+3.6 V的絕對最大額定值。串聯電阻可減小SCLK2上的壓擺率,使信號處于額定值之內。

圖8. AD7606 IBIS過沖模型仿真

串擾是能量通過互電容(電場)或互感(磁場)在并行傳輸線路間耦合的情況。串擾量取決于信號的上升時間、并行線路的長度以及它們之間的間距。

控制串擾的一些常用方法為:

增加線路間距

減小并行布線

使走線靠近參考金屬平面

使用適當的端接方案

減小信號壓擺率

數字活動導致的性能下降

數字活動可能導致SAR ADC性能下降,使SNR因數字地或電源噪聲、采樣時鐘抖動和數字信號干擾而減小。

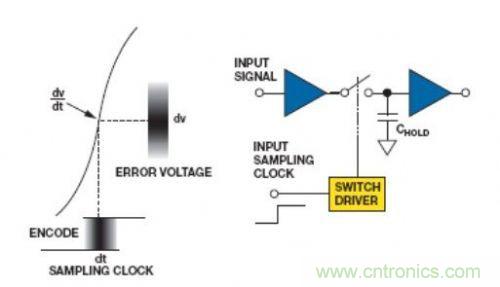

孔徑或采樣時鐘抖動設定SNR限值,尤其是對高頻輸入信號。系統抖動有兩個來源: 來自片內采樣保持電路的孔徑抖動(內部抖動),以及采樣時鐘上的抖動(外部抖動)??讖蕉秳訛檗D換間的采樣時間變化,為ADC的函數。采樣時鐘抖動通常為主要誤差源,但兩個源都會導致模擬輸入采樣時間變化,如圖9所示。它們的影響難以區(qū)分。

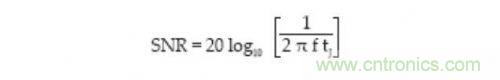

總抖動會產生誤差電壓,ADC總SNR的限制因素為

總抖動 = tJ (rms)

總抖動 = √(ADC孔徑抖動)2+(采樣時鐘抖動)2

其中,f為模擬輸入頻率,tJ為總時鐘抖動。

圖9. 采樣時鐘抖動導致的誤差電壓

數字輸出開關導致的電源噪聲應與敏感的模擬電源相隔離。分別去耦模擬和數字電源,密切注意地回流路徑。

高精度SAR ADC可能對數字接口上的活動很敏感,即使電源適當去耦和隔離時。突發(fā)時鐘往往優(yōu)于連續(xù)時鐘。數據手冊通常會列出接口不應活動的安靜時間。在較高吞吐速率條件下,可能難以減少這些時間內的數字活動,通常為采樣時刻及出現關鍵位判斷點時。

結論

密切注意數字活動,確保SAR ADC轉換有效。數字活動導致的誤差可能使SAR ADC進入未知狀態(tài),導致故障,或者降低性能。希望本文能幫助設計師排查根本原因,同時還能提供解決方案。