【導讀】當由于程序運行出錯或操作錯誤使系統(tǒng)處于死鎖狀態(tài)時,為擺脫困境,也需按復位鍵以重新啟動。所以系統(tǒng)的復位電路必須準確、可靠地工作。本文就講解的是多間隔脈沖信號連接器電路,教你快速準確的設計連接器電路!

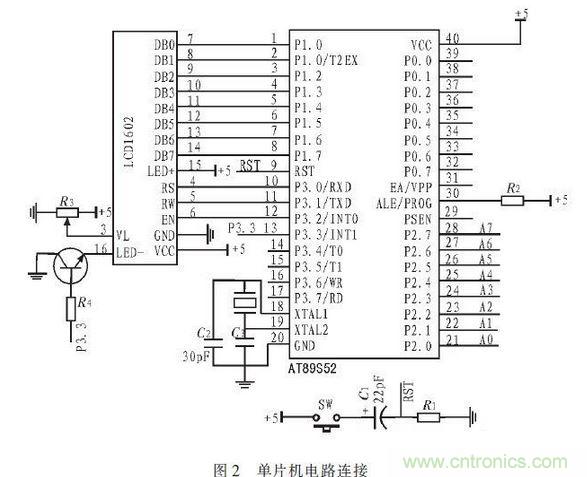

單片機應用系統(tǒng)工作時,除了進入系統(tǒng)正常的初始化之外,當由于程序運行出錯或操作錯誤使系統(tǒng)處于死鎖狀態(tài)時,為擺脫困境,也需按復位鍵以重新啟動。所以系統(tǒng)的復位電路必須準確、可靠地工作。單片機的復位都是靠外部電路實現(xiàn)的,在時鐘電路工作后,只要在單片機的RST引腳上出現(xiàn)24個時鐘振蕩脈沖(即2個機器周期)以上的高電平,單片機便實現(xiàn)初始化狀態(tài)復位。為了保證應用系統(tǒng)可靠地復位,系統(tǒng)采用按鍵電平復位方式。

單片機AT89S52的P1口與液晶顯示模塊LCD1602的數(shù)據(jù)端口相連,P3.2控制液晶模塊的讀寫;對比度調整端連接一個10 kΩ的可調電阻,用來調整液晶顯示亮度。另外,單片機的P2口與CPLD的8個I/O口相連,以進行數(shù)據(jù)傳輸,其電路設計如圖2所示。

CPLD電路設計

晶振是為處理器提供頻率基準的元器件,屬于系統(tǒng)不可或缺的一部分。通常分為有源晶振和無源晶振兩個大類,無源晶振要求芯片內部有震蕩器,并且其信號電壓根據(jù)起振電路而定,允許不同的電壓,但無源晶振通常信號質量和精度較差,需要精確的匹配外圍電路,如需更換晶振要同時更換外圍電路。有源晶振不需要芯片的內部振蕩器,可以提供高精度的頻率基準,信號質量也較無源晶振要好。

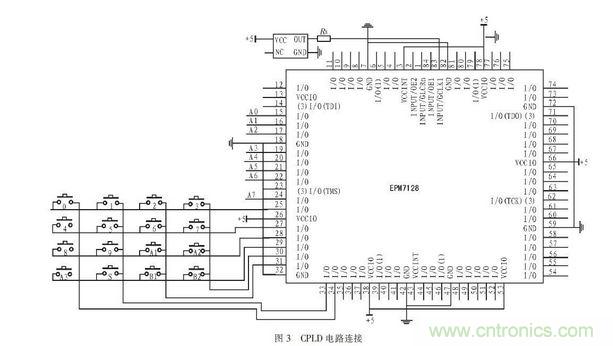

EPM7128SLC84需要提供外部時鐘信號,由于CPLD對時鐘精度要求甚高,通過前面的分析可知有源晶振的通信質量和精度較無源晶振高,所以采用1.000 MHz的有源晶體振蕩器,電路的輸出端口與處理器EPM7128SLC84的GCKL1連接,其具體電路設計如圖3所示。