【導讀】安森美半導體(ON Semiconductor)為滿足市場對更高時鐘精度的需求,不斷開發(fā)和拓展完整時鐘解決方案,降低時間抖動和相位噪聲,同時使系統(tǒng)設(shè)計更加簡單易行。

網(wǎng)絡(luò)/無線/云計算、數(shù)字消費、自動測試設(shè)備(ATE)/工業(yè)等應(yīng)用市場的不斷發(fā)展令時鐘技術(shù)在性能和靈活性的結(jié)合越趨重要,而且越來越多的應(yīng)用要求實時時鐘在寬溫度范圍內(nèi)有極高的計時精度。安森美半導體(ON Semiconductor)為滿足市場對更高時鐘精度的需求,不斷開發(fā)和拓展完整時鐘解決方案,降低時間抖動和相位噪聲,同時使系統(tǒng)設(shè)計更加簡單易行。

不同應(yīng)用市場對時鐘方案的需求

不同應(yīng)用市場對時鐘方案的需求各有特點。例如,網(wǎng)絡(luò)、無線和云計算領(lǐng)域需要低于1ps的抖動及低相位噪聲,采用晶體振蕩器(XO)或壓控晶體振蕩器(VCXO),并且在網(wǎng)絡(luò)/無線基站時鐘中集成更高的靈活性及更多的功能。數(shù)字消費領(lǐng)域則需要具有專用時鐘合成、壓控晶體振蕩器、可編程能力(系統(tǒng)設(shè)計靈活性)、多PLL可配置頻率、擴頻有源降低電磁干擾(EMI),以及快速提供樣品和上市,還需要降低成本。ATE和工業(yè)領(lǐng)域需要高速精密時鐘及數(shù)據(jù)管理器件。

PCIe接口的應(yīng)用優(yōu)勢及行業(yè)普及趨勢

作為一種重要的總線接口技術(shù),外圍組件快速互連(PCIe)具有很多優(yōu)勢,如在帶寬、模塊化及多內(nèi)核器件方面提供更高性能,采用標準獨特連接時可以優(yōu)化成本及可靠性等。在PCIe應(yīng)用漸趨普及的今天,越來越多的存儲設(shè)備已經(jīng)開始從SATA接口轉(zhuǎn)向PCIe,固態(tài)硬盤(SSD)存儲器也開始轉(zhuǎn)向PCIe;NEC家庭網(wǎng)關(guān)(HGW)自2010年開始使用PCIe;某些機頂盒芯片組(消費類)參考設(shè)計在2010年加入PCIe接口;不同架構(gòu)的數(shù)據(jù)中心在大幅增加高速PCIe的使用方面發(fā)揮了關(guān)鍵作用。我們看到,PCIe在PC/圖形/工作站、服務(wù)器和存儲、數(shù)據(jù)通信、嵌入式/企業(yè)、消費、SSD存儲等行業(yè)日漸普及。

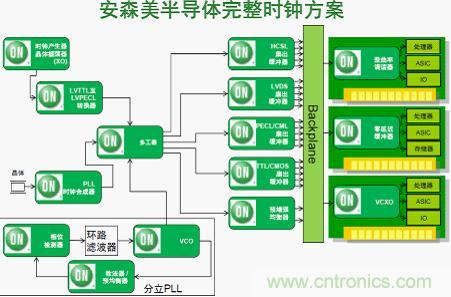

圖1:安森美半導體完整時鐘方案

正是為了配合時鐘市場及時鐘生成技術(shù)的應(yīng)用趨勢,安森美半導體憑借先進的半導體工藝和模擬技術(shù)專長,提供完整的時鐘方案(圖1)。這些產(chǎn)品可以在系統(tǒng)中提供猶如心臟有規(guī)律跳動的準確頻率,在實現(xiàn)更高性能的同時簡化系統(tǒng)復雜度,實現(xiàn)精確的系統(tǒng)同步。

安森美半導體用于服務(wù)器系統(tǒng)的PCIe時序產(chǎn)品和方案

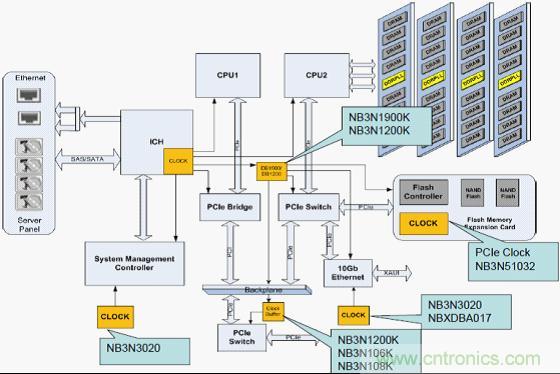

以服務(wù)器技術(shù)的變遷為例,首先可以看到其三個變化方向:關(guān)鍵任務(wù)/數(shù)據(jù)分析(大數(shù)據(jù))、企業(yè)和超大規(guī)模。其次,企業(yè)服務(wù)器市場將繼續(xù)繁榮發(fā)展,用于低交易量、高計算工作負荷的服務(wù)器市場不斷擴大,并逐步采用內(nèi)部部署(On-premise) 、云計算、虛擬化、數(shù)據(jù)庫等。第三,網(wǎng)絡(luò)級數(shù)據(jù)中心演進帶來了新商機,高交易量、低計算工作負荷不斷增加;Web 2.0數(shù)據(jù)中心、視頻傳送、用戶鑒別持續(xù)得到采用。安森美半導體用于服務(wù)器系統(tǒng)的時序產(chǎn)品如圖2所示。

圖2:安森美半導體用于服務(wù)器系統(tǒng)的時序產(chǎn)品

安森美半導體PCIe時鐘方案具有一些共同特性和優(yōu)勢,包括帶單路、雙路及四路輸出的PCIe時鐘合成器;帶1:6、1:8、1:10及1:21扇出的PCIe緩沖器;提供用于1、2、6、8、10及21通道應(yīng)用的方案;具有超低歪曲率(skew) ;傳播延遲變化?。ǘ噙_21路輸出);抖動符合PCIe第1代、第2代及第3代規(guī)范;直接器件接口省去外部端子元件,減少物料單(BOM) 。

1)NB3N3002

NB3N3002是一款3.3 V晶體至單高速電流驅(qū)動邏輯(HCSL) 合成器,特性包括:頻率25 MHz、100 MHz、125 MHz和200 MHz;HCSL差分輸出;支持PCI-Express和以太網(wǎng)需求;使用25MHz基本并聯(lián)諧振晶體;3.3 V電源;無需外部環(huán)路濾波器;引腳兼容無擴頻ICS557-01、5V41064、5V41234。此外還有NB3N5573 3.3 V晶體至雙高速電流驅(qū)動邏輯 (HCSL)合成器。圖3是NB3N3002的簡化框圖。

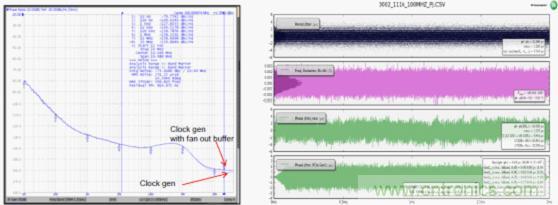

圖3:NB3N3002以100 MHz驅(qū)動NB3N106K/108K/111K扇出緩沖器符合PCIe 1,2,3抖動及相位噪聲規(guī)范。

[page]

2)NB3N51034、NB3N51044和NB3N51054

這些都是新推出的產(chǎn)品,特性包括:采用25 MHz基本模式并聯(lián)諧振晶體;掉電模式;不需要外部環(huán)路濾波器;四個低歪曲率HCSL輸出;OE三態(tài)輸出;擴頻選擇為-0.5%、-1.0%、-1.5%和無擴頻;PCI Express Gen 1、2、3抖動要求;引腳兼容IDT557-05、5V41236、5V40166。

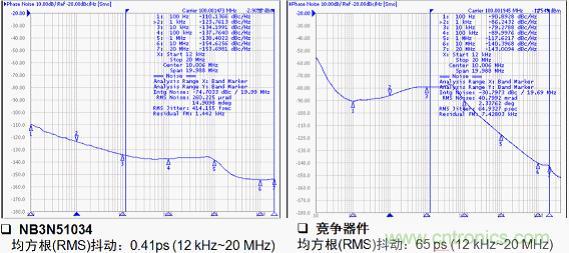

在100MHz條件下,NB3N51034與競爭對手(PCIe Gen3) 相比,其均方根(RMS)抖動僅為0.41ps (12 kHz~20 MHz),而競爭對手為65 ps (12 kHz~20 MHz),見圖4。

圖4:安森美半導體NB3N51034均方根抖動性能明顯優(yōu)于競爭器件

另一款是NB3N51044 3.3 V四輸出HCSL/LVDS合成器,帶單獨輸出啟用 (OE),增加了LVCMOS/LVTTL輸入,支持四個100 MHz (PCIe)或125 MHz (sRIO) HCSL輸出;FSEL引腳可在100 MHz/125 MHz之間切換;PLL旁路模式;每個輸出三態(tài)輸出單獨OE;引腳兼容IDT841604A。

還有一款新產(chǎn)品是NB3N51054 3.3 V、1:4 HCSL/LVDS合成器。其特性在于具有減少EMI的擴頻;啟用/禁用每個輸出和選擇/關(guān)擴頻ON/OFF的I2C接口;引腳兼容ICS841S104I。

3)NB3N3002/5573

它具有以100 MHz頻率驅(qū)動NB3N106K/108K/111K的輸出性能。在扇出緩沖器輸出進行測量的結(jié)果顯示,含25 MHz晶體的NB3N3002/5573(時鐘生成器)以100 MHz模式驅(qū)動NB3N106K/108K/111K扇出緩沖器符合PCIe 1、2、3抖動及相位噪聲規(guī)范;為NB3N3002/557增加扇出緩沖器不會產(chǎn)生足夠的抖動或相位噪聲以產(chǎn)生無法符合PCIe 1、2、3相位噪聲及抖動規(guī)范的“系統(tǒng)”。

4)用于PCIe應(yīng)用的時鐘分配器件ZDB及扇出緩沖器

服務(wù)器平臺有3種時鐘拓撲結(jié)構(gòu):內(nèi)部系統(tǒng)時鐘、混合系統(tǒng)時鐘和外部系統(tǒng)時鐘。針對PCIe外部時鐘架構(gòu),安森美半導體提供多種專用時鐘選擇,包括時鐘產(chǎn)生器(NB3N3002/NB3N5573/NB3N51034/NB3N51054/NB3N51054/NB3N

51044) 、零延遲緩沖器(ZDB) NB3N1200K/NB3W1200L (可用于PCIe混合時鐘架構(gòu)),以及HCSL至HCSL扇出緩沖器(不需要精確調(diào)節(jié)時鐘沿使其與ZDB輸出同步的多PCIe參考時鐘產(chǎn)生器)。

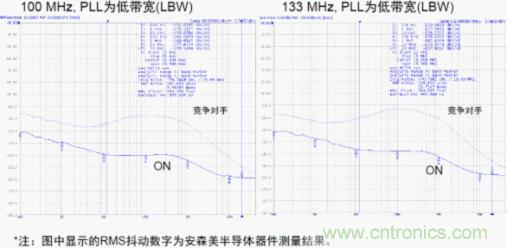

例如,NB3N1200K/NB3W1200L零延遲緩沖器(ZDB)帶12路HCSL/NMOS推挽輸出,特性包括:支持DIF SRC時鐘;12個差分時鐘輸出對@0.7V (NB3N1200K) ;12個低功耗NMOS推挽輸出對(NB3W1200L) ;針對100MHz和133 MHz優(yōu)化,符合PCIe 第2代/第3代和英特爾QPI相位抖動規(guī)范;符合低EMI擴頻;最低輸入至輸出延遲變化的偽外部固定反饋;每12個輸出的單獨OE控制引腳。兩者的相位噪聲均優(yōu)于競爭對手,見圖5。

圖5:NB3N1200K與競爭器件的相位噪聲性能比較

使用NB3N1200K或NB3W1200L時需注意,NB3W1200L是低能耗版本,用于要求低能耗的系統(tǒng),用于長度小于20英寸的較短長度輸出傳輸線路;NB3N1200K使用標準HCSL輸出設(shè)計,在輸出使用恒流源,可維持長于20英寸輸出傳輸線路的信號完整性。

另外,多個PLL分層布置時,用戶可調(diào)節(jié)帶寬對時鐘樹進行系統(tǒng)優(yōu)化。使用HBW(高帶寬)擴頻時鐘時用于維持擴頻特性,從而將輸入與輸出相位差減至最小;使用LBW (低帶寬)可濾除PLL帶寬內(nèi)的時鐘輸入抖動。

以下情況應(yīng)該使用ZDB或扇出緩沖器:使用零延遲緩沖器 (ZDB) (PLL模式) 時;維護同步時鐘沿對齊時;當時鐘生成至輸出傳播延遲至關(guān)重要時;用作扇出緩沖器時;當時鐘生成至扇出輸出傳播延遲不重要時。

5)新產(chǎn)品

安森美半導體還在開發(fā)一系列新產(chǎn)品來滿足英特爾白皮書規(guī)范,如帶19路HCSL/NMOS報推挽輸出的NB3N1900K/NB3W1900L ZDB,帶8路低能耗NMOS推挽輸出的NB3W800L ZDB,帶HCSL輸出的NB3N208K 1:8扇出緩沖器,以及帶HCSL輸出的扇出緩沖器NB3N106K、NB3N108K、NB3N111K和NB3N121K等。以上介紹的器件工作范圍為3.3 V ± 5-10 %,工業(yè)級溫度范圍均為-40°C至85°C,目標市場及應(yīng)用涵蓋服務(wù)器(PCIe、QPI和FB-DIMM),以及網(wǎng)絡(luò)(PCIe) 等。這些器件提供優(yōu)異性能。以NB3N1900K為例,其相位噪聲性能優(yōu)于競爭器件,見圖6。

圖6a:NB3N1900K與競爭器件的相位噪聲性能比較

圖6b:NB3N1900K與競爭器件的相位噪聲性能比較(續(xù))

總結(jié):

作為服務(wù)器應(yīng)用及其它多種應(yīng)用的時序方案供應(yīng)商,安森美半導體提供包括時鐘產(chǎn)生、零延遲緩沖器(ZDB)及扇出緩沖器等在內(nèi)的完整方案。公司的產(chǎn)品涵蓋計算機應(yīng)用的寬廣產(chǎn)品陣容,具有一流的相位噪聲和抖動性能以及極高的性價比優(yōu)勢,符合及超越第1代、第2代及第3代PCIe要求,可以直接升級眾多現(xiàn)有工業(yè)標準方案。