【導(dǎo)讀】今天,幾乎所有的電子設(shè)計都涉及到模數(shù)轉(zhuǎn)換器(ADC)。在簡單的應(yīng)用中,配套的MCU內(nèi)的ADC可能已經(jīng)足夠,而極端的高頻應(yīng)用則需要高速ADC。其他設(shè)計需要特別注意數(shù)據(jù)轉(zhuǎn)換器的類型和特性。

像模擬輸入濾波器這樣的設(shè)計挑戰(zhàn)通常需要額外的時間。不要忘了像十進位這樣的功能,它在一些設(shè)計中提供了好處。本文提出的建議可能有助于解決這些不同的設(shè)計考慮。

ADC的選擇

目前常用的ADC有三種基本類型:delta-sigma、逐次逼近寄存器(SAR)和用于RF的每秒千兆位采樣(GSPS)閃存或流水線ADC。您的應(yīng)用將決定必須進行數(shù)字化的信號類型。這些是與你的設(shè)計需求相匹配的主要規(guī)格:

采樣率?;疽?guī)則是,采樣率必須比要數(shù)字化的信號的最高頻率內(nèi)容大2倍或以上。換句話說,采樣率的一半的頻率被稱為奈奎斯特頻率;它是可以被轉(zhuǎn)換而不產(chǎn)生混疊的最高頻率信號。如果不符合這個標準,就會出現(xiàn)混疊。混疊會產(chǎn)生新的信號,干擾轉(zhuǎn)換過程。

分辨率。該規(guī)范定義了轉(zhuǎn)換的精度。分辨率是以可以測量的最小的輸入電壓增量來表示的。分辨率由輸出中的位數(shù)設(shè)定。位數(shù)越多,分辨率就越高。

動態(tài)范圍。這是最高和最低輸入電壓水平之間的最大范圍,以dB表示。與此規(guī)格相關(guān)的是無雜散動態(tài)范圍(SFDR),它定義了最高輸入振幅和本底噪聲中的峰值刺痛之間的范圍。

延遲。采樣脈沖的啟動和輸出位的出現(xiàn)之間的時間。

影響ADC選擇的其他因素是噪底和信噪比(SNR)。

在你的應(yīng)用中,功耗可能是一個主要關(guān)注點。功率的使用通常與采樣率成正比。

前兩個因素通常在一開始就被確定下來;然后選擇一個ADC架構(gòu)。Δ-Σ型ADC具有最高的分辨率,其數(shù)字輸出高達32位。然而,采樣率通常低于每秒10兆次(MSPS)。

SAR轉(zhuǎn)換器的分辨率高達18位,采樣率高達125MSPS。這一中檔類別適合許多應(yīng)用。GSPS ADC可提供超過10 GSPS的采樣率和10至14比特的分辨率,主要見于射頻設(shè)備和手機等產(chǎn)品。

對于廣泛的一般應(yīng)用,如工業(yè)設(shè)備,SAR是一個不錯的選擇。當需要高精度時,delta-sigma ADC是一個可靠的選擇。

基本設(shè)計標準

所有ADC都需要一個模擬輸入濾波器。它的主要目的是將輸入帶寬限制在只有要被數(shù)字化的信號上。其他信號,特別是輸入端的高頻成分,可能會產(chǎn)生混疊,造成轉(zhuǎn)換錯誤。這就需要一個低通濾波器,對所需信號中最高頻率成分以上的頻率進行急劇滾降。

模擬低通濾波器是有效的,但在試圖實現(xiàn)所需的衰減時,它們可能是大而復(fù)雜的處理方式。像有限輸入響應(yīng)(FIR)濾波器這樣的數(shù)字濾波器,有足夠數(shù)量的抽頭,可以提供卓越的選擇性。

也許最大限度地減少輸入濾波器要求的最簡單方法是使用一個大大高于混疊保護所需的最小采樣率。這種超采樣增加了輸入信號和混疊信號之間的距離,從而放松了對輸入濾波器的要求。

請記住,較高的采樣率對MCU、FPGA或其他接收ADC輸出的電路來說可能太快了。在轉(zhuǎn)換之后可以使用一個抽取濾波器來降低輸出速率。取樣提供了減少抗混疊濾波器要求的額外優(yōu)勢,因為取樣電路的低通濾波器效應(yīng)將降低二階和三階諧波。十取法還可以提高信噪比,每2個因子可提高-3dBFS(滿刻度分貝)。

任何使用ADC的設(shè)計中最關(guān)鍵的部分是模擬前端(AFE)。除了混疊濾波器之外,大多數(shù)ADC需要一些阻抗匹配電路、偏置網(wǎng)絡(luò)以及與ADC參考電壓的連接。所有這些都必須根據(jù)你的應(yīng)用進行定制。外部元件通常是必要的,因此在你的設(shè)計中要計劃一些額外的PCB空間。

一個值得考慮的ADC

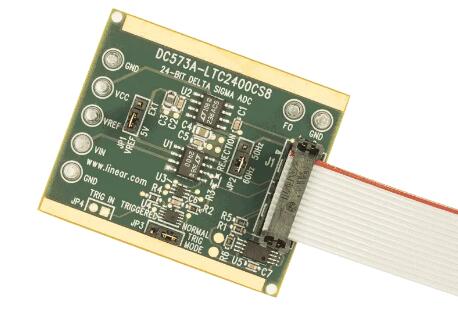

德州儀器公司提供了一系列的SAR ADC,可以與許多應(yīng)用相匹配。其中一個例子是ADC364x,這是一個雙通道14位CMOS器件,可以在10至65 MSPS的速率下采樣(見圖)。輸入可以是單端或差分的。輸出可以是并行或串行的,使用標準CMOS的LVDS輸出。輸出上的外部電阻控制電流。

一個關(guān)鍵特征是它的片上數(shù)字濾波器具有抽取功能。十取法有效地降低了輸出數(shù)據(jù)率,從而可以容納較慢的外部設(shè)備,如MCU或FPGA??梢赃x擇2、4、8、16或32的十進位。

使用ADC進行設(shè)計是一個復(fù)雜的過程,需要考慮許多相互關(guān)聯(lián)的因素。為尋找最佳可用的ADC而花費的時間將在以后的設(shè)計時間和成本節(jié)約中得到回報。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進行處理。

推薦閱讀: