【導(dǎo)讀】隨著數(shù)據(jù)轉(zhuǎn)換器的速度和分辨率不斷提升,對(duì)具有更低相位噪聲的更高頻率采樣時(shí)鐘源的需求也在不斷增長。時(shí)鐘輸入面臨的積分相位噪聲(抖動(dòng))是設(shè)計(jì)師在設(shè)計(jì)蜂窩基站、軍用雷達(dá)系統(tǒng)和要求高速和高性能時(shí)鐘信號(hào)的其他設(shè)計(jì)時(shí)面臨的眾多性能瓶頸之一。普通系統(tǒng)有多個(gè)低頻噪聲信號(hào),PLL 可將其上變頻至更高頻率,以便為這些器件提供時(shí)鐘。單個(gè)高頻PLL可以解決頻率轉(zhuǎn)換問題,但很難設(shè)計(jì)出環(huán)路帶寬足夠低,從而能夠?yàn)V除高噪聲參考影響的PLL。搭載低頻高性能VCO/VCXO和低環(huán)路帶寬的PLL可以清除高噪聲參考,但無法提供高頻 輸出。高速和噪聲過濾可以通過結(jié)合兩個(gè)PLL同時(shí)實(shí)現(xiàn):先是一個(gè)低頻窄環(huán)路帶寬器件(用于清除抖動(dòng)),其后是一個(gè)環(huán)路帶寬較寬的高頻器件。

有些現(xiàn)代雙環(huán)路模擬 PLL 集成于單個(gè)芯片之上,允許設(shè)計(jì)師 減少低頻參考抖動(dòng),同時(shí)還能提供高頻、低相位噪聲輸出。這 就節(jié)省了寶貴的 PCB 電路板面積,而且允許要求不同頻率的 多個(gè)器件以同一相位對(duì)齊源為時(shí)鐘源。

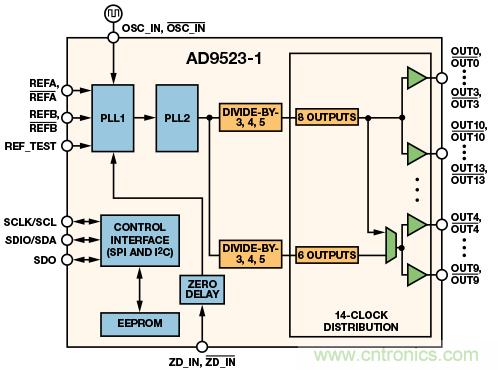

AD9523, AD9523-1和 AD9524 時(shí)鐘發(fā)生器(如圖 1 所示)由 兩個(gè)串聯(lián)模擬PLL構(gòu)成。第一個(gè)PLL (PLL1)清除參考抖動(dòng), 第二個(gè)PLL (PLL2)生成高頻相位對(duì)齊輸出。 PLL2 也可生成高 基頻,再以此為基礎(chǔ)衍生出各種低頻。PLL1 使用一個(gè)外部低 頻VCXO和一個(gè)部分嵌入式三階環(huán)路濾波器來構(gòu)成一個(gè)PLL, 其環(huán)路帶寬范圍為 30 Hz至 100 Hz。該環(huán)路的帶寬直接影響 將傳播至輸出的參考輸入相位噪聲量。 PLL2 使用一個(gè)內(nèi)部高 速VCO(中心頻率為 3.8 GHz,AD9523-1 為 3 GHz)和一個(gè) 部分嵌入式三階環(huán)路濾波器,其額定環(huán)路帶寬約為 500 kHz。 該內(nèi)部VCO的帶寬和相位噪聲會(huì)直接影響整體輸出的寬帶相 位噪聲。

圖 1 AD9523-1 的功能框圖

許多工程師把雙環(huán)路 PLL 當(dāng)作頻率轉(zhuǎn)換器,可減少固定量的 參考輸入抖動(dòng),但更加準(zhǔn)確的做法是將其視為低相位噪聲頻率 轉(zhuǎn)換器,其性能受到各個(gè) PLL 的環(huán)路帶寬以及 VCO/VCXO 的 相位噪聲曲線的影響。

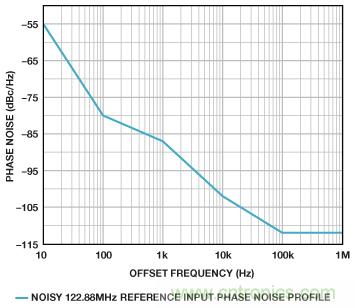

ADIsimCLK™ 仿真工具為確定參考相位噪聲對(duì)雙環(huán)路PLL輸出 相位噪聲的影響提供了一種簡便的方法。本例使用ADIsimCLK 來模擬高噪聲參考對(duì)AD9523-1 整體相位噪聲的影響。圖 2 所 示為一個(gè)仿真 122.88 MHz參考輸入的典型相位噪聲曲線。

圖 2 122.88 MHz 時(shí)的參考相位噪聲曲線

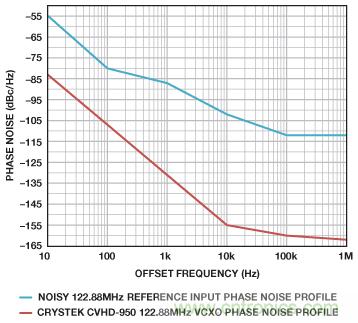

PLL1 依賴高性能 VCXO 和低環(huán)路帶寬來衰減參考相位噪聲, 從而允許 VCXO 的相位噪聲占據(jù)主導(dǎo)地位。本例采用一個(gè) Crystek CVHD-950 VCXO來生成與參考輸入相同的輸出頻率。 這幅圖直接比較了 PLL1 輸出端出現(xiàn)的參考相位噪聲量。圖 3 對(duì) Crystek CVHD-950 VCXO 的相位噪聲曲線與參考輸入相位 噪聲進(jìn)行了比較。

圖 3 122.88 MHz 時(shí)的 Crystek CVHD-950 相位噪聲曲線

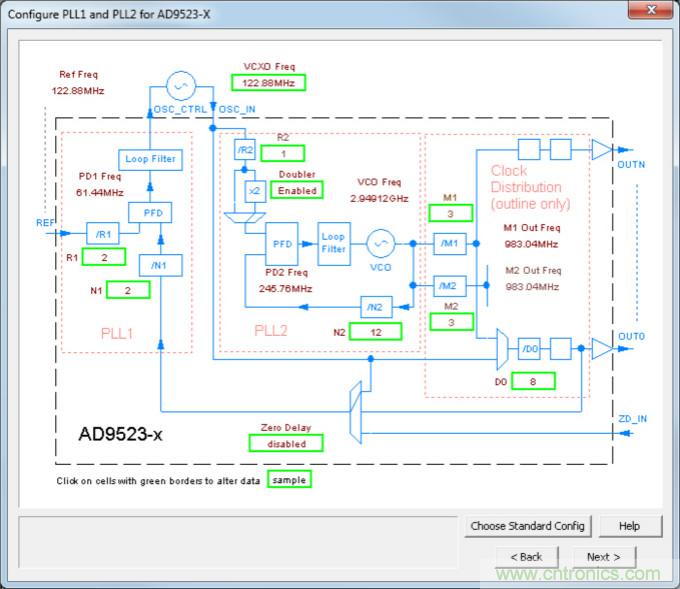

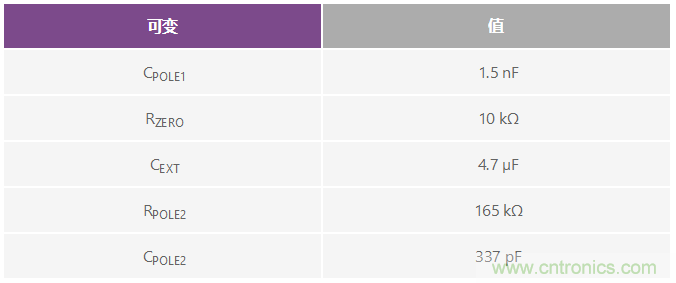

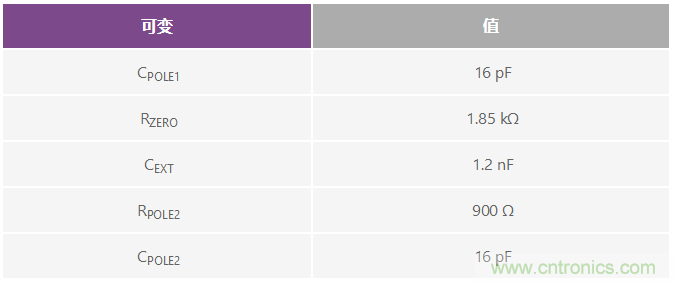

圖 4 和表 1 所示為 ADIsimCLK 配置參數(shù),這些參數(shù)用來仿真 針對(duì)圖 3 所示參考輸入和 PLL1 VCXO 相位噪聲曲線, AD9523-1 的 PLL1 輸出相位噪聲響應(yīng)情況。表 2 所示為 ADIsimCLK 在這些設(shè)置下生成的 PLL1 環(huán)路濾波器值。

圖 4 ADIsimCLK v1.5 中的 AD9523-1 配置

表 1 PLL1配置參數(shù)

表 2 ADIsimCLK產(chǎn)生的 PLL1環(huán)路濾波器元件值

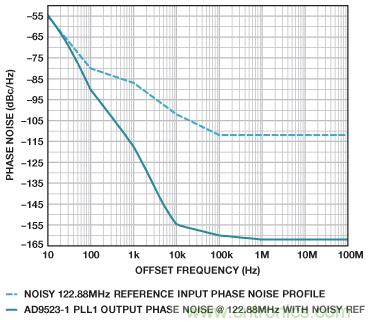

圖5展示的是通過ADIsimCLK生成的PLL1在122.88 MHz條 件下的仿真輸出(實(shí)線),以及高噪聲 122.88 MHz 參考頻率 的原始相位噪聲曲線(虛線)。請(qǐng)注意,PLL1 的輸出相位噪 聲遠(yuǎn)遠(yuǎn)低于原始參考輸入相位噪聲。PLL1 的環(huán)路帶寬會(huì)顯著 衰減參考頻率的相位噪聲,使 VCXO 的低相位噪聲曲線可以 在 30 Hz 環(huán)路濾波器截止頻率之后占據(jù)主導(dǎo)地位。如果參考相 位噪聲在全部偏移頻率上都在增加,則輸出相位噪聲將只會(huì)隨 PLL1 環(huán)路帶寬而增加。

圖 5 采用高抖動(dòng)參考頻率的 PLL1 輸出相位噪聲

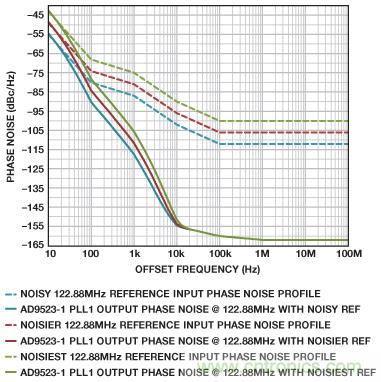

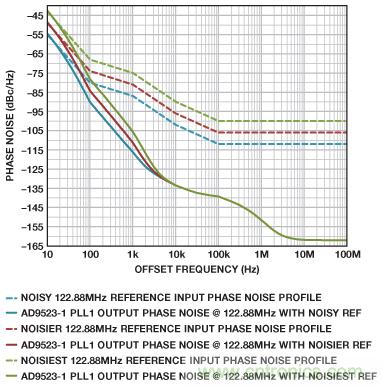

圖 6 和圖 7 展示的是 AD9523-1 PLL1 輸出,其相位噪聲比 圖 2 中的高噪聲參考頻率分別高出 6 dB 和 12 dB。 在頻偏約 20 kHz 以外,PLL1 的輸出相位噪聲由其環(huán)路設(shè)置和 VCXO 的性能所主導(dǎo)。因此,由于積分范圍始于 20 kHz 失調(diào),抖 動(dòng)性能只會(huì)略微變化,盡管參考輸入相位噪聲會(huì)增加 12 dB。 這是在設(shè)計(jì)時(shí)使 PLL1 具備低環(huán)路帶寬并使用低相位噪聲 VCXO 帶來的直接結(jié)果。必須使用具有低 KVCO 的低頻、高 性能 VCXO 來形成足夠低的 PLL1 環(huán)路帶寬,以便實(shí)現(xiàn)抖動(dòng) 的清除。

圖 6 采用各種參考頻率的 PLL1 輸出相位噪聲

圖 7 采用各種參考頻率的 PLL1 輸出相位噪聲

PLL1 的低相位噪聲輸出充當(dāng) PLL2 的參考頻率,以形成相位 對(duì)齊、頻率更高的輸出。

PLL2含有一個(gè)內(nèi)部VCO (其中心頻率為3 GHz), 最高支持1 GHz 的輸出頻率。為了比較高噪聲輸入?yún)⒖碱l率和AD9523系列器件 的整體相位噪聲,需要在 122.88 MHz 下考察所得到的相位噪聲 (FVCO 除以 24)。注意,PLL2 的輸出一般用于頻率轉(zhuǎn)換或高頻 輸出。表 3 所示為輸入 ADIsimCLK 的 PLL2 配置參數(shù)。表 4 所 示為ADIsimCLK在這些設(shè)置下生成的PLL2環(huán)路濾波器值。

表 3 PLL2配置參數(shù)

表 4 來自 ADIsimCLK的 PLL2環(huán)路濾波器元件值

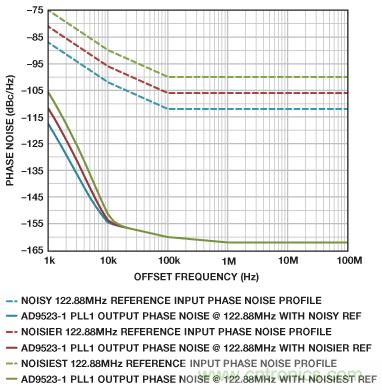

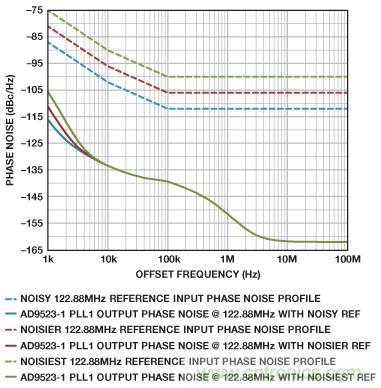

圖 8 和圖 9 對(duì)各參考輸入相位噪聲與通過 ADIsimCLK 仿真得 到的 AD9523-1 輸出相位噪聲結(jié)果進(jìn)行了比較。請(qǐng)注意 10 kHz 和 1 MHz 之間增加的相位噪聲基底。這是因?yàn)?PLL2 的內(nèi)部 VCO 相位噪聲的關(guān)系。

圖 8 采用各種參考頻率的 PLL2 輸出相位噪聲

圖 9 采用各種參考頻率的 PLL2 輸出相位噪聲(放大圖)

PLL2 中的內(nèi)部 VCO 相位噪聲在大約頻偏為 5 kHz 之后足夠 高,會(huì)開始主導(dǎo)器件的總輸出相位噪聲。在頻偏 5 kHz 區(qū)域之 后,增加的參考相位噪聲對(duì)輸出相位噪聲的影響很小。

結(jié)論

PLL1 的抖動(dòng)清除功能可以防止多數(shù)參考輸入相位噪聲到達(dá) PLL2。高噪聲參考輸入確實(shí)會(huì)影響近載波相位噪聲(頻偏 10kHz 以下),但器件的總輸出抖動(dòng)是由器件的性能而非參考頻率的性能所主導(dǎo)的。對(duì)于積分抖動(dòng)計(jì)算值處于 12 kHz 至 20 MHz 之間的情況,輸出抖動(dòng)很可能相同,不受輸入抖動(dòng)的影 響。真正的性能指標(biāo)不是聲稱雙環(huán)路模擬 PLL 可以衰減多少 抖動(dòng),而是它會(huì)產(chǎn)生多少抖動(dòng)。

推薦閱讀: