【導(dǎo)讀】低壓差穩(wěn)壓器(LDO)可用來(lái)為高速時(shí)鐘�、模數(shù)轉(zhuǎn)換器����、數(shù)模轉(zhuǎn)換器、壓控振蕩器和鎖相環(huán)這些電路供電��。噪聲對(duì)于高性能模擬電路的設(shè)計(jì)人員而言極為重要����。降低噪聲的關(guān)鍵是保持LDO噪聲增益接近單位增益,且不影響交流性能或直流閉環(huán)增益��。

本文描述簡(jiǎn)單的RC網(wǎng)絡(luò)如何降低可調(diào)節(jié)輸出低壓差穩(wěn)壓器的輸出噪聲�����。本文通過(guò)實(shí)驗(yàn)數(shù)據(jù)來(lái)演示這一簡(jiǎn)單方法的有效性���。雖然RC網(wǎng)絡(luò)的主要目的是降噪��,但它也能改善電源抑制和負(fù)載瞬態(tài)響應(yīng)��。

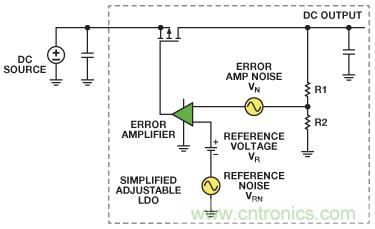

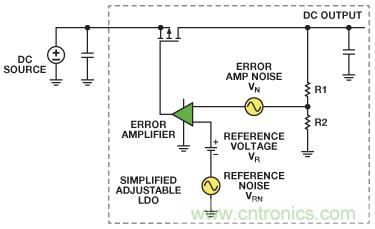

圖 1 顯示典型可調(diào)節(jié)輸出LDO的簡(jiǎn)化框圖���。輸出電壓VOUT等于基準(zhǔn)電壓與誤差放大器直流閉環(huán)增益的乘積:VOUT = VR × (1 + R1/R2),其中(1 + R1/R2)是誤差放大器的直流閉環(huán)增益�。

誤差放大器噪聲VN和基準(zhǔn)電壓噪聲VRN放大相同的倍數(shù),使輸出噪聲與設(shè)定的輸出電壓成比例增加�。這使得輸出電壓上的噪聲比參考電壓高但小于 2 倍,輸出噪聲適度增加但在敏感應(yīng)用 中哪怕這種適度增加都有可能無(wú)法接受�。

圖 1. 顯示內(nèi)部噪聲源的可調(diào)節(jié) LDO 簡(jiǎn)化框圖

LDO 噪聲

LDO的主要噪聲源是內(nèi)部基準(zhǔn)電壓和誤差放大器。當(dāng)今的器件工作時(shí)內(nèi)部偏置電流為幾百nA或更低����,可實(shí)現(xiàn)高達(dá) 15 µA的靜態(tài)電流���。這些小電流需要使用高達(dá) 1 GΩ的偏置電阻,使得誤差放大器和基準(zhǔn)電壓電路相比分立式部署更為噪雜��。典型LDO采用電阻分壓器設(shè)置輸出電壓�,因此噪聲增益等于交流閉環(huán)增益,其結(jié)果與直流閉環(huán)增益相同���。

降低 LDO 噪聲

兩種降低LDO噪聲的主要方法是過(guò)濾基準(zhǔn)電壓����,以及降低誤差放大器的噪聲增益���。某些LDO可采用外部電容過(guò)濾基準(zhǔn)電壓���。事實(shí)上,許多所謂的超低噪聲LDO都需要使用外部降噪電容來(lái)實(shí)現(xiàn)其低噪聲性能����。這項(xiàng)技術(shù)的缺點(diǎn)是誤差放大器噪聲和任何殘留的基準(zhǔn)電壓噪聲依然會(huì)通過(guò)交流閉環(huán)增益放大。這使得噪聲與輸出電壓成正比。

降低誤差放大器的噪聲增益可使LDO的輸出噪聲不隨輸出電壓上升而大幅增加����。不幸的是�,這對(duì)于固定輸出LDO而言是不可行的,因?yàn)榉答伖?jié)點(diǎn)不易獲得��。然而幸運(yùn)的是��,該節(jié)點(diǎn)在可調(diào)節(jié)輸出LDO中容易獲得�。

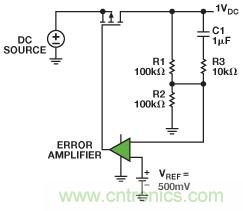

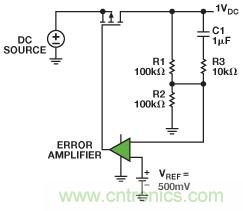

圖 2 顯示的是一個(gè)可調(diào)節(jié)輸出LDO,其中R1 和R2 設(shè)置輸出電壓���。由R3 和C1 構(gòu)成的網(wǎng)絡(luò)可降低誤差放大器的交流增益�����。為確保具有低相位裕量(或者非單位增益穩(wěn)定)LDO的穩(wěn)定性��,選擇R3 將放大器的高頻增益設(shè)為 1.1 左右���。如需降低 1/f區(qū)的噪聲,則需選擇C1 將低頻零點(diǎn)設(shè)為 10 Hz以下�。

圖 2. 降低可調(diào)節(jié)輸出 LDO 噪聲增益的簡(jiǎn)單 RC 網(wǎng)絡(luò)

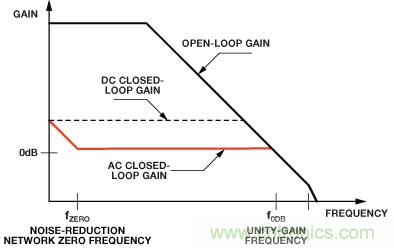

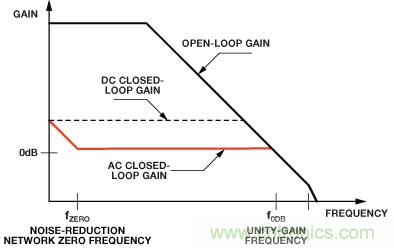

圖 3 將交流閉環(huán)增益(其降噪網(wǎng)絡(luò)經(jīng)過(guò)適當(dāng)設(shè)計(jì))與開(kāi)環(huán)增益 以及未經(jīng)過(guò)修改的閉環(huán)增益進(jìn)行比較。采用降噪網(wǎng)絡(luò)后,在大 部分帶寬中交流增益接近單位增益��,因此基準(zhǔn)電壓噪聲和誤差 放大器噪聲放大的程度較低��。

圖 3. LDO 環(huán)路增益與頻率的關(guān)系(帶降噪網(wǎng)絡(luò))

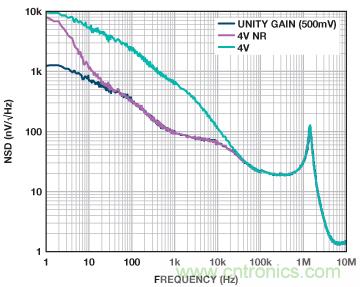

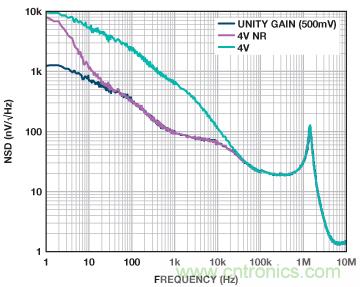

圖 4 顯示降噪網(wǎng)絡(luò)對(duì)ADP125 LDO噪聲譜密度的影響���。該曲線比較了使用和不使用降噪網(wǎng)絡(luò)時(shí)����,4 V電壓下的噪聲譜密度�,以及單位增益下的噪聲譜密度。

可看到在 20 Hz至 2 kHz范圍內(nèi)���,噪聲性能得到了極大的改善���。在R1 和C1 組成的零點(diǎn)之上,采用降噪網(wǎng)絡(luò)的噪聲特性與單位 增益時(shí)基本相同��。噪聲譜密度曲線在 20 kHz以上融合���,這是因?yàn)檎`差放大器的閉環(huán)增益與開(kāi)環(huán)增益相交�����,無(wú)法進(jìn)一步降低噪聲增益��。

圖 4. 可調(diào)節(jié)輸出 LDO ADP125 的噪聲譜密度

電源抑制

此頻率范圍內(nèi)的電源抑制比(PSRR)同樣得到了改善����。PSRR衡量電路抑制電源輸入端出現(xiàn)的外來(lái)信號(hào)(噪聲和紋波),使這些 干擾信號(hào)不至于破壞電路輸出的能力�����。PSRR定義為:PSRR = VEIN/VEOUT�。這還可以用dB表示:PSR = 20 × log(VEIN/VEOUT)���, 其中VEIN 和VEOUT為出現(xiàn)在輸入端和輸出端的外來(lái)信號(hào)����。

對(duì)于大部分模擬電路�,PSR用于為電路內(nèi)部供電的引腳。然而���,對(duì)于LDO����,輸入引腳不僅為內(nèi)部電路供電,還為穩(wěn)壓輸出提供負(fù)載電流����。

改善 PSR

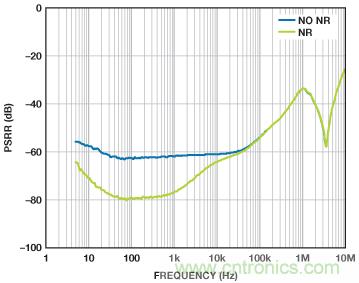

使用降噪網(wǎng)絡(luò)降低可調(diào)節(jié)輸出LDO輸出噪聲還有另一個(gè)優(yōu)勢(shì),即還能改善低頻PSR��。圖 2 中的R1�����、R3 和C1 形成超前-滯后網(wǎng)絡(luò)����,其零點(diǎn)大致在 1/(R1 × C1)處,極點(diǎn)大致在 1/(R3 × C1)處�����。超前-滯后網(wǎng)絡(luò)為補(bǔ)償環(huán)路提供正饋功能�,因此能改善PSR。對(duì)于低于閉環(huán)增益和開(kāi)環(huán)增益融合的頻率而言�����,若改善的量以dB表示����,則數(shù)值約為 20 × log(1 + R1/R3)�。

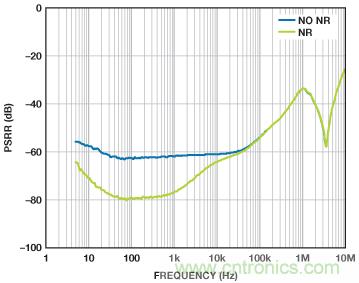

圖 5 顯示降噪網(wǎng)絡(luò)對(duì)可調(diào)節(jié)輸出LDO ADP7102 所產(chǎn)生的影響����。若輸出為 9 V,則R1 = 64 kΩ����、R2 = 10 kΩ、R3 = 1 kΩ����、C1 = 1 μF�����。R1 和C1 在大約 2.5 Hz時(shí)建立的零點(diǎn)證明 10 Hz以上PSRR得到了改善�。在 100 Hz至 1 kHz范圍內(nèi),總PSRR增加約 17 dB��。改善情況直到約 20 kHz處才有所下降�����;在該處,開(kāi)環(huán)增益和閉環(huán)增益融合����。

圖 5. 使用和不使用降噪網(wǎng)絡(luò)的可調(diào)節(jié)輸出

LDO ADP7102/ADP7104 的 PSRR

瞬態(tài)負(fù)載改善

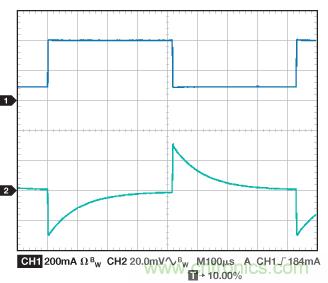

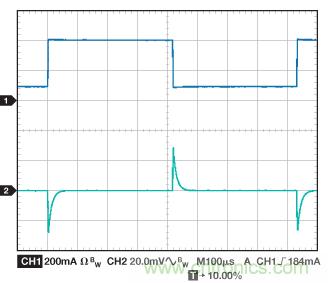

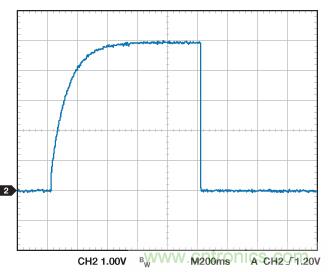

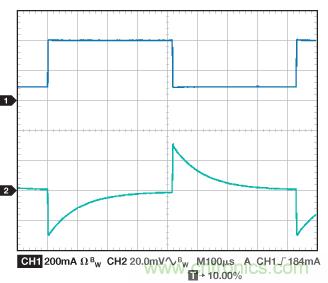

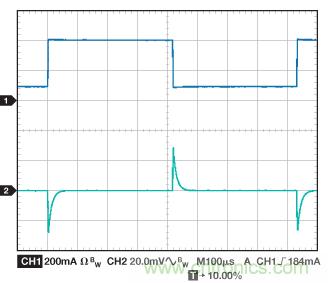

降噪網(wǎng)絡(luò)還能改善LDO的瞬態(tài)負(fù)載響應(yīng)。同樣��,R1�、R3 和C1執(zhí)行補(bǔ)償環(huán)路的前饋功能。負(fù)載瞬態(tài)的高頻分量——由未經(jīng)衰減的誤差放大器檢測(cè)——允許誤差放大器快速響應(yīng)負(fù)載瞬態(tài)����。圖 6 顯示使用與不使用降噪網(wǎng)絡(luò)時(shí)的ADP125 負(fù)載瞬態(tài)響應(yīng)情況。使用降噪網(wǎng)絡(luò)后���,LDO能在 50 μs內(nèi)響應(yīng)負(fù)載瞬態(tài)�,而不使用降噪網(wǎng)絡(luò)時(shí)為 500 μs����。

(a) 不使用降噪網(wǎng)絡(luò)

(b) 使用降噪網(wǎng)絡(luò)

圖 6. 可調(diào)節(jié)輸出 LDO ADP125 的瞬態(tài)負(fù)載響應(yīng)

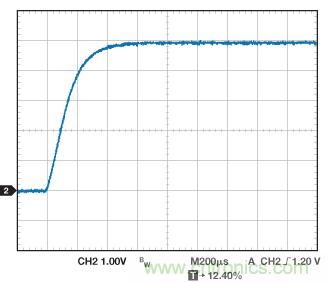

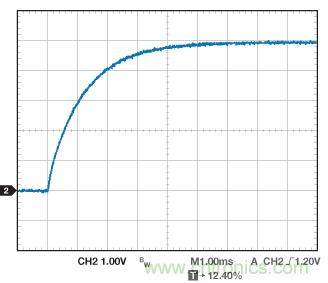

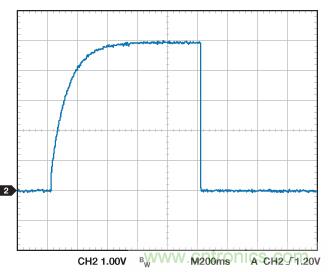

對(duì)啟動(dòng)時(shí)間的影響

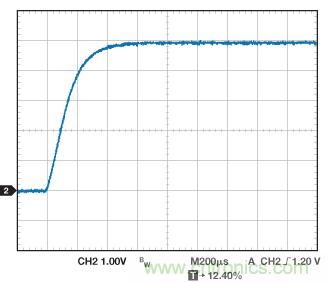

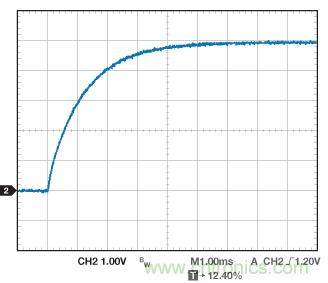

降噪網(wǎng)絡(luò)的一個(gè)缺點(diǎn)是它會(huì)極大地增加啟動(dòng)時(shí)間。圖 7 顯示使用與不使用降噪網(wǎng)絡(luò)時(shí)的ADP125 啟動(dòng)時(shí)間��。正常啟動(dòng)時(shí)間約為 600 μs�����。若C1 = 10 nF,則啟動(dòng)時(shí)間增至 6 ms�����;若C1 = 1 μF���,則增至 600 ms�。對(duì)于電路完全上電后不再開(kāi)關(guān)LDO的應(yīng)用而言���,啟動(dòng)時(shí)間增加應(yīng)該不是問(wèn)題�����。

(a) 不使用降噪網(wǎng)絡(luò)

(b) 使用降噪網(wǎng)絡(luò),C1 = 10 nF

(c) 使用降噪網(wǎng)絡(luò)��,C1 = 1 µF

圖 7. 可調(diào)節(jié)輸出 LDO ADP125 的啟動(dòng)時(shí)間

結(jié)論

通過(guò)添加一個(gè)簡(jiǎn)單的RC降噪網(wǎng)絡(luò),便可明顯改善可調(diào)節(jié)輸出LDO的噪聲���、電源抑制和瞬態(tài)性能,為高速時(shí)鐘�����、模數(shù)轉(zhuǎn)換器、數(shù)模轉(zhuǎn)換器����、壓控振蕩器和鎖相環(huán)等噪聲敏感型應(yīng)用帶來(lái)極大的優(yōu)勢(shì)。

ADP125, ADP171, ADP1741, ADP1753, ADP1755, ADP7102, ADP7104, 和 ADP7105等LDO均具有這種通用架構(gòu)�,并將極大 地受益于降噪網(wǎng)絡(luò)的使用。該技巧可用于與圖 2 所示相似的 LDO架構(gòu)���,在該架構(gòu)中�,基準(zhǔn)電壓噪聲和誤差放大器噪聲均由 直流閉環(huán)增益放大���,因此輸出噪聲與輸出電壓成比例關(guān)系����。

較新的超低噪聲LDO——比如ADM7151不會(huì)得益于此降 噪網(wǎng)絡(luò)����,因?yàn)樵摷軜?gòu)采用單位增益LDO誤差放大器,所以基準(zhǔn)電壓等于輸出電壓����。此外,內(nèi)部基準(zhǔn)電壓濾波器極點(diǎn)低于 1 Hz��,可極大地過(guò)濾基準(zhǔn)電壓,并消除幾乎全部基準(zhǔn)電壓噪聲影響�。

推薦閱讀: