【導(dǎo)讀】有源鉗位正激(ACF)控制器在高頻dc-dc模塊中很受歡迎:近零電壓開(kāi)關(guān)、減小尺寸的磁性器件和高能效的設(shè)計(jì)是ACF的特點(diǎn)。如果設(shè)計(jì)功率級(jí)需要注意任何高功率設(shè)計(jì)��,那么從轉(zhuǎn)換器的控制-輸出傳遞函數(shù)可以很好地了解補(bǔ)償策略,以滿(mǎn)足交越和相位裕度等設(shè)計(jì)目標(biāo)�。本文將先論述ACF傳遞函數(shù)���,然后再給出一個(gè)典型的補(bǔ)償示例�����。

1.前言

有源鉗位正激(ACF)控制器在高頻dc-dc模塊中很受歡迎:近零電壓開(kāi)關(guān)���、減小尺寸的磁性器件和高能效的設(shè)計(jì)是ACF的特點(diǎn)。如果設(shè)計(jì)功率級(jí)需要注意任何高功率設(shè)計(jì)�,那么從轉(zhuǎn)換器的控制-輸出傳遞函數(shù)可以很好地了解補(bǔ)償策略,以滿(mǎn)足交越和相位裕度等設(shè)計(jì)目標(biāo)�����。本文將先論述ACF傳遞函數(shù)�,然后再給出一個(gè)典型的補(bǔ)償示例���。

2.功率級(jí)運(yùn)行

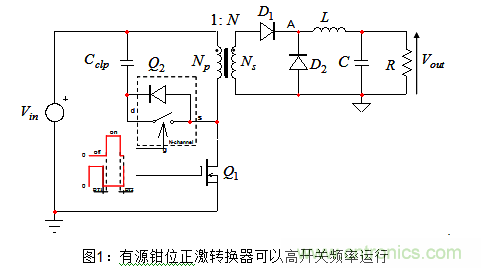

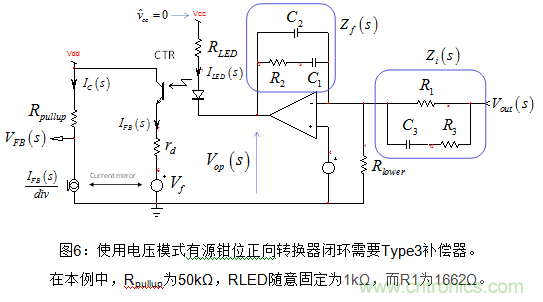

圖1顯示的是一個(gè)ACF的簡(jiǎn)化電路圖,其具體運(yùn)行細(xì)節(jié)可見(jiàn)參考文獻(xiàn)[1]。正常情況下����,晶體管Q1在經(jīng)典的正激轉(zhuǎn)換器中工作���,但當(dāng)它關(guān)斷時(shí)�,其退磁過(guò)程會(huì)涉及到鉗位電容Cclp和初級(jí)電感Lmag之間的諧振周期��。一部分存儲(chǔ)在磁化電感中的能量會(huì)將漏極連接處的集總電容轉(zhuǎn)移����,同時(shí)VDS(t)上升,直到找到流過(guò)Q2體二極管的路徑。然后�����,通過(guò)在零電壓開(kāi)關(guān)(ZVS)條件下導(dǎo)通Q2��,使后者短路:現(xiàn)在,Q1的漏極被鉗位到Vin加Cclp的電壓Vclp。考慮到Lmag和Cclp之間的諧振周期�,循環(huán)電流最終會(huì)反轉(zhuǎn)��,并流過(guò)Q2(導(dǎo)通狀態(tài))和磁化電感Lmag�。

在某個(gè)點(diǎn),控制器將指示Q2開(kāi)通��,迫使電流離開(kāi)包括Cclp在內(nèi)的網(wǎng)格����,自然地流過(guò)輸入源Vin和漏極集總電容:漏極節(jié)點(diǎn)開(kāi)始下降����,直到一個(gè)新的開(kāi)關(guān)周期,從而降低了導(dǎo)通損耗�。

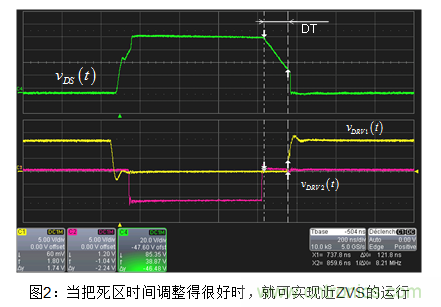

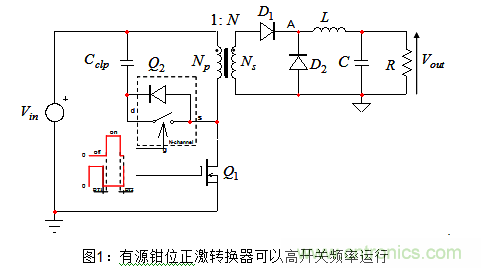

如圖2所示����,在MOSFET轉(zhuǎn)換之間插入了一個(gè)死區(qū)時(shí)間���,從而提供了產(chǎn)生漏源諧振周期的時(shí)間�����,該周期現(xiàn)在涉及Clump的Lmag���,以達(dá)到一個(gè)谷點(diǎn)��。在某些運(yùn)行條件下(較小的輸出電流)����,漏波觸地會(huì)導(dǎo)致零導(dǎo)通損耗�。

3.傳遞函數(shù)

在補(bǔ)償轉(zhuǎn)換器或任何系統(tǒng)之前�����,您需要功率級(jí)的控制-輸出傳輸函數(shù)。換句話(huà)說(shuō)�����,如果您想用正弦波來(lái)激勵(lì)控制輸入�,這里指的是脈寬調(diào)制器(PWM)���,那如何通過(guò)功率級(jí)來(lái)傳輸信息�,并在輸出中產(chǎn)生響應(yīng)呢�?將響應(yīng)與激勵(lì)聯(lián)系起來(lái)的數(shù)學(xué)關(guān)系就是我們需要的傳遞函數(shù)H�。

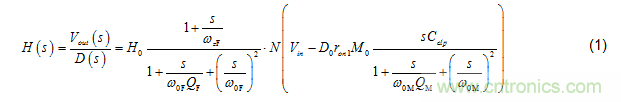

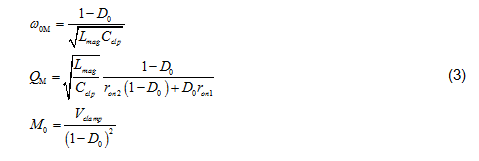

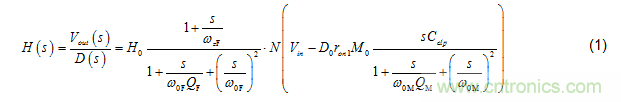

公式(1)導(dǎo)出了電壓模式下ACF的控制-輸出傳遞函數(shù),通過(guò)四階多項(xiàng)式描述了該轉(zhuǎn)換器:

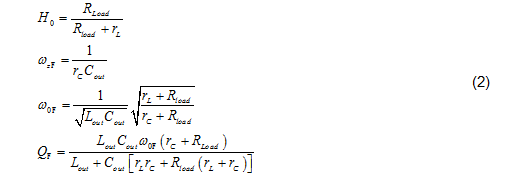

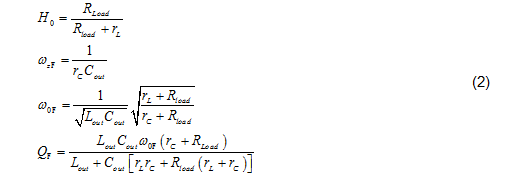

方程由兩個(gè)部分組成:左邊是經(jīng)典正激轉(zhuǎn)換器項(xiàng)�,其中:

公式(1)中的第二項(xiàng)表示有源鉗位電路的增加�����,以及圍繞Cclp和Lmag建立諧振網(wǎng)絡(luò)的影響:

在這些表達(dá)式中,rL和rC分別表示輸出電感(Lout)和電容(Cout)等效串聯(lián)電阻(ESR)���,ron1表示主開(kāi)關(guān)晶體管rDS(on),ron2表示有源鉗位晶體管rDS(on)��,N表示變壓器匝比���,D0表示靜態(tài)占空比。

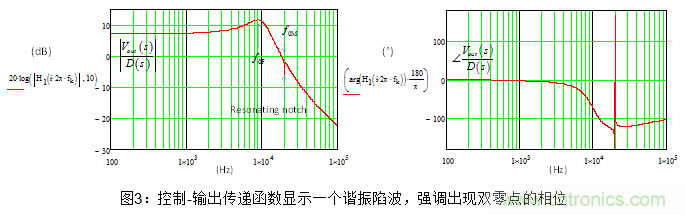

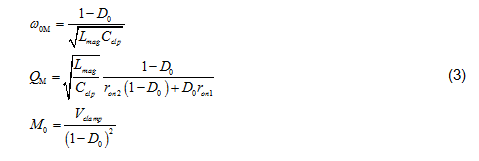

根據(jù)該表達(dá)式�,我們可獲得10-Hz至100-kHz頻率范圍的幅值和相位響應(yīng)的波特圖(如圖3所示)��。各器件的值即為由安森美半導(dǎo)體的NCP1566參考文獻(xiàn)[2]供電的3.3-V/30-A dc-dc模塊的值���。有源鉗位部分是特意非阻尼的,并假定Q2是低rDS(on)的MOSFET。

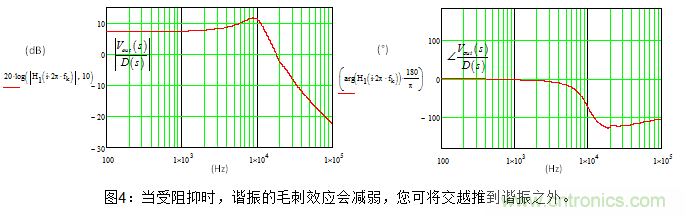

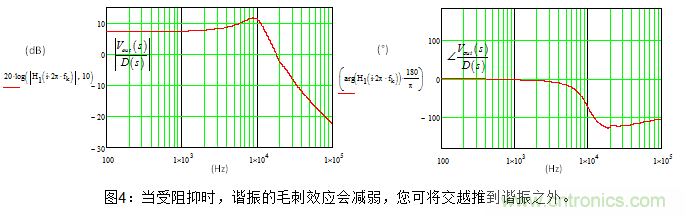

當(dāng)頻率達(dá)到公式(3)所描述的諧振時(shí)�����,您可觀(guān)察到受相位嚴(yán)重失真影響的幅值毛刺�����。幅值下降歸因于一次側(cè)諧振電流的突增����,這導(dǎo)致了一次側(cè)功率MOSFET Q1的壓降����。如公式(1)中右側(cè)項(xiàng)所示��,此壓降會(huì)從輸入電壓Vin中減去��,并創(chuàng)建可觀(guān)察到的響應(yīng)陷波。根據(jù)參考文獻(xiàn)[3]和文獻(xiàn)[4]的建議,選擇一個(gè)在Lmag-Cclp的最小諧振頻率之前的交越點(diǎn)是明智的,因?yàn)榇藭r(shí)存在嚴(yán)重的相位滯后。但是,如果在有源鉗位電路中施加適當(dāng)?shù)淖枘?���,則可以擴(kuò)展交越�。如參考文獻(xiàn)[5]所示��,在瞬態(tài)條件下,必須仔細(xì)研究這種決策對(duì)主MOSFET漏源峰值電壓的影響。圖4顯示相同的傳遞函數(shù)�,現(xiàn)在被Q2的2.5-ΩrDS(on)所抑制:幅值和相位響應(yīng)非常接近經(jīng)典正激轉(zhuǎn)換器的幅值和相位響應(yīng),而且可以在諧振陷波之外選擇fc��。

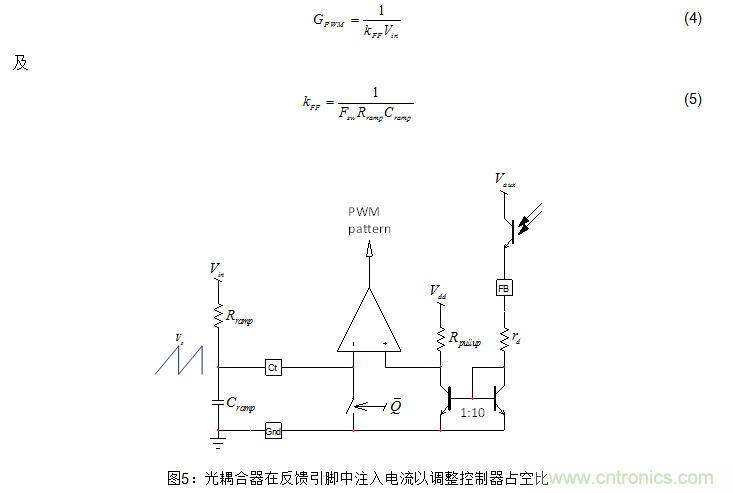

4.脈寬調(diào)制器

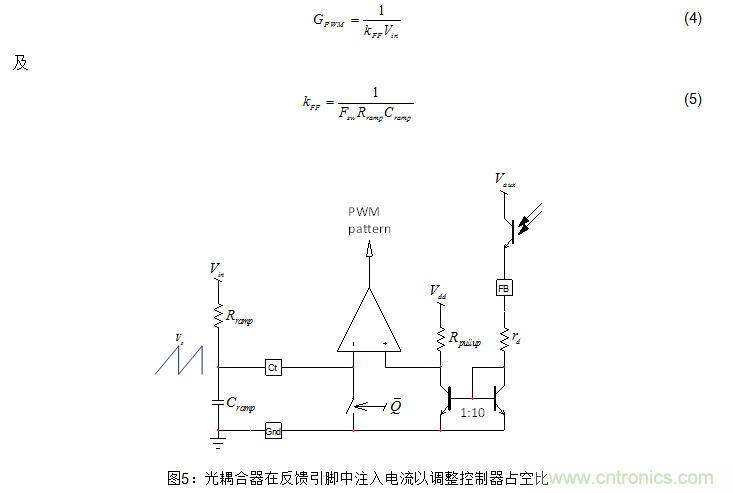

公式 (1)中給出的表達(dá)式不包括PWM模塊的影響���。在一個(gè)隔離開(kāi)的dc-dc轉(zhuǎn)換器中����,調(diào)節(jié)回路位于二次側(cè)����,光耦合器會(huì)偏置控制器反饋引腳來(lái)控制占空比��。在大功率轉(zhuǎn)換器中常見(jiàn)的一種方案是并聯(lián)調(diào)節(jié)器:光耦合器不是通過(guò)公共發(fā)射極配置將引腳拉低至接地��,而是通過(guò)發(fā)射極連接控制器并注入電流����。此電流在內(nèi)部呈鏡像���,可以拉低一個(gè)由50kΩ電阻加載的內(nèi)部節(jié)點(diǎn)���。這種電壓偏置PWM比較器�����,可確保穩(wěn)壓�。當(dāng)輸入動(dòng)態(tài)電阻壓降較小時(shí)���,由于準(zhǔn)恒定VCE電壓,該技術(shù)使米勒效應(yīng)最小化:光耦合器極被推到更高的頻率,避免閉環(huán)時(shí)發(fā)生問(wèn)題�����。動(dòng)態(tài)電阻rd=400Ω�����,但對(duì)頻率分析不產(chǎn)生影響�����。如果將電容反饋引腳接地,則會(huì)產(chǎn)生影響�����。但是�,除此配置之外,阻抗需為ac���,因?yàn)閱为?dú)的光耦合器可以調(diào)節(jié)輸入電流。此電流被10除(單位記為div)��,并通過(guò)拉高阻抗,調(diào)節(jié)內(nèi)部操作點(diǎn)��。

在倒相引腳上�,定時(shí)電容Cramp由取決于輸入電壓的電流充電����。因此,模擬鋸齒波的斜率將與輸入電壓有關(guān)�����,隨著Vin變化而動(dòng)態(tài)地改變?cè)鲆妗4伺渲脤?shí)現(xiàn)我們所謂的前饋操作��。可能顯示參考文獻(xiàn)[6]該調(diào)制單元的小信號(hào)增益等于:

在公式(1)中,您可看到在方程的右邊出現(xiàn)了Vin,表示傳輸函數(shù)的直流增益(s=0)將隨輸入電壓的變化而變化。因此,交越頻率和穩(wěn)定性也許都會(huì)受到影響���。通過(guò)PWM傳遞函數(shù)(公式(4)),分母中的Vin抵消了輸入電壓的影響,在輸入范圍內(nèi)穩(wěn)定了環(huán)路增益和交越頻率��。

5.Type 3補(bǔ)償器

為設(shè)計(jì)ACF轉(zhuǎn)換器的環(huán)路增益����,我們需要將PWM模式激勵(lì)因子D(s)與觀(guān)察到的變量Vout(s)響應(yīng)聯(lián)系起來(lái)的傳遞函數(shù)。我們將通過(guò)極點(diǎn)-零點(diǎn)位置應(yīng)用選定的設(shè)計(jì)策略�,以確保轉(zhuǎn)換器的強(qiáng)固性和良好的瞬態(tài)響應(yīng)。

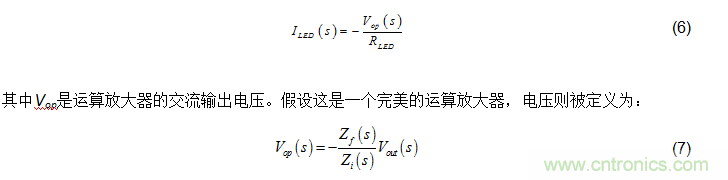

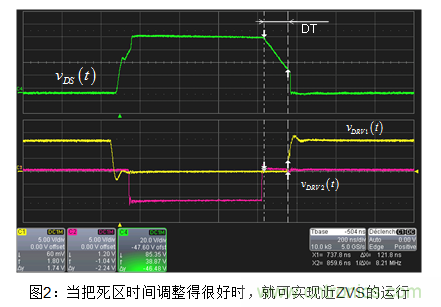

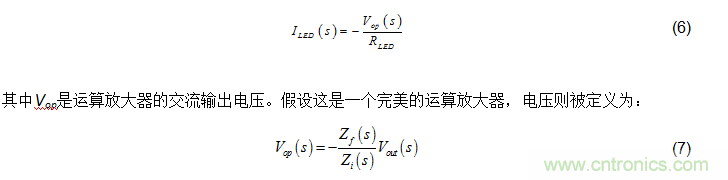

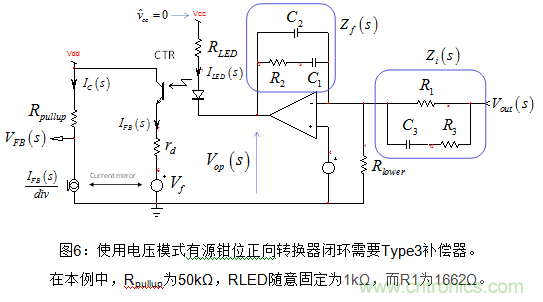

圖6表示含一個(gè)Type3補(bǔ)償器的典型架構(gòu),Type3補(bǔ)償器采用光耦合器隔離。該光耦合器本身受電流傳輸比(CTR)和極點(diǎn)的影響,極點(diǎn)的位置取決于負(fù)載電阻�。在本應(yīng)用中,分流調(diào)節(jié)反饋輸入讀取光耦合器電流�。負(fù)載電阻是rd且相當(dāng)小����,這意味著我們必須描述一個(gè)相當(dāng)高頻率的光耦合器極點(diǎn)���,以便之后中和它參考文獻(xiàn)[7]�。這里注意,LED連接到二次側(cè)的一個(gè)安靜的Vcc點(diǎn)(或輔助電壓Vaux)�����,與Vout完全交流耦合。需要注意這一點(diǎn)����,否則會(huì)產(chǎn)生快速的通道�����,使補(bǔ)償器參考文獻(xiàn)[7]的頻率響應(yīng)失真��。LED中的交流電流(忽略其動(dòng)態(tài)電阻)由下式給出:

Zf和Zi 是圖6中所圈部分的阻抗��。從這兩個(gè)網(wǎng)絡(luò)中�,我們可用快速分析電路技術(shù)參考文獻(xiàn)[8]來(lái)推斷我們想要的傳遞函數(shù)零點(diǎn)的位置���。在Vout有激勵(lì)的情況下��,需要怎樣的Zf和Zi 阻抗組合��,才能使輸出VFB為零���?

有兩個(gè)條件:

1. 當(dāng)Vout在sz處調(diào)諧時(shí)��,Zi幅值無(wú)窮大��,則VFB(sz) = 0 V。Zi由分子和分母D(s)組成��。當(dāng)D(sz) = 0時(shí)��,這個(gè)阻抗無(wú)窮大����。因此���,這個(gè)一階網(wǎng)絡(luò)的極點(diǎn)是我們想要的零點(diǎn)�。影響Zi的時(shí)間常數(shù)是通過(guò)暫時(shí)斷開(kāi)C3和“觀(guān)察”通過(guò)其連接端子提供的電阻來(lái)獲得的����。在我們的思維中����,時(shí)間常數(shù)是�����,網(wǎng)絡(luò)極點(diǎn)或傳遞函數(shù)零點(diǎn)就僅是�。

2. 當(dāng)R2和C1串聯(lián)構(gòu)成變換短路時(shí)����,輸出也為零����。這個(gè)阻抗被定義為。您可以通過(guò)得到零點(diǎn)����,從而定義了第二個(gè)零點(diǎn)位置在��。接下來(lái)���,我們可根據(jù)公式更新公式(7)。

推薦閱讀: