【導(dǎo)讀】本人結(jié)合自己在軍隊參與的電磁兼容設(shè)計工作實踐,對印制電路板的電磁兼容性設(shè)計進行了一下小結(jié),希望對印制電路板的設(shè)計有所作用。

本人結(jié)合自己在軍隊參與的電磁兼容設(shè)計工作實踐,空軍系統(tǒng)關(guān)于電子對抗進行的兩次培訓(xùn)(雷達系統(tǒng)防雷、電子信息防泄露)及入司后參與706所楊繼深主講的EMC培訓(xùn)、701所周開基主講的EMC培訓(xùn)、自己在地方電磁兼容實驗室參與EMC整改的工作體驗、特別是國際IEEE委員發(fā)表的關(guān)于EMC有關(guān)文章、與地方同行的交流體會,并結(jié)合公司的實驗情況,對印制電路板的電磁兼容性設(shè)計進行了一下小結(jié),希望對印制電路板的設(shè)計有所作用。

需要提醒注意的是:總結(jié)中只是提供了一些最基礎(chǔ)的結(jié)論,對具體頻率信號的走線長度計算、應(yīng)考慮的諧波頻率、波長、電路板級屏蔽、屏蔽體腔的設(shè)計、屏蔽體孔徑的大小、數(shù)目、進出導(dǎo)線的處理、截止導(dǎo)波管直徑、長度的計算及靜電防護,雷電防護等知識沒有進行描述。或許有些結(jié)論不一定正確,還需各位指正,本人將不勝感謝。

一、元器件布局

印刷電路板進行EMC設(shè)計時,首先要考慮布局,PCB工程師必須和結(jié)構(gòu)工程師、EMC工程師一起協(xié)調(diào)進行,做到兩者兼顧,才能達到事半倍。

首先要考慮印刷電路板的結(jié)構(gòu)尺寸大小,考慮如何對器件進行布置。如果器件分布很散,器件之間的傳輸線可能會很長,印制線路長,阻抗增加,抗噪聲能力下降,成本也會增加。如果器件分布過于集中,則散熱不好,且鄰近線條易受耦合、串擾。因此根據(jù)電路的功能單元,對電路的全部元器件進行總體布局。同時考慮到電磁兼容性、熱分布、敏感器件和非敏感器件、I/O接口、復(fù)位電路、時鐘系統(tǒng)等因素。

一般來說,整體布局時應(yīng)遵守以下基本原則:

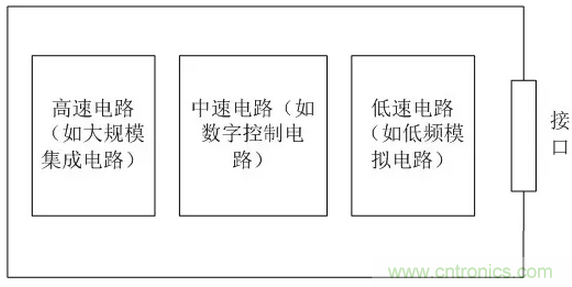

1、當線路板上同時存在高、中、低速電路時,應(yīng)該按邏輯速度分割:布置快速、中速和低速邏輯電路時,高速的器件(快邏輯、時鐘振蕩器等) 應(yīng)安放在靠近連接器范圍內(nèi),減少天線效應(yīng)、低速邏輯和存儲器,應(yīng)安放在遠離連接器范圍內(nèi)。這樣對共阻抗耦合、輻射和交擾的減小都是有利的。

2、在單面板或雙面板中,如果電源線走線很長,應(yīng)每隔3000mil對地加去耦合電容,電容取值為10uF+1000pF,濾除電源線上高頻噪聲。

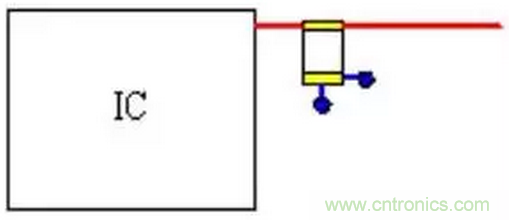

3、在單面板和雙面板中,濾波電容的走線應(yīng)先經(jīng)濾波電容濾波,再到器件管腳,使電源電壓先經(jīng)過濾波再給IC供電,并且IC回饋給電源的噪聲也會被電容先濾掉。至于去耦電容安放位置要根據(jù)實際情況來定,并不是絕對放在電源正極處,也可能放在電源負極處,原則上保證接地阻抗最小。

4、時鐘線、總線、射頻線等強輻射信號線遠離接口外出信號線至少1000mil,避免強輻射信號線上的干擾耦合到外出信號線上向外輻射,晶體、晶振、繼電器、開關(guān)電源等均為強輻射器件布局時應(yīng)著重考慮。

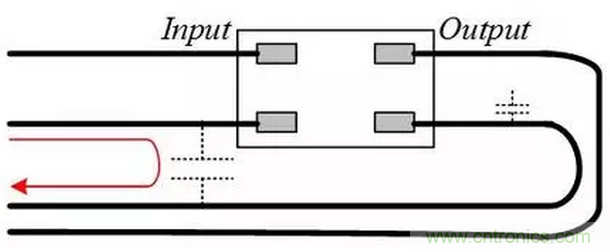

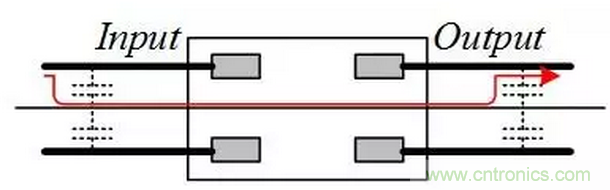

5、濾波器(濾波電路)的輸入、輸出信號線不能相互平行、交叉走線,避免濾波前后的走線直接噪聲耦合。

6、對于始端串聯(lián)匹配電阻,應(yīng)靠近其信號輸出端放置,即驅(qū)動源放置。

7、為IC濾波的各濾波電容應(yīng)盡可能靠近芯片的供電管腳放置,減少高頻回路面積,從而減少輻射。

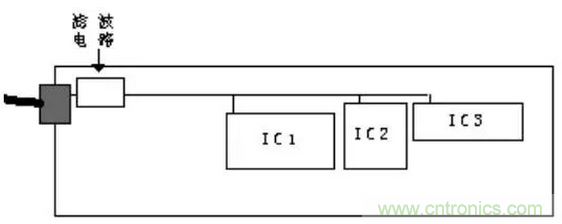

8、在PCB板上,接口電路的濾波、防護以及隔離器件應(yīng)該靠近接口放置,并且遵循先防護后濾波的原則。

9、線路板電源輸入口的濾波電路應(yīng)靠近接口放置。

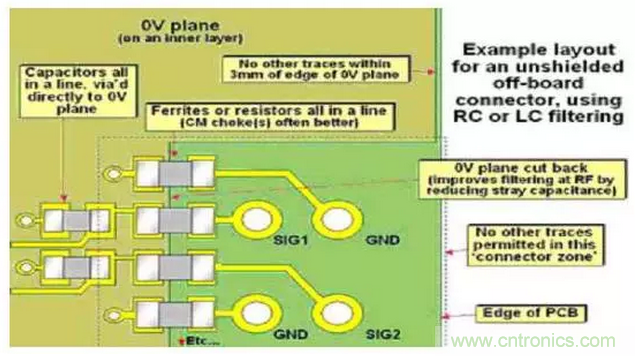

10、當接口電路采用隔離方式進行濾波設(shè)計時,其RC、LC電路應(yīng)采用如下布局,且隔離區(qū)其他層不允許有其他走線。

11、靠近PCB板邊緣4mm以內(nèi)不允許放置元器件。

12、按照電路信號的流向安排各個功能電路單元的位置,使布局便于信號流通,并使信號盡可能保持一致的方向,信號走線最短、不產(chǎn)生回流。

13、以每個功能電路的核心元件為中心,圍繞它來進行布局。元器件應(yīng)均勻、整齊、緊湊地排列在PCB上,盡量減少和縮短各元器件之間的引線和連線。

14、高頻工作的電路,要考慮元器件之間的分布參數(shù)。一般電路應(yīng)盡可能使元器件同一方向排列。

15、盡可能縮短高頻元器件之間的參數(shù),減少它們的分布參數(shù)和相互間的電磁干擾。易受干擾的器件不要相互挨得太近,輸入和輸出元件應(yīng)盡可能遠離。

16、元器件的位置應(yīng)按電源電壓、數(shù)字及模擬電路、速度快慢、電流大小等進行分組,以免相互干擾。根據(jù)元器件的位置可以確定印制板連接器各個引腳的安排。所有連接器應(yīng)安排在印制板的一側(cè),盡量避免從兩側(cè)引出電纜,減少共模輻射。

17、高頻濾波電容必須放在每個IC電源的引腳附近,減少對地回路,且要求每個電源引腳放一個高頻小電容。

18、存在較大電流變化的單元電路或器件(如電源模塊的I/O,風(fēng)扇及繼電器)附近應(yīng)放置儲能電容和高頻濾波電容。

二、印制板布線

在印制板布線時,應(yīng)先確定元器件在板上的位置,然后布置地線、電源線,再安排高速信號線,最后考慮低速信號線。應(yīng)先布地線,這條規(guī)則很重要,地線最好布成網(wǎng)狀布置。

1、電源線:在考慮安全條件下,電源線應(yīng)盡可能靠近地線,以減小差模輻射的環(huán)面積,也有助于減小電路的交擾。

2、時鐘線、信號線和地線的位置:信號線與地線距離應(yīng)較近,形成的環(huán)面積較小,時鐘線兩邊應(yīng)盡可能進行包地線處理,防止時鐘信號對其他信號的串擾,且包地線要可能多的打地過孔與地平面相連,減少接地阻抗,防止地線成為一個發(fā)射天線。

◇時鐘線包地處理

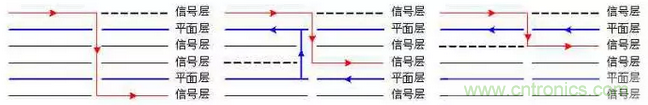

3、時鐘線和信號線盡量不要換層走線,如確因?qū)嶋H情況需換層時,在走線過孔處,需打地過孔。

◇時鐘線過孔處、信號線過孔處打地過孔

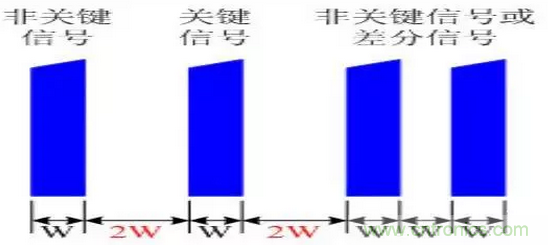

4、時鐘線、總線、射頻線等關(guān)鍵信號走線和其他同層平行走線應(yīng)滿足3W原則。

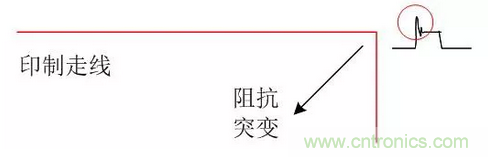

5、應(yīng)避免印制電路板導(dǎo)線的不連續(xù)性:◇跡線寬度不要突變 ◇導(dǎo)線不要突然拐角,信號走線避免“毛剌”、“銳角”、“直角”、“寬度不一致”等情況。

◇導(dǎo)線不要突然拐角

◇跡線寬度不要突變

6、輸入輸出線應(yīng)盡可能避免相鄰長距離的平等,減少輸入輸出間的串擾(差分線除外)。

7、電路板上的濾波器(濾波電路)下方不要有其他無關(guān)信號走線。

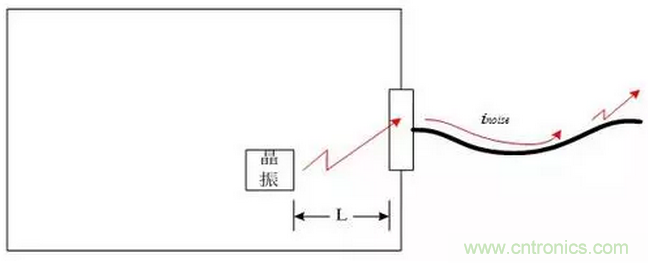

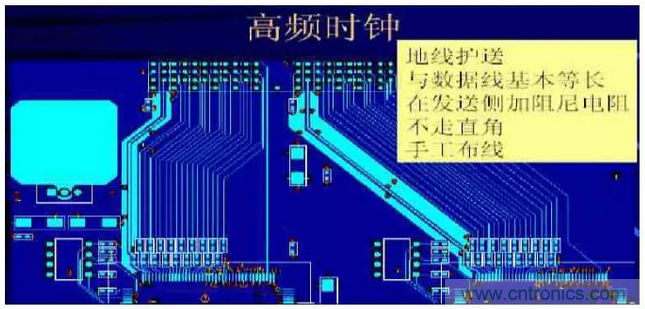

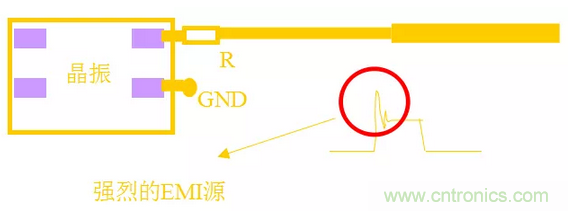

8、晶振走線盡可能靠近IC,且在時鐘線兩邊進行包地處理,時鐘接地腳與CPU接地腳應(yīng)同層直接靠近連接,減少晶振接地回路。時鐘線的線寬至少10mil,護送地線的線寬至少20 mil。時鐘晶振下最好露出地銅皮,增加電容耦合。

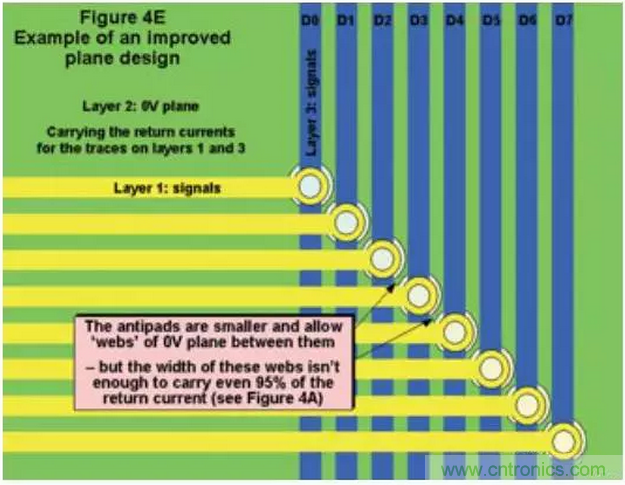

9、關(guān)鍵信號線(如時鐘線、總線、接口信號線、很射頻線、復(fù)位線、片選線)一般都是強輻射源或敏感信號線,盡可能靠近地平面布線,使其信號回路面積減少,減少其輻射強度或提高抗干擾能力。

10、高頻信號線要遠離時鐘或晶振走線,如時鐘線和高速信號線盡量不要平行走線,確因?qū)嶋H情況需平行走線,應(yīng)用地線隔開。

11、關(guān)鍵信號線距參考地平面邊沿≥3H(H為線距離參考平面的高度),特別是電源走線

12、模擬信號的高低電平信號線要分別走在地層兩側(cè)或電源兩側(cè)。

13、差分信號線應(yīng)同層、等長、并行走線,保護阻抗一致,差分線間不應(yīng)有其他走線。當確因?qū)嶋H情況要打過孔時,應(yīng)同時打過孔,且不能相距太遠。

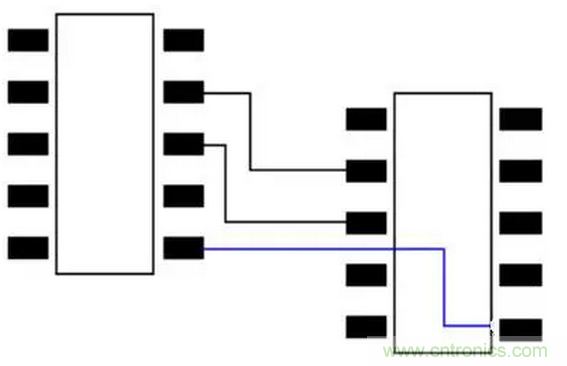

14、關(guān)鍵信號線走線不要跨分區(qū)走線,如一定要跨分區(qū)走線,則在走線附近采用橋接方式,使信號形成完整回路。

15、布線時應(yīng)把回流面積最小化作為最高原則

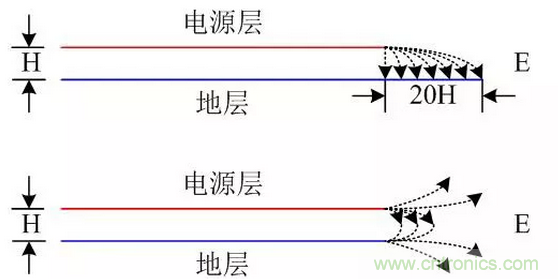

16、電源平面應(yīng)相對于其相鄰地平面內(nèi)縮20H,當因結(jié)構(gòu)限制時,也應(yīng)保證5H

17、信號線和地址線的走線應(yīng)避免形成地排或地溝

三、電源的EMC設(shè)計

電源方面的EMC設(shè)計不僅僅包括開關(guān)電源的EMC設(shè)計,還包括數(shù)字電路、模擬電路方面的電源EMC設(shè)計。

開關(guān)電源方面的EMC設(shè)計主要包括電源前端共模濾波器、差模濾波器設(shè)計、開關(guān)變壓器緩沖回路的參數(shù)設(shè)計、開關(guān)管和快速二極管的吸收回路的設(shè)計、開關(guān)變壓器的屏蔽設(shè)計等項目。主要根據(jù)具體產(chǎn)品來進行具體設(shè)計。

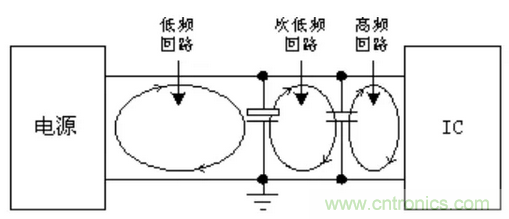

模擬電路和數(shù)字電路電源部分的EMC設(shè)計是非常重要的一個部分,主要包括BULK去耦電容的選擇、IC去耦電容的選擇、整體去耦電容的選擇、磁珠的選擇、濾波方式的選擇等。

電源開關(guān)的交流回路、整流器交流回路包含高幅梯形電流,這些電流中諧波含量成分很高,其頻率遠大于開關(guān)基頻,峰值幅值可高達持續(xù)輸入/輸出直流電流幅度的五倍,過渡時間通常為50ns,這兩個回路最容易產(chǎn)生電磁干擾。因此應(yīng)優(yōu)先布好這些回路,每個回路中的三種主要器件:濾波電容、電源開關(guān)或整流器、電感或變壓器應(yīng)彼此相鄰地進行設(shè)置,調(diào)整元器件位置使它們之間的電流回路路徑盡可能的短。

開關(guān)電源的布線規(guī)則為:

1、所有傳送交流信號的引線要盡可能的短而寬。

2、盡可能地減少環(huán)路面積,以抑制開關(guān)電源的輻射干擾。

3、根據(jù)印刷線路板電流的大小,盡可能地加粗電源線寬度,減少環(huán)路電阻。

4、電源線、地線的走線與電流的方向一致,增加抗噪聲能力。

開關(guān)電源的地線設(shè)計規(guī)則為:

1、通常選擇單點接地:輸入濾波電容公共端應(yīng)是其它的接地點耦合到大電流的交流地的唯一連接點,同一級電路的接地點應(yīng)盡量靠近,且本級電路的濾波電容應(yīng)接在該級接地點上,主要是考慮電路各部分回流到地的電流是變化的。

2、盡量加粗接地線:地線寬度最好是地線 寬度比電源線寬,如有可能接地線寬度大于3mm,也可以用大面積銅層作為地線用,在印刷板上把沒有用上的地方都與地相連,作為地線。

3、控制芯片的接地設(shè)計:功率地與信號地最終歸為一個地,但功率地與電源地要形成回流,信號地與信號線形成回流,切不可把功率地和信號地混淆,功率地和信號地最終實現(xiàn)單點接地。IC控制地最好在其他交流電路環(huán)路都布置好后再放置,控制地要通過一特定的點連接到主電源地,減少檢測部分、誤差放大器和敏感輸入端之間的連接而引入噪聲。

四、數(shù)字電路的EMC設(shè)計

數(shù)字電路的EMC設(shè)計主要包括有源器件的選擇、時鐘電路的EMC設(shè)計、數(shù)據(jù)總線和地址總線的EMC設(shè)計、阻抗匹配和接地反彈的設(shè)計、總線驅(qū)動器的濾波設(shè)計等。

首先應(yīng)注意器件的選擇:應(yīng)優(yōu)先選用器件上升沿平滑的器件。高速數(shù)字器件的布線易產(chǎn)生振鈴。該振鈴?fù)ǔ1憩F(xiàn)為諧波發(fā)射。通常的解決方法是在高速數(shù)據(jù)線上串一個阻尼電阻或串一個磁珠。

90%的EMI是由于10%的關(guān)鍵電路引起的,因此布線時要特別關(guān)注關(guān)鍵電路的布線。關(guān)鍵電路主要有時鐘電路、高速數(shù)據(jù)總線、地址總線、復(fù)位線、中繼線、控制線等,布線時應(yīng)優(yōu)先布好這些關(guān)鍵線路。

高速數(shù)據(jù)電路的接地設(shè)計為:一般采用多點接地,減少接地阻抗。

高速數(shù)據(jù)電路的電源設(shè)計為:

電路板入口處的電源去耦:大多數(shù)電路板的電源入口處去耦包括一個大的去耦電解電容并一到兩個小的高頻去耦電容,主要作用是為數(shù)字電路提供再充電,同時減少高頻噪聲。

器件去耦:任何鐘控器件(除微處理器外),必須在電源引腳加高速電容去耦,如果提供了多個電源和地線的管腳都必須加去耦電容。

高速數(shù)據(jù)電路的布線規(guī)則為:

1、時鐘線、信號和地線的位置:信號線與地線距離應(yīng)較近,形成的環(huán)面積較小,時鐘線兩邊應(yīng)盡可能進行包地線處理,防止時鐘信號對其他信號的串擾,且包地線要可能多的打地過孔與地平面相連,減少接地阻抗,防止地線成為一個發(fā)射天線。

2、按邏輯速度分割:當需要在電路板上布置快速、中速和低速邏輯電路時,高速的器件(快邏輯、時鐘振蕩器等) 應(yīng)安放在靠近連接器范圍內(nèi),減少天線效應(yīng)、低速邏輯和存儲器,應(yīng)安放在遠離連接器范圍內(nèi)。這樣對共阻抗耦合、輻射和交擾的減小都是有利的。

3、應(yīng)避免印制電路板導(dǎo)線的不連續(xù)性:◇跡線寬度不要突變 ◇導(dǎo)線不要突然拐角

4、輸入輸出線不要緊靠時鐘線或振 蕩器線、電源線等電磁熱線,也不要緊靠復(fù)位線、中斷線、控制線等敏感信號線,應(yīng)盡可能避免相鄰長距離的平等,減少輸入輸出間的串擾(差分線除外)。

5、信號走線避免“毛剌”、“銳角”、“直角”、“寬度不一致”等情況。

6、晶振走線盡可能靠近IC,且在時鐘線兩邊進行包地處理,時鐘接地腳與CPU接地腳應(yīng)同層直接靠近連接,減少晶振接地回路。時鐘線的線寬至少10mil,護送地線的線寬至少20 mil。

7、關(guān)鍵信號線(如時鐘線、總線、接口信號線、很射頻線、復(fù)位線、片選線)一般都是強輻射源或敏感信號線,盡可能靠近地平面布線,使其信號回路面積減少,減少其輻射強度或提高抗干擾能力。

8、高頻信號線要遠離時鐘或晶振走線,如時鐘線和高速信號線盡量不要平等走線,確因?qū)嶋H情況需平行走線,應(yīng)用地線隔開。

9、時鐘線和信號線盡量不要換層走線,如確順實際情況需換層時,在走線過孔處,需打地過孔。

10、差分信號線應(yīng)同層、等長、并行走線,保護阻抗一致,差分線間不應(yīng)有其他走線。

11、關(guān)鍵信號線走線不要跨分區(qū)走線,如一定要跨分區(qū)走線,則在走線附近采用橋接方式,使信號形成完整回路。

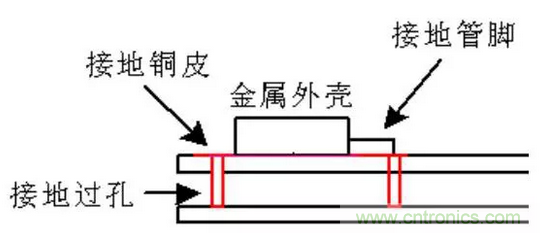

12、金屬外殼接地的器件如晶振,應(yīng)在其投影面的頂層上鋪接地鈾皮,目的是通過金屬外殼與接地銅皮之間的分布電容來抑制其對外輻射和提高抗干擾能力。

五、模擬電路的EMC設(shè)計

模擬電路的EMC設(shè)計主要考慮EMS,因為模擬器件對產(chǎn)品的抗干擾非常敏感,因此模擬電路主要是在必要的端口加防護器件,抑制外來的電子干擾。常用的防護器件有濾波器件、磁珠、瞬態(tài)抑制二極管、共模扼流圈、隔離變壓器等。

模擬電路工作在低頻狀態(tài)下,任何mv級的電壓變化都會引起工作狀態(tài)的改變,因此模擬電路的EMC設(shè)計主要考慮EMS,對這些靈敏電路單點接地是最好的接地方式,接地的主要目的是防止來自其他噪聲元件如數(shù)字電路、開關(guān)電源、繼電器的大接地電流爭用敏感的模擬地線。接地環(huán)路必須避開一切敏感的低頻模擬電路。

對數(shù)?;旌系碾娐?,其接地方式最好不要進行地分割?,F(xiàn)在芯片發(fā)展迅速,大部分芯片中數(shù)字電路和模擬電路皆有,對于這種情況,最好將數(shù)字地與模擬地混合,而在布局上將模擬部分的外圍器件集中放置,遠離干擾源。

六、接口電路的EMC設(shè)計

接口電路的EMC設(shè)計包括接口電路的濾波電路設(shè)計和接口電路的防護設(shè)計。

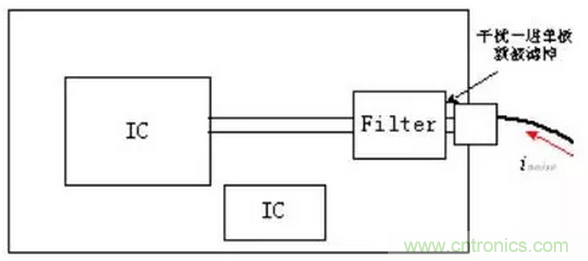

接口電路濾波設(shè)計的目的是減小系統(tǒng)通過接口及電纜對外產(chǎn)生的輻射,抑制外界輻射和傳導(dǎo)噪聲對整機系統(tǒng)的干擾;

接口防護電路設(shè)計的目的是使電路可以承受一定的過電壓、過電流的沖擊。

接口濾波電路和防護電路設(shè)計應(yīng)遵循下面的基本設(shè)計原則:

1、濾波和防護電路對接口信號質(zhì)量的影響滿足要求。

2、濾波和防護電路應(yīng)根據(jù)實際需要設(shè)計,不能簡單拷貝。

3、需要同時進行濾波電路和防護電路時,應(yīng)保證先防護后濾波的原則。

4、接口芯片,包括相應(yīng)的濾波、防護、隔離器件等,應(yīng)盡可能沿信號流方向成直線放置在接口連接器處。

5、接口信號的濾波、防護、隔離器件等盡可能靠近接口連接器處,相應(yīng)的信號連接線必須盡可能短(符合工藝要求條件下的最短距離)。

6、接口變壓器要就近放置在連接器附近,通常在對應(yīng)接口連接器3cm以內(nèi)。

7、模擬信號接口和數(shù)字信號接口、低速邏輯信號接口和高速邏輯信號接口等(以敏感和干擾發(fā)射程度來區(qū)分),它們之間要間隔一定距離放置。當連接器之間存在相互干擾的可能時,必須采取隔離、屏蔽等措施。

8、同一接口連接器里存在不同類型的信號時,必須用地針隔離這些信號,特別是對于一些比較敏感的信號。

9、接口信號線走線的線寬應(yīng)始終一致。對于高速信號線,如果走線有需要彎曲的地方,則應(yīng)采用圓弧平滑地彎曲走線。

10、禁止在差分線和信號回線之間走其他信號線,差分對線對應(yīng)的部份應(yīng)平行、就近、同層走線,且走線的長度盡可能一致。

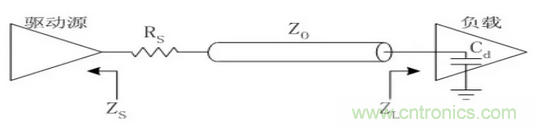

11、當接口信號線較長(從驅(qū)動、接收器到接口連接器超過2.5cm),應(yīng)按傳輸線布線方法,使走線滿足規(guī)定的特性阻抗。

12、所有的信號走線不能跨平面走線,除非已經(jīng)過隔離濾波器。

13、接口信號連接器建議選用帶屏蔽外殼的連接器,尤其是高頻信號連接器。

14、連接器的金屬外殼應(yīng)與機殼保持良好的電連續(xù)性,對于能夠360度環(huán)繞的連接器,則必須360度環(huán)繞連接,而且通常連接阻抗要小于1mΩ。

15、對于不能進行360度環(huán)繞連接的連接器,則建議采用外殼四周有向上簧片的連接器,而且簧片必須有足夠的尺寸和性能(彈性),以保持與機殼間有良好的電連接。

16、濾波連接器對產(chǎn)品EMC性能往往有很大的幫助,但其成本比較高,通常在采用板內(nèi)濾波、電纜屏蔽等方法能解決問題的情況下,就不采用濾波連接器。

17、屏蔽線的屏蔽層要盡可能與接插件外殼保持360度的連接。對于做不到這一點的接口,通常有其他對應(yīng)的措施,來保證接口的EMC性能。

18、接口信號線和接口芯片,必須遵守供應(yīng)廠商或標準的要求進行阻抗匹配、濾波、隔離、防護等。

七、結(jié)構(gòu)的EMC設(shè)計

結(jié)構(gòu)EMC設(shè)計包括底板、機殼和設(shè)備內(nèi)部走線幾種情形。

底板和機殼是為控制設(shè)備或功能單元中無用信號通路提供屏蔽的最有效方法,因此電子產(chǎn)品的底板和機殼最好采用金屬結(jié)構(gòu)或采用內(nèi)部鍍金屬的塑料結(jié)構(gòu)。

結(jié)構(gòu)縫隙必須盡量減少結(jié)構(gòu)的不連續(xù)性,以便控制來自底板和機殼進出的泄漏輻射。提高縫隙屏蔽效果的結(jié)構(gòu)措施包括增加縫隙深度、減少縫隙長度,在接合處加導(dǎo)電襯墊,在接縫處涂導(dǎo)電涂料,縮短螺釘間距等措施。

結(jié)構(gòu)開口方向應(yīng)與磁力線方向一致,如果垂直磁力線方向則會產(chǎn)生切斷磁力線,使磁阻增加,屏蔽效果變差。

設(shè)備內(nèi)部走線混亂則對非屏蔽的電子設(shè)備來講,設(shè)計的屏蔽、濾波電路、接地措施應(yīng)不會起到應(yīng)有的作用。內(nèi)部走線太亂,不僅傳輸高、低電平信號之間相互騷擾,也給后期采用屏蔽、濾波、接地等補救措施帶來不便。

設(shè)備內(nèi)部走線的基本原則為:

1、機箱內(nèi)各種裸露走線要盡量短。

2、傳輸不同電平信號的導(dǎo)線分組捆扎,數(shù)字電路和模擬電路信號線應(yīng)分組捆扎,并保持適當距離,減少導(dǎo)線相互影響。

3、對產(chǎn)品中用來傳遞信號的扁平電纜,應(yīng)采用地-信號-地-信號-地排列的方式,這樣可以有效抑制騷擾,增強其抗干擾能力。

4、將低頻進線和回線絞合在一起,形成雙絞線,減少電磁騷擾。

5、對確定的輻射騷擾較大的導(dǎo)線要加屏蔽措施。

6、屏蔽電纜進出屏蔽體必須保證屏蔽層與屏蔽體之間可靠搭接,一般要求360°環(huán)接,并提供足夠低的搭接阻抗。

7、非屏蔽電纜原則上禁止直接從屏蔽體中出線。特殊情況下允許直接出線,但是要求屏蔽體內(nèi)側(cè)(或者外側(cè))電纜的長度不得越過80mm,注意這個尺寸包括PCB上面的走線,如果有濾波電路,指濾波電路與屏蔽體之間的電纜長度。

8、非屏蔽電纜還有一種特殊處理措施就是:用金屬絲網(wǎng)將非屏蔽電纜在屏蔽體內(nèi)部分纏繞變成局部的屏蔽電纜,然后按照屏蔽電纜的方式進行處理。需要注意的是這種方法可能存在工藝性差,作用有限等缺陷。

9、屏蔽電纜還有一種特殊應(yīng)用場合,有時系統(tǒng)規(guī)定其屏蔽層不得與屏蔽體(實際上就是PGND)連接,典型的例子是同軸電纜。這時的屏蔽電纜可以按照非屏蔽電纜處理(在屏蔽體一側(cè)的長度不得超過80mm),或者采用雙層屏蔽電纜。

八、接地設(shè)計

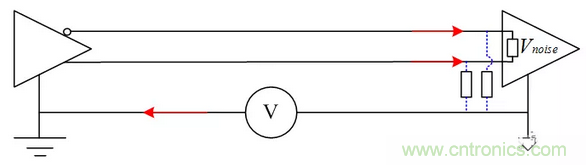

接地首先必須采用低阻抗設(shè)計,相對于其他電氣的連接線,接地設(shè)計中要求接地線盡量粗、短,特別是在印制板設(shè)計上通常采用大面積連接。在接地設(shè)計中,地環(huán)路問題也是要重點考慮的問題,但地環(huán)回路一般出現(xiàn)在低頻場合,大多數(shù)情況下采取低阻抗接地通路的設(shè)計方案來解決此類問題。

地環(huán)路在高速電路設(shè)計中不必要太多關(guān)心,因為這時很難去掉地環(huán)路,需要考慮的是如何降低地線的阻抗,因此數(shù)字電路常采用多點接地。但對低頻模擬電路及小信號電路,地環(huán)路問題又是比較重要的,必須減少地環(huán)路面積,抑制地環(huán)路對低頻模擬電路及小信號電路的騷擾。

在數(shù)字電路里,其工作特性不取決于電路中的工作頻率,而是取決于該電路工作脈沖的上升沿和下降沿,因此數(shù)字電路產(chǎn)生的諧波頻帶非常寬,且幅度大,因此常采用多點接地減少接地阻抗。

由于現(xiàn)在IC器件往往是模擬和數(shù)字電路同時存在,因此在設(shè)計中往往采用單點和多點混合接地的形式。在數(shù)字電路中,采用多點接地或大面積接地方式;在模擬電路,采用單接地。

實際上,在電路板設(shè)計中,上述接地方法可以很好的實現(xiàn);但是在系統(tǒng)設(shè)計的接地設(shè)計中,由于要考慮信號傳輸質(zhì)量的好壞,另外系統(tǒng)對EMS、安全設(shè)計以及相應(yīng)的EMC性能要求使接地變得更為復(fù)雜。

單點和多點接地是設(shè)計人員關(guān)心的一個問題。單點接地適合小信號和模擬電路,多點接地適合高頻電路設(shè)計。因為在小信號和模擬電路設(shè)計中,mV級的干擾就可能會影響電路的性能,單點接地可以控制電流的路徑,避免地環(huán)路的形成。而在高頻電路中,引線電感和寄生電容都可能是破壞單點接地因素,從而構(gòu)成大的接地阻抗和隱性的地環(huán)路。因此不少工程師通常將數(shù)字地與模擬地分開,但由于印制板的限制又不能完全遵循EMC設(shè)計原則,導(dǎo)致印制板設(shè)計的失敗。現(xiàn)代 科學(xué)技術(shù)的飛速發(fā)展,集成芯片的發(fā)展速度非??欤粋€芯片中往往包括數(shù)字電路和模擬電路,如果將數(shù)字地和模擬地完全分開,再有經(jīng)驗的PCB工程師估計也難實現(xiàn)。為了證明數(shù)字地與模擬否能混合,國際IEEE委員Tony Waldron在對某大型影劇院進行EMC整改時,將兩個地混合為一個完整的地,徹底解決了導(dǎo)線長達20多米的麥克風(fēng)尖叫(hum)問題,當電源合上時整個影劇院悄無聲息,在場的工程師簡直不相信自己的耳朵。

本文轉(zhuǎn)載自:道客巴巴