【導讀】目前快充市場可謂“百花齊放”,各種快充協(xié)議讓人眼花繚亂。高通QC2.0/3.0、MTKPE 1.0/2.0和USB PD高壓快充占據市場大壁江山;華為Super Charger、OPPO VOOC、努比亞NeoCharger、高通QC 4.0以及MTK PE3.0低壓直充也發(fā)展迅速;魅族、小米、OPPO以及錘子等手機品牌也正在研究更大功率的電荷泵高壓直充充電技術。

快充業(yè)界尚未形成統(tǒng)一協(xié)議,各種協(xié)議互不兼容,用戶使用起來諸多不便。將各種快充協(xié)議放到一個芯片內做一個全協(xié)議兼容的方案,可以一定程度上解決兼容性難題。

易能推出的EDP3032,是為全協(xié)議快充適配器設計的一顆 SOC 芯片,內部集成 QC2.0、QC3.0、PE1.0、AFC、FCP、SCP、 VOOC、BC1.2 DCP、APPLE 2.4A 快充協(xié)議;支持輸出電壓自適應,還集成了輸出欠壓、過壓、短路保護等多重安全保護功能。

如何利用易能的EDP3032芯片制作一個18W全協(xié)議兼容的快充適配器?請看下文。

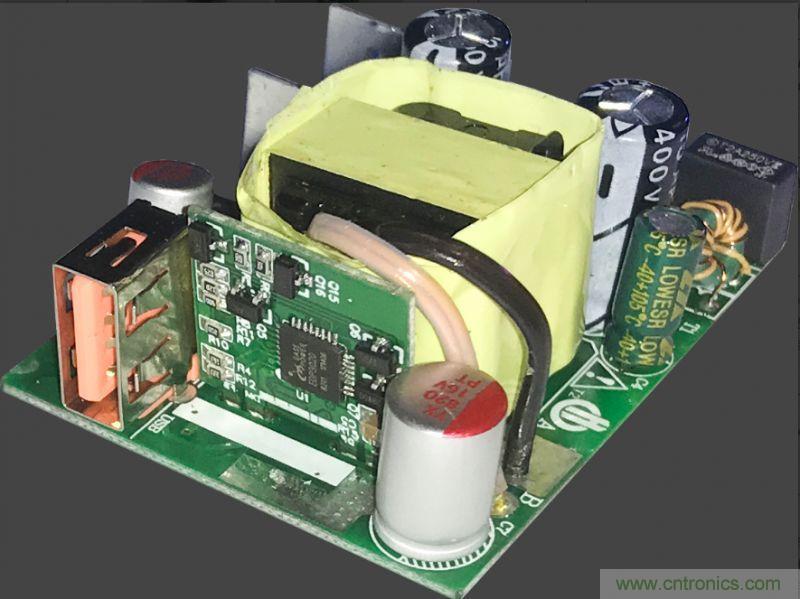

圖1: 18W全兼容適配器

1.所需要的BOM貼片清單

圖2:BOM貼片清單

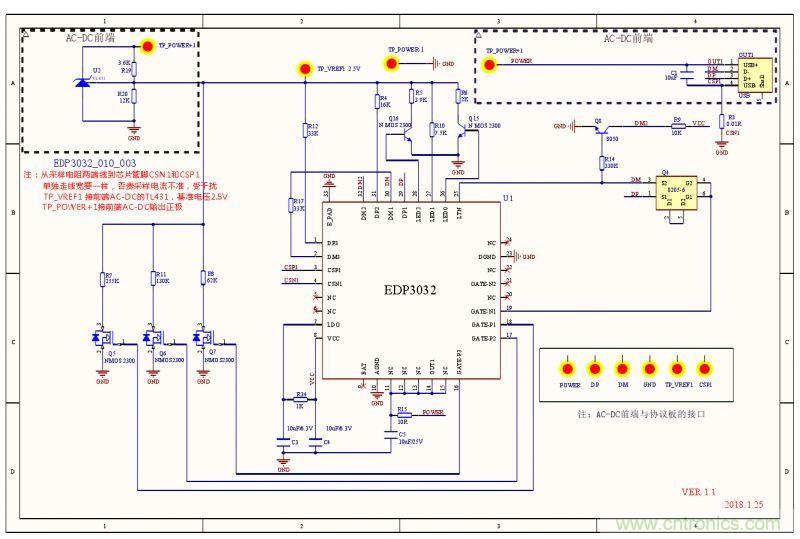

2.電路原理圖

圖3:電路原理圖

3.PCB設計

(1)IC下面需敷銅散熱,IC襯底要連接到PGND,散熱面積盡量大,襯底焊盤打通孔到PCB底層,并適當露銅皮增強散熱。

(2)LDO18腳的10uF電容要靠近芯片管腳;AGND用單點接連的方式回到PGND。

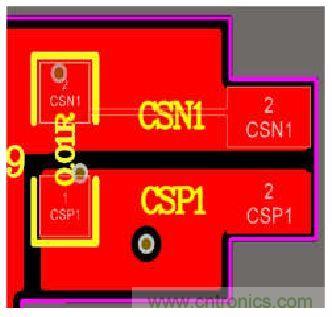

(3)采樣電阻CSP,CSN端Layout應遵循如下規(guī)則:

① CSP,CSN走線要盡量避開干擾源器件比如電感、環(huán)路MOS、Vout等;

② CSP,CSN走線盡量在同一層,減少打孔的情況;

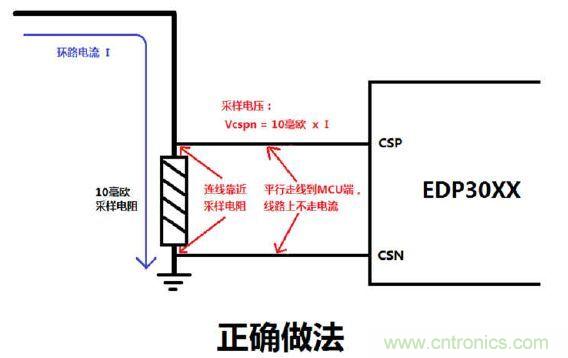

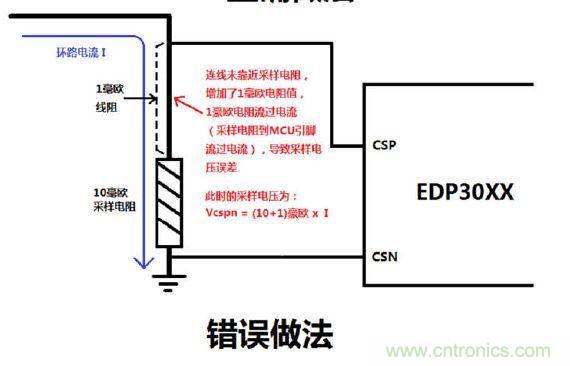

③ CSP,CSN兩條線都必須靠近采樣電阻,從采樣電阻兩端平行走線接入芯片且盡量靠近芯片,采樣電阻到芯片端之間的連線不得過電流。同理,CSN也不可以直接和PGND相連。

圖4:焊盤

圖5:正確做法

圖6:錯誤做法

④ 大電流通路(升降壓環(huán)路部分電路:BAT–電感–MOS--VOUT):盡量走在同一層,而且盡量粗短,同時地的面積也盡量增大且要完整,從而增加散熱,減小紋波并降低EMC干擾。

⑤ USB口外殼不可以直接接GND。由于某些USB線負極與外殼相連,而采樣電阻需要接在接口負極與GND中間,若兩者相連會導致采樣電阻短路。

⑥ 為保證散熱,EMC等性能最佳,推薦使用四層板。

推薦閱讀: