【導讀】PI(Power Integrity),即電源完整性,以前隸屬于信號完整性分析專題,但是因為PI足夠復雜和關鍵,現在已經把其單獨拿出來作為一個專題去研究??焖俣鴾蚀_的仿真電源完整性至今仍然是一個待突破的難題。

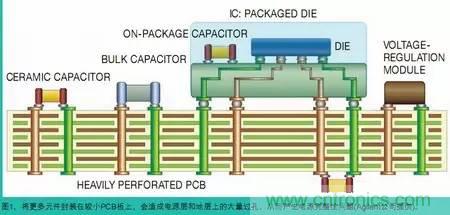

對于高速數字電路和系統(tǒng),PI的研究對象是電源分配網絡PDN(Power Distribution Network)。以筆記本電腦為例,AC到DC電源適配器供給計算機主板的是一個約16V的直流電源,主板上的電源分配網絡要把這個16V直流電源變成各種電壓的直流電源(如:+-5V, +1.5V, +1.8V,+1.2V等等),給CPU供電,給各個芯片供電。CPU和IC用電量很大,而且是動態(tài)耗電的,瞬時電流可能很大,也可能很小,但是電壓必須平穩(wěn)(即紋波和噪聲必須較小),以保持CPU和IC的正常工作。這都對PDN提出了苛刻的要求。

要測量PDN性能,首先需要用示波器測試CPU和IC管腳的電源紋波和噪聲。但是要精確衡量PDN的性能,還需要測試PDN的輸出阻抗(隨頻率變化的阻抗)和PDN的傳輸阻抗(也是隨頻率變化的阻抗),就像表征一個單端口網絡或雙端口網絡一樣去表征PDN。由于現在的PDN大都是開關電源結構,還需要測量PDN或關鍵DC到DC轉換器件的環(huán)路增益。

小結一下,電源完整性的測量對象是電源分配網絡PDN。主要測量內容包括四部分:

● 紋波和噪聲的測量;

● 輸出阻抗的測量;

● 環(huán)路增益的測量;

● 濾波器件(電容/磁珠等)性能參數的測量。

電源紋波和噪聲測量

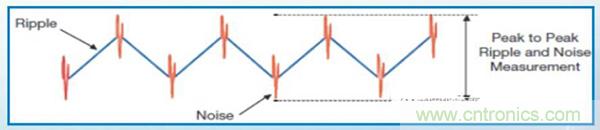

電源紋波和電源噪聲是一個比較容易混淆的概念,如下圖2所示,藍色波形為電源紋波,紅色波形為電源噪聲。電源紋波的頻率為開關頻率的基波和諧波,而噪聲的頻率成分高于紋波,是由板上芯片高速I/O的開關切換產生的瞬態(tài)電流、供電網絡的寄生電感、電源平面和地平面之間的電磁輻射等諸多因素產生的。因此,在PMU側測量電源輸出為紋波,而在SINK端(耗電芯片端,如AP、EMMC、MODEM等)測量的是電源噪聲。

今天的電子電路(比如手機、服務器等領域)的切換速度、信號擺率比以前更高,同時芯片的封裝和信號擺幅卻越來越小,對噪聲更加敏感。因此,今天的電路設計者們比以前會更關心電源噪聲的影響。實時示波器是用來進行電源噪聲測量的一種常用工具,但是如果使用方法不對可能會帶來完全錯誤的測量結果。

由于電源噪聲帶寬很寬,所以很多人會選擇示波器做電源噪聲測量。但是不能忽略的是,實時寬帶數字示波器以及其探頭都有其固有的噪聲。如果要測量的噪聲與示波器和探頭的噪聲在相同數量級,那么要進行精確測量將是非常困難的一件事情。

示波器的主要噪聲來源于2個方面:示波器本身的噪聲和探頭的噪聲。

所有的實時示波器都使用衰減器和放大器來調整垂直量程。設置衰減以后示波器本身的噪聲會被放大。比如,當不用衰減器時,示波器的基本量程是5mV/格,假設此時示波器此時的底噪聲是500uVRMS。當把量程改成50mV/格時,示波器會在輸入電路中增加一個10:1的衰減器。為了顯示正確的電壓信號,示波器最后顯示時會把信號再放大10倍顯示。因此此時示波器的底噪聲看起來就有5mVRMS了。因此,測量噪聲時應盡可能使用示波器最靈敏的量程檔。但是示波器在最靈敏檔下通常不具有足夠的偏置范圍可以把被測直流電壓拉到示波器屏幕中心范圍進行測試,因此通常需要利用示波器的AC耦合功能把直流電平濾掉只測量AC成分。

現在有12bits的示波器上市,如安捷倫9000H系列示波器,其噪聲相對小的多,只有0.7v@100mv/格,所以,能夠用12bits示波器,則是最好的選擇。

基于同樣的原因,在電源測量中也應該盡量使用1:1的探頭而不是示波器標配的10:1的探頭。否則示波器的噪聲也會被放大。

探頭帶來的噪聲是在在衰減器前面耦合進來的,因此無論衰減比設置多少,探頭貢獻的噪聲都是一定的。但是,在某些不正確的使用方法下,探頭可能會帶來額外的噪聲,一個典型的例子就是使用長地線。為了方便測試,示波器的的無源探頭通常會使用15cm左右的鱷魚夾形式的長地線,但是這對于電源紋波的測試卻是不適用的,特別是板上存在開關電源的場合。由于開關電源的切換會在空間產生大量的電磁輻射,而示波器探頭的長地線又恰恰相當于一個天線,所以會從空間把大的電磁干擾引入測量電路。一個簡單的驗證方法就是把地線和探頭前端接在一起,靠近被測電路(不直接接觸)就可能在示波器上看到比較大的開關噪聲。因此測量過程中應該使用盡可能短的地線。

現在很多被測件要求測量出峰峰值為幾毫伏的紋波和噪聲,比如有些10Gbps以上的SerDes要求3mv峰峰值的電源紋波和噪聲。這時候最好用同軸電纜來進行測量,雖然同軸電纜的阻抗只有50歐姆,但是對于毫偶級別的被測電源來說,負載影響很小,測試精度非常高。

但是用同軸電纜,示波器設置為50歐姆輸入阻抗時,示波器都是DC耦合,這時候可有兩種處理手段:

其一,在被測的電源的接觸點放置電容。電容一邊連接被測件,一邊接觸同軸電纜。一般電容用0.1uF即可。

其二,制作電源測試探頭。最好做一個小的PCB,PCB兩端放置SMA接頭,中間裸露出來,可以用來放置電容。圖3是自制探頭的示例。

最后要注意的一點是,通常電源測試都規(guī)定了某個頻率范圍內的紋波和噪聲,比如20MHz以內的,而一般示波器的帶寬都大于這個要求,因此測試時可以打開示波器的帶寬限制功能,這對于減小高頻噪聲也會有比較好的效果。

小結一下,對于電源紋波噪聲的測試,通常需要注意以下幾點:

● 盡量使用自制的電源測試探頭

● 盡量使用12bits示波器

● 盡量使用示波器最靈敏的量程檔;

● 盡量使用AC耦合功能;

● 盡量使用小衰減比的探頭;

● 探頭的接地線盡量短;

● 根據需要使用帶寬限制功能;

電源分配網絡PDN輸出阻抗的測量

要衡量PDN性能,只用示波器測試CPU和IC管腳的電源紋波和噪聲是不夠的,而且出現問題后也沒有辦法定位問題。要精確衡量PDN的性能,還需要測試PDN的輸出阻抗(隨頻率變化的阻抗)和PDN的傳輸阻抗(也是隨頻率變化的阻抗),就像表征一個單端口網絡或雙端口網絡一樣去表征PDN。這就要用到網絡分析儀工具。

用網絡分析儀去測試PDN,有兩大挑戰(zhàn):

1、PDN的輸出阻抗和傳輸阻抗是豪歐級的(一般2m歐姆左右),想準確測試,是一件比較困難的事情。

2、PDN工作時是帶直流電壓的,即帶偏置的,需要網絡分析儀有偏置測量的功能。

用網絡分析儀測試毫歐級的輸出阻抗,不能簡單的用一端口測試方法,因為阻抗太小,反射太大。這時比較好的方法是用雙端口測試方法,測試時用S21代替S11。

假設探測試電纜電感約為0,Z(DUT)遠小于Zo(VNA端口阻抗),PDN輸出阻抗的計算公式如下:

ZDUT=Z11=S21x25

用網絡分析儀測試毫歐級的輸出阻抗,也是用雙端口測試方法。

假設探測試電纜電感約為0,Z11,Z21,Z22遠小于Zo,PDN傳輸阻抗的計算公式如下:

Z21=Z12=S21x25

電路板系統(tǒng)級PDN測量

如何探測?

要進行電路板系統(tǒng)級PDN的測量,最好使用SMA連接器或半剛性SMA同軸電纜。SMA連接器中間是信號針,四周四個腳是地針,需要用鉗子把3個腳針剪掉,留下一個即可。半剛性SMA電纜則需要剪斷,露出中間的信號針,外包的屏蔽焊接短線供連接地用。

探測時,盡量不要在同一個面探測,因為電流環(huán)路產生的磁場會使得探頭之間互相耦合,產生誤差。如果只能在一面探測,請盡量使用半剛性SMA電纜自制的短針探頭探測。

如果不需要進行 kHz 級以下的測量,并且可以在連接電纜上使用磁心,我們可以用 E5061B VNA 的 S 參數端口和簡單的配置來對不加電或加電的系統(tǒng)電路板上的 PDN 阻抗進行高達 3 GHz 的測量。如果我們需要測量比較低的頻率響應,可用該儀器的增益-相位測試端口在 5 Hz 到 30 MHz 的頻率范圍內進行測量。在系統(tǒng)電路板應用方面,直流-直流轉換器的高直流環(huán)路增益在它感應線的連接點上保持著極低的低頻阻抗值。遠離感應點時,水平面電阻將使低頻值增大。這不是測量誤差,而是系統(tǒng)電路板 PDN 的實際特征。

DC-DC轉換器環(huán)路增益測量

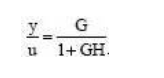

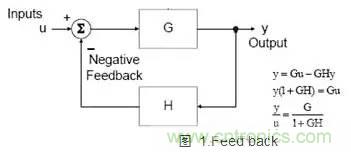

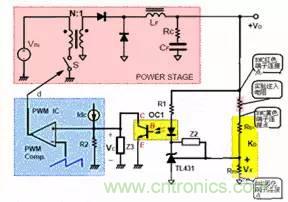

隨著電子,自控,航天,通訊,醫(yī)療器械等技術不斷向深度和廣度的發(fā)展,勢必要求為其供電的電源要有更高的穩(wěn)定性,即不僅要有好的線性調節(jié)率、負載調節(jié)率還要有快速的動態(tài)負載響應。而這些因素都和控制環(huán)路有關,控制環(huán)路一般工作在負反饋狀態(tài),稱之為電壓負反饋。如果變換器中沒有用到反饋控制環(huán)路(即下圖1中H部分),其傳遞函數一般為 其中G為輸入濾波、功率變換、整流濾波部分等因數的乘積(因為其為級聯的形式,所以本文中以總的乘積因子G來表示),可以看出輸出隨著輸入的變化而成線性的變化,但是由于整流、濾波網絡在整個時域的非線性,實際上這種變化應該是近似于線性,所以當輸入電壓改變的時候并不能很好的起到穩(wěn)壓的作用;如果反饋環(huán)路設計的不好,對于負載的瞬態(tài)改變,環(huán)路不能做出及時恰當的調整,那么輸出電壓瞬間會偏高或者偏低,甚至有可能造成電源系統(tǒng)的振蕩,對下一級構成損壞。此時能夠對環(huán)路測量就顯得很重要了,那么環(huán)路部分又是怎樣影響整個回路的呢?參考金升陽公司寬壓或者AC-DC系列產品,此時下圖表示的是反饋環(huán)路控制部分中的運放的環(huán)增益模型,其傳遞函數為

其中G:開環(huán)增益,H:反饋系數,GH:環(huán)增益(可以通過圖1中推導看出)

Feed back

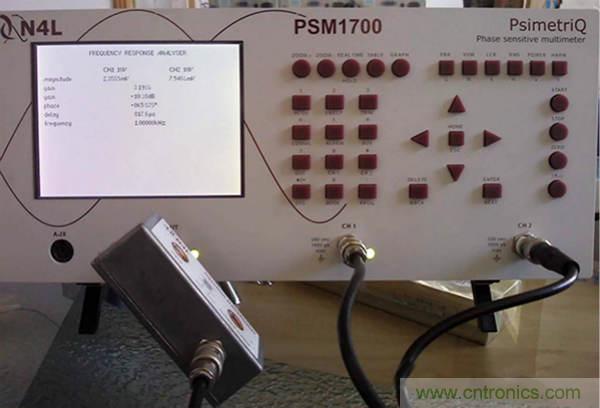

PSM1700 PSM1735 PSM2200 FRA5087 頻率響應分析儀

一、環(huán)增益穩(wěn)定的標準:

由傳遞函數

有,因為放大器的開環(huán)增益G是頻率的函數,會隨著頻率的增加而減小,同時也和放大器的相位有關,當GH= -1,則其傳遞函數的值為∞,即增益是無窮大的,可以認為任意小的輸入擾動都能引起輸出的無窮大,如果這種輸出無窮大的信號再反饋到功率變換環(huán)節(jié),勢必會造成最后輸出的振蕩,整個系統(tǒng)因而不再穩(wěn)壓。所以說可以通過分析GH的增益和相位來判斷系統(tǒng)的穩(wěn)定性。

又因為當GH= -1時是振蕩的,所以有相移∠GH是180°(因為負反饋本身就有180°的相移),回路增益|GH|=1(0dB)。

所以要使運放穩(wěn)定需要滿足以下條件:1.相位條件就是要其相移要小于180°,即要有45度以上的裕量;2.還要滿足增益條件即要有12dB以上的裕量;3.穿越頻率按20dB/Dec閉合。相關解釋下文給出。

二、Bode圖的基礎:

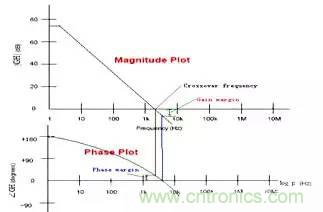

由上文知我們可以通過環(huán)增益GH的頻率特性來判斷系統(tǒng)的穩(wěn)定性,而回路增益|GH|以及回路相位差∠GH的頻率特性可以用Bode圖(見圖2)來表示,并且系統(tǒng)的穩(wěn)定性可以通過Bode圖中的相位裕量(phase margin) ,增益裕量(gain margin),穿越頻率(crossover frequency)來衡量。其中

相位裕量(phase margin)是指:在頻率-相位曲線上,當環(huán)路增益為單位增益時實際相位延遲與360deg 間的差值,以度(deg)為單位表示,見圖2。

增益裕量(gain margin)是指: 在頻率-增益曲線上,當總相位延遲為360deg 時,增益低于單位增益的量,以分貝(dB)為單位來表示,見圖2。

穿越頻率(crossover frequency)也有資料稱之為頻帶寬度等是指:在頻率-增益曲線上,增益為零時所對應的頻率值,見圖2。

Bode plot• Gain margin• Phase margin

相位裕量(phase margin)的作用,是確保在一定的條件下(包括元器件的誤差、輸入電壓變化、負載變化、溫升等)系統(tǒng)都能夠穩(wěn)定,使用在標稱輸入額定負載室溫下,要有45度的裕量;如果輸入電壓、負載、溫度變化范圍非常大, 相位裕量不應小于30度。

增益裕量(gain margin)為了不接近不穩(wěn)定點,一般認為12dB以上是必要的。

穿越頻率(crossover frequency)頻帶寬度的大小可以反映控制環(huán)路響應的快慢。一般認為帶寬越寬,其對負載動態(tài)響應的抑制能力就越好,過沖、欠沖越小,恢復時間也就越快,系統(tǒng)從而可以更穩(wěn)定。但是由于受到右半平面零點的影響,以及原材料、運放的帶寬不可能無窮大等綜合因素的限制,電源的帶寬也不能無限制提高,一般取開關頻率的1/20~1/6。

三、環(huán)路的測試

對環(huán)路的增益和相位的測量,我們可以通??衫妙l率響應分析儀(FRA)或增益-相位分析儀進行測量。這些儀器是通過對采樣獲得的模擬信號進行預處理,然后通過A/D轉換,再利用DFT(離散傅里葉變換)運算求得增益和相位,最后用曲線(Bode plot)表示出來。

本文將以株式會社NF公司的頻率響應分析儀(FRA5087)來做分析,主要按照下邊的接線圖來進行,注意環(huán)節(jié)是注入電阻的位置,以及大小,為了減小測量誤差,實驗一般選取50~100Ω的電阻;有關擾動信號的大小我們可以在測試的過程中通過示波器來讀出,也可以利用FRA的振幅壓縮(Amplitude compression )功能來設置,不過要求擾動的幅度不能超過輸出電壓的5%。否則測出來的結果是不準確的。

FRA測量時注入電阻的位置及接線。

推薦閱讀: