【導(dǎo)讀】本文概述與內(nèi)置基準電壓源、模擬輸出、數(shù)字輸入和時鐘驅(qū)動器的DAC接口電路相關(guān)的一些重要問題。由于ADC也需要基準電壓源和時鐘,因此本文中與這些主題相關(guān)的大多數(shù)概念同樣適用于ADC。

DAC基準電壓

越來越多的人簡單地將DAC視作具有數(shù)字輸入和一個模擬輸出的器件。但模擬輸出取決于 是否存在稱為基準電壓源的模擬輸入,且基準電壓源的精度幾乎始終是DAC絕對精度的限 制因素。在匹配基準電壓源和數(shù)據(jù)轉(zhuǎn)換器時,基準電壓源向?qū)В╒oltage Reference Wizard)等 設(shè)計工具非常有用。如需獲取這些工具及其它,請訪問ADI公司網(wǎng)站的設(shè)計中心(Design Center)部分。

有些ADC和DAC內(nèi)置基準電壓源,而有些則沒有。有些ADC使用電源作為基準電壓源。 不幸的是,與ADC/DAC基準電壓源相關(guān)的標準是少之又少。有些情況下,內(nèi)置基準電壓 源的轉(zhuǎn)換器通??梢酝ㄟ^以更為精密和穩(wěn)定的外部基準電壓源覆蓋或替換內(nèi)部基準電壓源 來提高直流精度。其它情況下,通過使用外部低噪聲基準電壓源,也可以改善高分辨率 ADC的無噪聲碼分辨率。

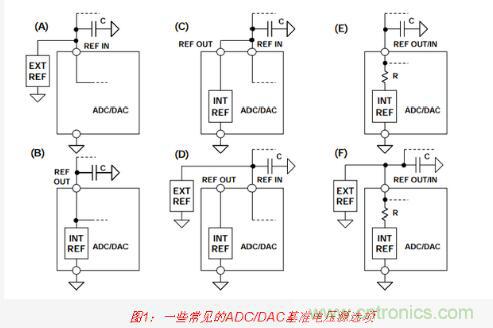

各種各樣的ADC和DAC以各種各樣的方式支持使用外部基準電壓源來替代內(nèi)部基準電壓源。圖1所示為一些常見配置(但顯然并不是全部)。

圖1A所示為需要外部基準電壓源的轉(zhuǎn) 換器。通常建議在ADC/DAC REF IN引腳附近添加合適的去耦電容。基準電壓源數(shù)據(jù)手冊 中通常指定了合適的電容值。另外,基準電壓源在使用必要的容性負載時保持穩(wěn)定是非常 重要的。

圖1B所示為內(nèi)置基準電壓源的轉(zhuǎn)換器,其中基準電壓源也引出到器件上的某個引腳。這 樣,只要負載不超過額定值,就可以在電路中的其它位置上使用該器件。另外,還要在轉(zhuǎn) 換器引腳附近放置電容。如果內(nèi)置基準電壓源可以通過引腳輸出來供外部使用,ADC或 DAC數(shù)據(jù)手冊上通常會指定其精度、穩(wěn)定性和溫度系數(shù)。

如果是要在電路中的其它位置上使用基準輸出,則必須嚴格遵守與扇出和負載相關(guān)的數(shù)據(jù) 手冊規(guī)格。此外,必須小心地進行基準輸出布線,從而最大程度地減少噪聲拾取。很多情 況下,應(yīng)直接在REF OUT引腳處連接合適的運算放大器緩沖器,然后再扇出至電路的各種 其它部分。

圖1C所示為采用內(nèi)部或外部基準電壓源但需要額外封裝引腳的轉(zhuǎn)換器。如果使用的是內(nèi) 部基準電壓源(如圖1C),REF OUT只需外部連接到REF IN并根據(jù)需要進行去耦。

如果使用 的是外部基準電壓源(如圖1D),REF OUT保持懸空,且外部基準電壓源經(jīng)過去耦后施加于 REF IN引腳。這種配置相當(dāng)靈活,可使用相同的基準電壓源來驅(qū)動類似的ADC或DAC, 從而實現(xiàn)器件之間的良好跟蹤性能。

圖1E所示為使用單個封裝引腳以外部基準電壓源來覆蓋驅(qū)動內(nèi)部基準電壓源的配置。電阻 R的值通常為數(shù)kΩ,因此允許通過將低阻抗外部基準電壓源連接到REF OUT/IN引腳來覆 蓋驅(qū)動內(nèi)部基準電壓源。圖1F顯示的是如何連接外部基準電壓源來覆蓋內(nèi)部基準電壓源。

圖1所示的配置并不是ADC和DAC基準電壓源的唯一配置;欲了解有關(guān)選項、扇出和去耦 等的詳細信息,請查閱相關(guān)的數(shù)據(jù)手冊。

雖然基準電壓源元件本身可以是帶隙型、嵌入式齊納型或XFET™型,但實際上所有基準電 壓源都具有某種類型的輸出緩沖器運算放大器。運算放大器將基準電壓源元件與輸出端隔 離開來并還提供驅(qū)動功能。不過,這種運算放大器必須遵守與運算放大器穩(wěn)定性相關(guān)的一 般通則,而這就是基準電壓源去耦話題與本文討論相關(guān)的原因所在。

注意,ADC或DAC的基準電壓輸入與ADC的模擬輸入相似,因為內(nèi)部轉(zhuǎn)換過程可以在該 引腳處注入瞬態(tài)電流。這就要求進行充分去耦來穩(wěn)定基準電壓。添加此類去耦功能可能導(dǎo) 致某些類型的基準電壓源中出現(xiàn)不穩(wěn)定,具體取決于輸出運算放大器設(shè)計。當(dāng)然,基準電 壓源數(shù)據(jù)手冊可能并不會給出輸出運算放大器的任何詳細信息,而這在一定程度上讓設(shè)計 人員陷入兩難境地,擔(dān)心是否能夠保持穩(wěn)定且不會產(chǎn)生瞬態(tài)誤差。很多情況下,ADC或 DAC數(shù)據(jù)手冊將會推薦合適的外部基準電壓源和建議的去耦網(wǎng)絡(luò)。

設(shè)計良好的基準電壓源可以在采用重容性去耦時保持穩(wěn)定。不幸的是,有些基準電壓源并 不能做到這點,并且電容越大,瞬態(tài)響鈴振蕩量實際上會增加。由于轉(zhuǎn)換器幾乎都需要一 定的本地去耦,因此此類基準電壓源在數(shù)據(jù)轉(zhuǎn)換器應(yīng)用中實際上毫無用處。

基準電壓源和數(shù)據(jù)轉(zhuǎn)換器之間可以添加合適的運算放大器緩沖器。不過,有很多品質(zhì)良好 的基準電壓源可以在使用輸出電容時保持穩(wěn)定。數(shù)據(jù)轉(zhuǎn)換器應(yīng)用中應(yīng)當(dāng)選擇這種類型的基 準電壓源,而不是進一步提高運算放大器的復(fù)雜性和成本。

DAC模擬輸出考慮因素

DAC的模擬輸出可能是電壓或電流。兩者情況下,可能都需要知道輸出阻抗。如果對電壓 輸出進行了緩沖,則輸出阻抗將很低。而電流輸出和未緩沖的電壓輸出將存在較高阻抗, 并還可能具有電抗性分量以及純粹的電阻性分量。在有些DAC架構(gòu)的輸出結(jié)構(gòu)中,輸出阻 抗與DAC上的數(shù)字碼字成函數(shù)關(guān)系,這點應(yīng)會在數(shù)據(jù)手冊中明確注明。

理論上,電流輸出應(yīng)當(dāng)連接到電阻為零歐姆的地電位。在實際應(yīng)用中,該輸出將采用非零 阻抗和電壓。“順從性”標題下只是定義了該輸出可耐受的電壓偏差大小,端接電流輸出 DAC時應(yīng)當(dāng)注意到此項技術(shù)規(guī)格。

適合視頻、RF或IF應(yīng)用的大多數(shù)高速DAC具有電流輸出,旨在直接驅(qū)動源和負載端接電 纜。例如,20-mA電流輸出DAC可以在25-Ω負載(相當(dāng)于50-Ω源和負載端接電纜的直流電 阻)上產(chǎn)生0.5 V的電壓。大多數(shù)情況下,單電源高速CMOS DAC具有至少+1 V的正輸出順 從電壓和數(shù)百毫伏的負輸出順從電壓。

很多情況下(如TxDAC®系列),同時支持真正電流輸出和互補電流輸出。差分輸出可以直 接驅(qū)動變壓器的初級繞組,并且通過將輸出繞組的一側(cè)接地,可以在次級繞組處產(chǎn)生單端 信號。與簡單地從DAC電流輸出之一直接獲取輸出信號并將其它輸出接地相比,這種方法 通??梢栽诟哳l率下獲得更佳失真性能。

現(xiàn)代電流輸出DAC通常具有數(shù)個差分輸出,以便實現(xiàn)高共模抑制并減少偶數(shù)階失真產(chǎn)物。 常見的滿量程輸出電壓范圍為2 mA至30 mA。

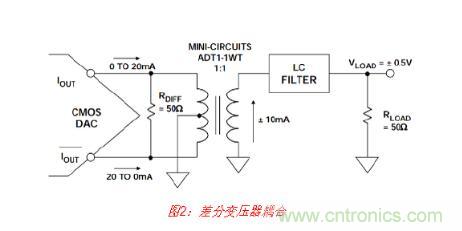

在許多應(yīng)用中,需要將DAC的差分輸出轉(zhuǎn)換成適合驅(qū)動同軸線路的單端信號。只要無需低 頻響應(yīng),那么通過RF變壓器便可輕松地實現(xiàn)這點。圖2所示為這種方法的典型示例。DAC 的高阻抗電流輸出與50 Ω電阻差分端接,從而將變壓器的源阻抗定義為50 Ω。

所得到的差分電壓驅(qū)動1:1 RF變壓器的初級繞組,從而在次級繞組的輸出端產(chǎn)生單端電 壓。50 Ω LC濾波器的輸出與50 Ω負載電阻RL相匹配,進而最終產(chǎn)生1 Vp-p的輸出電壓。

變壓器不僅用于將差分輸出轉(zhuǎn)換成單端信號,而且還將DAC的輸出與LC濾波器的抗性負 載隔離開來,因而可以改善整體失真性能。

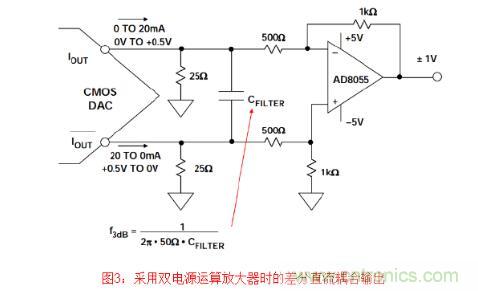

需要低至DC的頻率響應(yīng)時,可以連接運算放大器作為差分轉(zhuǎn)單端轉(zhuǎn)換器來獲取單端輸 出。 在圖3中,運算放大器AD8055用于實現(xiàn)高帶寬和低失真。電流輸出DAC驅(qū)動平衡的 25 Ω阻性負載,從而在各輸出端產(chǎn)生0至+0.5 V的錯相電壓。這項技術(shù)用于代替直接I/V轉(zhuǎn) 換,從而防止高壓擺率DAC電流導(dǎo)致放大器過載和引入失真。必須小心地處理使DAC輸 出電壓位于其順從電壓額定值范圍之內(nèi)。

AD8055的增益配置為2,以最終產(chǎn)生2 V p-p且以地電壓為基準的單端輸出電壓。注意,由 于輸出信號擺幅高于/低于地,因此需要采用雙電源運算放大器。

CFILTER電容構(gòu)成具有50 Ω等效差分輸出阻抗的差分濾波器。此濾波器可減少運算放大器的 任何壓擺率型失真,而該濾波器的最佳截止頻率是憑經(jīng)驗來確定的,旨在獲得最佳整體失 真性能。

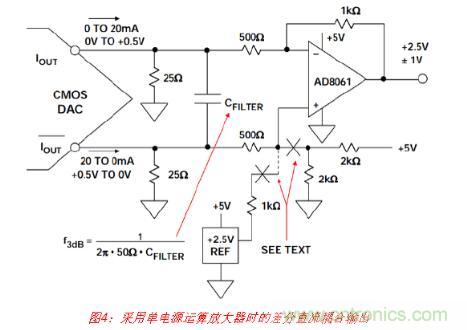

只要運算放大器的共模電壓設(shè)為中間電源電壓(+2.5 V),則圖3中的電路經(jīng)過改良后可以采 用單電源供電。具體如圖4所示,其中使用的是運算放大器AD8061。輸出電壓為2 Vp-p且 以共模電壓+2.5 V為中心。此共模電壓可以使用電阻分壓器從+5 V電源產(chǎn)生,或直接從 +2.5 V基準電壓源產(chǎn)生。如果使用+5 V電源來提供共模電壓,則必須進行深度去耦,以免 放大電源噪聲。

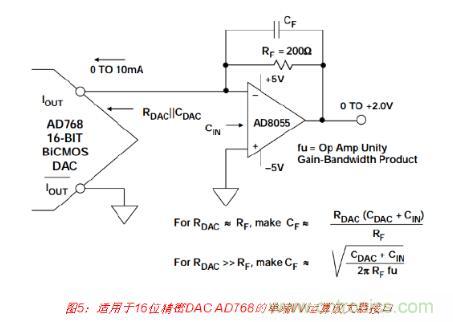

單端電流電壓轉(zhuǎn)換

通過使用單個運算放大器作為I/V轉(zhuǎn)換器,便可輕松執(zhí)行單端電流電壓轉(zhuǎn)換,如圖5所 示。AD768的10 mA滿量程DAC電流輸出可以在200 Ω RF電阻上產(chǎn)生0至+2 V的輸出電 壓。

通過驅(qū)動AD8055運算放大器的虛擬地,可以最大程度地減少因DAC輸出阻抗中的非線性 而導(dǎo)致的任何失真。實際上,這種類型的DAC大多數(shù)都使用I/V轉(zhuǎn)換器進行過工廠調(diào)整。

但是應(yīng)注意,與差分工作模式相比,以這種方式使用DAC的單端輸出時,共模抑制性能將 下降,且2階失真產(chǎn)物將增加。

CF反饋電容應(yīng)當(dāng)進行優(yōu)化,以在電路中實現(xiàn)最佳脈沖響應(yīng)。圖中給出的等式僅供參考。

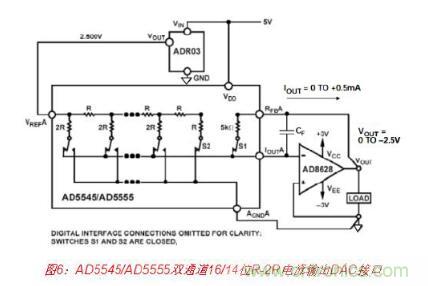

基于R-2R的電流輸出DAC的輸出阻抗與碼字有關(guān),因此其輸出必須驅(qū)動運算放大器的虛 擬地,以便維持線性。16/14位DAC AD5545/AD5555都是此種架構(gòu)的很好范例。圖6所示為 一種合適的接口電路,其中ADR03用作2.5 V基準電壓源,而AD8628斬波穩(wěn)定運算放大器 用作輸出I/V轉(zhuǎn)換器。

外部2.5 V基準電壓源決定滿量程輸出電流0.5 mA。注意,5 kΩ反饋電阻包含在DAC內(nèi),且 無需外部電阻,即可增加溫度穩(wěn)定性。因此,運算放大器的滿量程輸出電壓為–2.5 V。CF 反饋電容補償DAC輸出阻抗,因此應(yīng)當(dāng)選擇來優(yōu)化脈沖響應(yīng),起點通常為20 pF。

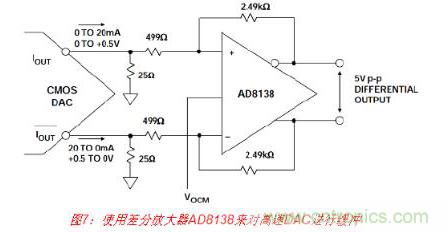

差分電流轉(zhuǎn)差分電壓轉(zhuǎn)換

如果要求從電流輸出DAC獲得緩沖差分電壓輸出,則可以使用AD813x系列差分放大器, 如圖7所示。

DAC輸出電流首先流過25 Ω電阻而轉(zhuǎn)換成電壓。接著,使用AD8138將電壓放大5倍。這 項技術(shù)用于代替直接I/V轉(zhuǎn)換,從而防止高壓擺率DAC電流導(dǎo)致放大器過載和引入失真。 必須小心地處理使DAC輸出電壓位于其順從電壓額定值范圍之內(nèi)。

AD8138的VOCM輸入可用于設(shè)置AD8138規(guī)格范圍內(nèi)的最終輸出共模電壓。通過添加一 對75 Ω串聯(lián)輸出電阻,將允許驅(qū)動傳輸線路。

DAC數(shù)據(jù)輸入考慮因素

最早的單芯片DAC幾乎不包含邏輯電路,且數(shù)字輸入必須維持并行數(shù)據(jù),才能維持數(shù)字 輸出。而今,幾乎所有DAC都會被鎖存,且只需向其中寫入數(shù)據(jù),而不用去維持。有些 器件甚至具有非易失性鎖存器并可在關(guān)斷時記住設(shè)置。

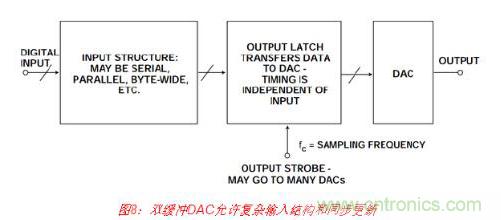

DAC輸入結(jié)構(gòu)存在無數(shù)變化形式,本文將不一一介紹,但幾乎所有都稱為“雙緩沖”。栓 緩沖DAC具有兩組鎖存器。數(shù)據(jù)最初鎖存在第一級中,然后傳輸?shù)降诙?,如圖8所示。 這種配置非常有用,具體有以下幾種原因。

首先,其允許以多種不同方式將數(shù)據(jù)輸入DAC。如果DAC沒有鎖存器或具有一個鎖存 器,則必須以并行方式同時加載所有位,否則其加載期間的輸出可能會與其實際內(nèi)容或 目標內(nèi)容完全不同。然而,雙緩沖DAC可以加載并行數(shù)據(jù)、串行數(shù)據(jù)、4位或8位字或任 何其它內(nèi)容,并且在新數(shù)據(jù)加載完成且DAC收到更新指令之前,輸出不會受到影響。

雙緩沖DAC的另一項優(yōu)勢在于,通過以并行方式驅(qū)動所有開關(guān)并以DAC輸出數(shù)據(jù)速率更 新單個鎖存器,可以最大程度地減少各個開關(guān)之間的時間偏斜。這樣可以最大程度地減 少毛刺脈沖并改善失真性能。

雙緩沖結(jié)構(gòu)的第三項優(yōu)勢是可以同步更新多個DAC。數(shù)據(jù)依次載入各DAC的第一級,當(dāng) 一切就緒之后,即會同時更新所有DAC的輸出緩沖器。在許多DAC應(yīng)用中,數(shù)個DAC的 輸出必須同時變化,而通過雙緩沖結(jié)構(gòu)可以非常輕松地實現(xiàn)這點。

早期的單芯片高分辨率DAC大多數(shù)具有并行或字節(jié)寬數(shù)據(jù)端口,并且往往連接到并行數(shù) 據(jù)總線和地址解碼器,然后作為極小的只寫存儲器由微控制器進行尋址。(有些并行DAC 并不是只能寫入內(nèi)容,而且還可以進行讀?。贿@點對于一些應(yīng)用來說非常方便,但并不 是非常常見。)DAC連接到數(shù)據(jù)總線時,總線的邏輯噪聲容易容性耦合到模擬輸出,因此 而今許多DAC采用串行數(shù)據(jù)結(jié)構(gòu)。這類結(jié)構(gòu)更不容易受到上述噪聲的影響(因為涉及到的 噪聲引腳更少)且使用的引腳更少,因此占用的電路板空間也更少;在與現(xiàn)代微控制器(大 多數(shù)具有串行數(shù)據(jù)端口)搭配使用時,這類結(jié)構(gòu)通常更為方便。此類串行DAC有些(但并 非全部)具有數(shù)據(jù)輸出和數(shù)據(jù)輸入,因此數(shù)個DAC可以串聯(lián)連接,而數(shù)據(jù)則通過單個數(shù)據(jù) 端口逐個輸入所有這些器件。這種配置通常稱為“菊花鏈”。

串行DAC支持語音頻帶和語音頻率更新速率。例如,以192 kSPS速率更新的24位數(shù)字音頻 要求串行端口傳輸速率至少達到24 &TImes; 192 kSPS = 46.08 MSPS,而CMOS邏輯可以輕松處理 該速率。不過,涉及到更新速率時,由于所需的串行數(shù)據(jù)傳輸速率過高,因此必須采用 并行DAC。

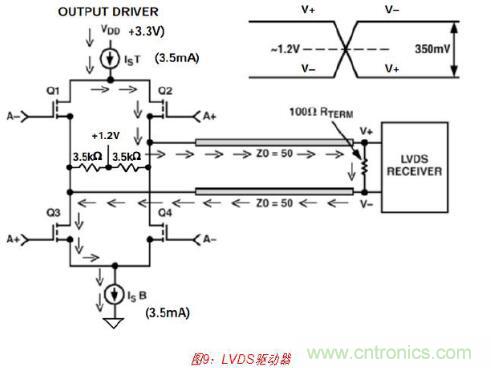

當(dāng)并行數(shù)據(jù)速率超過約100 MSPS時,由于不太可能會產(chǎn)生CMOS邏輯電平以上的瞬變干 擾,因此通常使用低電平電流模式差分邏輯(PECL、較低級別的PECL或LVDS等)(見圖 9)。這樣可幫助最大程度地減少因碼相關(guān)毛刺而產(chǎn)生的失真。例如,AD9734/AD9735/ AD9736 DAC系列采用1.2 GSPS并接受LVDS輸入邏輯電平。片上包含特殊電路,以確保 輸入數(shù)據(jù)相對于DAC時鐘具有正確時序

DAC時鐘考慮因素

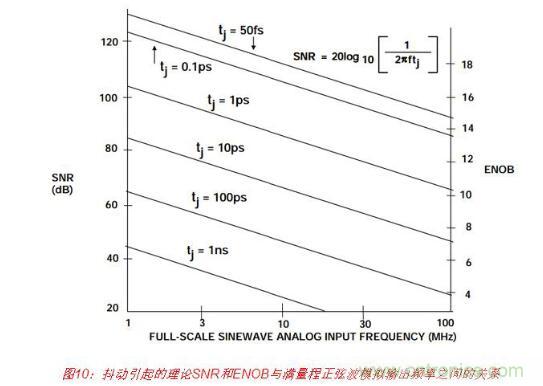

ADC寬帶孔徑抖動tj、轉(zhuǎn)換器SNR和滿量程正弦波模擬輸入頻率 f之間的關(guān)系如下:

這種關(guān)系同樣適用于重構(gòu)DAC。該等式假定使用的是理想ADC/DAC,其中唯一誤差源是 時鐘抖動。SNR測量的帶寬為奈奎斯特帶寬DC至f c /2,其中f c 是DAC更新速率。注意,等 式1還假定采用的是滿量程正弦波輸出。因抖動而產(chǎn)生的誤差與輸出信號的壓擺率成比 例,即正弦波幅度越小且壓擺率相應(yīng)越小,所產(chǎn)生的SNR值就越大(相對于滿量程)。

應(yīng)注意,等式1中的t j 是采樣時鐘抖動t jc和ADC內(nèi)部孔徑抖動t ja兩者相加;這兩個術(shù)語并不 相關(guān),因此是在方和根(rss)基礎(chǔ)上相加的:

另一方面,高速重構(gòu)DAC并未內(nèi)置采樣保持放大器,因此沒有內(nèi)部孔徑抖動規(guī)格。雖然 DAC存在內(nèi)部時鐘抖動分量,但由于主要抖動源是外部時鐘抖動, 通常并不測量或指定 該分量。

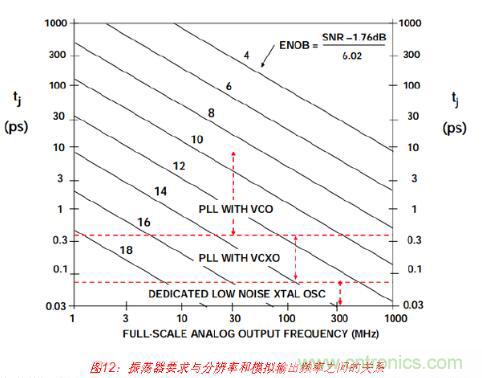

圖10繪制出了等式1的曲線圖并以圖形形式顯示了各種滿量程模擬輸出頻率抖動如何導(dǎo)致 SNR下降(注意,此處假定tj包含所有抖動源,包括內(nèi)部DAC抖動)。例如,如果70 MHz IF 輸出頻率需要維持12位SNR (74 dB),時鐘抖動必須小于0.45 ps(見等式1)。

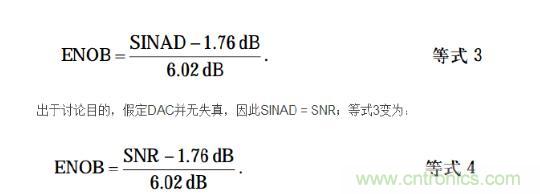

有效位數(shù)(ENOB)和信納比(SINAD)之間存在非常有用的關(guān)系, 具體如下:

圖10左側(cè)垂直軸上的SNR值已經(jīng)使用等式4轉(zhuǎn)換成右側(cè)垂直軸上的ENOB值。

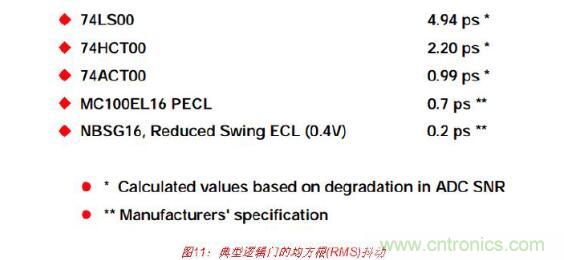

為了顯示這些抖動值的重要性,請考慮與一組邏輯門相關(guān)的均方根(RMS)抖動典型值,如 圖11所示。74LS00、74HCT00和74ACT00的值都是采用參考文獻1第5章所述的方法以高 性能ADC(孔徑抖動小于0.2-ps rms)測得的,其中抖動是從因多個相同門串聯(lián)而導(dǎo)致的FFT SNR降低計算得出的。然后,通過除以串聯(lián)門總數(shù)的平方根,便可計算出單個門所造成 的抖動。制造商給出了MC100EL16和NBSG16的抖動數(shù)據(jù)。

圖12顯示的是與圖10相同的數(shù)據(jù),但其中針對各種分辨率要求繪制出與模擬輸出頻率成 函數(shù)關(guān)系的最大允許抖動。根據(jù)最大輸出頻率和ENOB中所需分辨率來選擇采樣時鐘發(fā)生 器類型,應(yīng)以此圖片作為大概準則。具有標準VCO的PLL方法就是產(chǎn)生采樣時鐘的一種 不錯方式,其中均方根(RMS)抖動要求大約為1 ps或以上。不過,亞皮秒抖動要求采用基 于VCXO的PLL或?qū)S玫驮肼暰w振蕩器。“教程MT-008”介紹了如何將振蕩器相位噪聲轉(zhuǎn) 換成抖動。

這部分介紹了假設(shè)抖動僅由內(nèi)部DAC抖動和外部時鐘抖動組成時SNR上的抖動效應(yīng)。不 過,無論DAC或采樣時鐘振蕩器的規(guī)格如何,不當(dāng)?shù)牟季?、接地和去耦技術(shù)可造成額外 的時鐘抖動,進而顯著降低動態(tài)性能。

若將采樣時鐘信號與具有噪聲的數(shù)字信號并行布線,肯定會因雜散耦合而導(dǎo)致性能下 降。實際上,若將來自并行輸出ADC的高速數(shù)據(jù)耦合到采樣時鐘,不僅會導(dǎo)致噪聲增 加,而且還可能造成額外的諧波失真,因為數(shù)字輸出瞬態(tài)電流包含的能量與信號有關(guān)。