【導讀】對信號完整性工程師而言,高速串行鏈路仿真是功能強大的工具。這些仿真可讓設計人員大致了解系統(tǒng)性能預測,使他們在將設計交付耗資巨大的電路板生產(chǎn)之前更容易做出正確決定以達到設計目標。

TI的WEBENCH®接口設計工具可為串行鏈路仿真提供簡單卻功能強大的環(huán)境。這款基于Web的免費工具可作為快速且方便使用的高速通道分析仿真工具 —— 對傳統(tǒng)上由已獲授權(quán)的電子設計自動化(EDA)軟件工具進行的分析(更嚴格更耗時)是一種補充。您可在這篇博客文章里讀到更多關于WEBENCH接口設計工具的內(nèi)容。

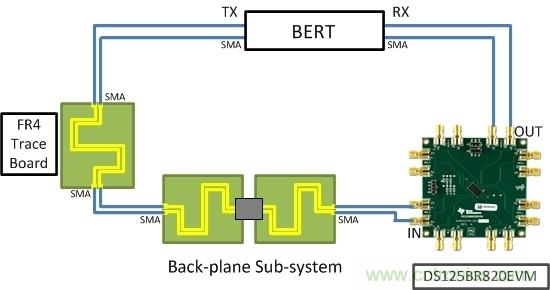

這一切聽起來很棒,但該工具能給您帶來可靠的結(jié)果嗎?為了回答這個問題,筆者去了實驗室,并進行了一些測量。筆者決定使用一個速率為12.5Gbps的Linear re-driver DS125BR820EVM、一些FR4印刷電路板(PCB)走線以及具有SMA連接器、適用于背板子系統(tǒng)的子卡。圖1展示了筆者的簡單設置。使用一個誤碼率測試器(BERT)作為為本次研究的發(fā)送器及接收器)。

圖1:實驗室測量設置

首先,筆者用一個四端口網(wǎng)絡分析儀測定了所有線纜、連接器和電路板走線的S參數(shù)并保存它們,目的是用來建立通道模型。接著筆者對這些文件進行級聯(lián),旨在為前置通道(芯片輸入之前的所有通道)和后置通道(芯片輸出后面的所有通道)創(chuàng)建組合式模型,以便上傳到WEBENCH接口設計工具。因為可從該工具訪問DS125BR820 IBIS-AMI(input/output buffer information specification-algorithmic modeling interface)模型,所以最后要做的一件事是設置發(fā)送器。筆者使用一個通用的IBIS-AMI發(fā)送器模型,并將邊緣速率和差分輸出電壓匹配得盡量接近BERT。由于筆者的WEBENCH環(huán)境復制了實驗室的試驗臺,因此筆者可為幾種不同的設置運行仿真,并觀察它們的匹配狀況如何。WEBENCH接口設計工具的另一個妙處是它能遠程處理仿真,這樣筆者就可以在實驗室通過自己的筆記本電腦運行它們,無需擔心處理能力。

在本次研究中用了兩個實例。實例1是在8Gbps的數(shù)據(jù)速率下使用了PCI Express Gen3。實例2是在12Gbps的數(shù)據(jù)速率下使用了SAS3。

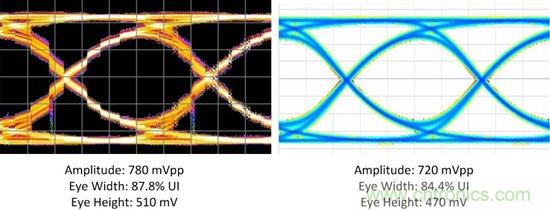

實例 1 的技術(shù)參數(shù)為:

BERT輸出:8Gbps、800mVpp。

通道:在4GHz的前置通道處為?10dB,在4GHz的后置通道處為?2dB。

DS125BR820設置:輸入EQ = Level 3、輸出VOD = Level 5。

圖2:實例1的實驗室數(shù)據(jù)(左)和WEBENCH接口設計工具仿真數(shù)據(jù)(右)

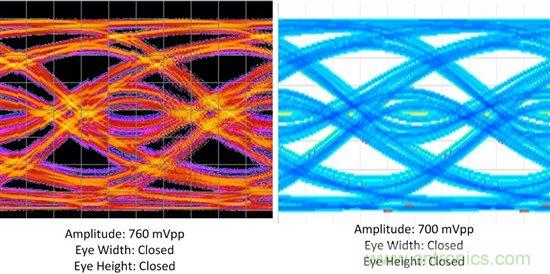

實例 2 的技術(shù)參數(shù)為:

BERT輸出:12Gbps、800mVpp。

通道:在6GHz的前置通道處為?14dB,在6GHz的后置通道處為?3dB。

DS125BR820設置:輸入EQ = Level4、輸出VOD = Level 7。

圖3:實例2的實驗室數(shù)據(jù)(左)和WEBENCH接口設計工具仿真數(shù)據(jù)(右)

DS125BR820在筆者的系統(tǒng)輸出端打開了眼圖。圖2所示的實例1表明有足夠的余量,看來DS125BR820能補償更多的通道損耗同時使眼圖仍能保持開啟狀態(tài)。圖3所示的實例2展示了相反的情況:筆者的通道有太多的損耗,在這些運行條件下筆者很可能會看到誤碼,除非在通道的末端使用接收芯片的均衡功能。

如果您未能如筆者一樣擁有可上傳的S參數(shù)測量值,那么您可以簡單地輸入在給定頻率下的預期損耗;WEBENCH接口設計工具將產(chǎn)生與您所需插入損耗相匹配的通用S參數(shù)。

設置和運行像這樣的仿真大約需要30分鐘,產(chǎn)生的結(jié)果比實驗室測量值更合理且匹配更好。WEBENCH接口設計工具是一種非常有用、基于Web的工具,能幫用戶根據(jù)自己的應用需求挑選合適的器件。筆者希望您試用一下它!

推薦閱讀:

推薦閱讀: